目录

小数分频

双模预分频器可以被变成为两个分频比。分频比可以在P和P+1之间来回切换,以此来实现小数分频。控制该分频比的控制信号Cout,是使用大小为F(或者log2F位)的累加器/具有反馈的分频器/加法器/计数器生成。当加法器输出≥F时,就会发生溢出。在第i个上升沿,累加器输出:

其中yi−1为上一个上升时钟沿的输出,Ki为用户自定义的输入,Ki的值将决定分数分频器的值。

实例:

模块化运算(A mod B)返回(A÷B)的余数,这是对累加器溢出建模所必需的。

描述输入K = 1, K = 3的3位累加器的操作,假设累加器种子值(即初始累加器输出值)为零。

对于K = 1的情况,在每8个时钟周期内,Cout在1个周期内为高电平,在7个周期内为低电平,因此Cout的频率为fclk /8。对于K = 3的情况,Cout为3个周期高,在每8个时钟周期内5个周期为低,因此Cout的频率为3fclk /8。

F:在F个参考时钟周期内观察Cout,位数为log2F。

K:Cout在F个周期内,有K个周期为高电平,所以Cout频率为K*fclk/F。

如果双模预分频器在Cout低时除以P,在Cout高时除以P + 1,则VCO的平均输出频率为:

括号里面的就是小数分频比,一般P和F都是固定的,所以可编程的唯一参数就是K,K的范围是1~F。由于K是整数,所以该架构的步长为:

R通常是固定的,以避免改变输入端的比较频率。请注意,R通常尽可能小,以最小化晶体的带内相位噪声贡献。因此,步长与比特数(log2f)成反比;因此,累加器通常用于减小合成器步长而不增加R和降低带内相位噪声。

可编程累加器

有时可能需要步长可编程,所以需要F可编程。下图,累加器大小为G,可编程范围:1-F

累加器的位数是n = log2 (F)。

在Verilog二进制格式中,最大累加器值为F={n{1'b0}},这是n个串联的零。一般来说,在模F算术中,0和F是等价的。例如,3位累加器的最大值F=8,用二进制000表示。可以存储在累加器中的最大数字是F−1,即111。当累加器值≥F,产生进位位。与没有大小可编程性的简单累加器相比,上述累加器具有进位Cin。Cin将F−G添加到累加器。因此,累加器将始终以值F−G开始。如果输入为K=1,则累加器需要G个时钟周期才能达到溢出点F(F−G+G=F),这相当于具有大小为G的累加器。

通俗易懂点讲:当累加器的数值增加到最大值时,它就会重新从最小值开始计数。假设你有一个可以从1数到8的累加器(即F = 8)。当它数到8时,如果再加1,会发生什么呢?在这个情况下,我们想让它重新从1开始数,而不是继续数到9或更高。为了实现这一点,我们需要一种方法,当累加器数值到达最大值时,它会自动重置回到最小值。这段话中提到的方法就是为了实现这个目的。它会在累加器数值达到最大值时,向累加器输入一个特殊的值,这个值会使累加器从最大值重新开始计数。

具体地说,当累加器的输出值接近最大值时,会检测是否需要产生一个溢出(carry-out)信号。如果累加器的输出值达到了最大值,那么产生溢出信号。在这种情况下,会向累加器输入一个特殊的值,该值的目的是让累加器从最小值重新开始计数。这个特殊的值是通过 F 和 G 计算得到的,表示从最大值到最小值的差。通过将这个值加到累加器中,我们可以确保在下一个时钟周期中,累加器从最小值重新开始计数。G 和 F 分别表示累加器的大小和最大值。

由于模F运算中的F=0,因此F−G=−G。−G通过取G的两个补码来获得,也就是说,将G的所有位反相,然后将结果加1。为了避免二者的补码运算相加,合成器的输入可以是G′=G−1,而不是G。因此,F−G=−G可以简单地通过反转输入G′的所有位来获得。这个运算将得到G′的一个补码。

多模分频器的小数分频器

用MMD代替双模分频器,更通用的形式如图所示。使用MMD的优点是,合成器可以调谐的频率范围得到了扩展。合成器输出频率:

其中I是循环除数的整数部分。例如,如果需要一个100.25的循环分割比,我们可以编程I = 100, K = 1, F = 4。MMD分割比率在100和101之间切换。在n位模数控制信号下,MMD分频比由式给出

MMD编程范围为2^(n) ~ 2^(n + 1)−1。例如,一个6位的MMD可以从64位编程到127位。

缺点:

由于周期性地切换环路分频比而产生的杂散分量。回想一下,在时间域中的任何重复模式都会在频率域中产生杂散。分数累加器周期性地生成使环路分频比切换的进位输出。预计应该在进位输出频率的倍数处产生杂散音调。

实例:设计一个分数n合成器架构,用于合成从819.2 MHz到820.96 MHz的11个通道,步长为160 kHz,并与参考频率fr/R = 5.12 MHz进行比较。确定分数n杂散分量的频率。

答:由步长公式 ,求出F=32,可以用5位加法器实现。累加器输入可以从编程为0-10覆盖819.2 MHz到820.96 MHz的11个通道。步长为160 kHz,求出整除分频比的值:

,求出F=32,可以用5位加法器实现。累加器输入可以从编程为0-10覆盖819.2 MHz到820.96 MHz的11个通道。步长为160 kHz,求出整除分频比的值:

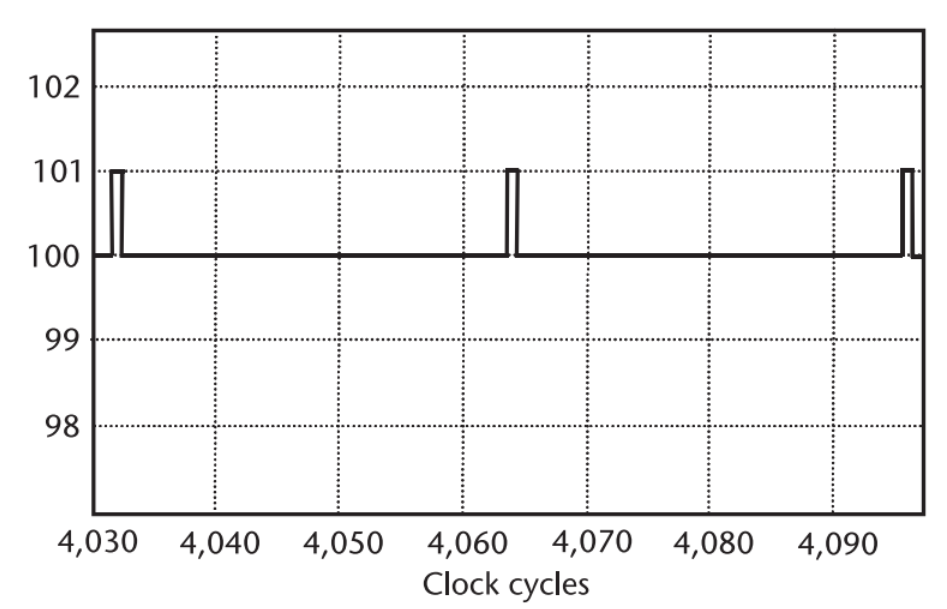

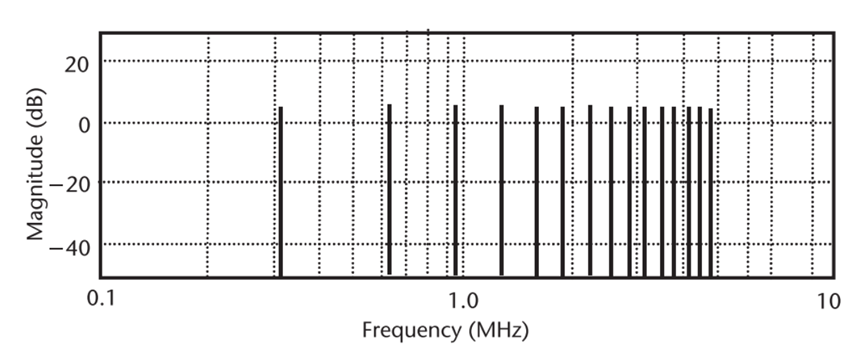

,得到I = 160,循环总除数(上式括号里面的项)为N = 160 + K/32,其中K = 0,1,…。10. 如果使用带有MMD的小数分频架构,则需要可编程范围为128到255的7位MMD。循环除数在160和161之间切换。模量控制由累加器执行产生,其频率为(fr/R)*(K/F)。因此,对于K个参考周期,环路被除以160,对于F−K个周期,环路被除以161,其结果是平均分割比为160 + K/F。以K = 1, F = 32的第二个通道为例,模拟分数阶累加器输出如图所示,分数阶累加器每32个比较周期输出一次执行,这迫使分法器在31个周期内除以160,在1个周期内除以161。除以161的周期相位校正脉冲产生均匀间隔为fr/R/32 = 160 kHz的分数型杂散,如图 (b)所示。

,得到I = 160,循环总除数(上式括号里面的项)为N = 160 + K/32,其中K = 0,1,…。10. 如果使用带有MMD的小数分频架构,则需要可编程范围为128到255的7位MMD。循环除数在160和161之间切换。模量控制由累加器执行产生,其频率为(fr/R)*(K/F)。因此,对于K个参考周期,环路被除以160,对于F−K个周期,环路被除以161,其结果是平均分割比为160 + K/F。以K = 1, F = 32的第二个通道为例,模拟分数阶累加器输出如图所示,分数阶累加器每32个比较周期输出一次执行,这迫使分法器在31个周期内除以160,在1个周期内除以161。除以161的周期相位校正脉冲产生均匀间隔为fr/R/32 = 160 kHz的分数型杂散,如图 (b)所示。

杂散将出现在合成器的输出频谱中。分数杂散在160 kHz的整数倍。随着频率的增加,杂散幅度的滚降是由于环路低通滚降特性。

小数合成器实现了小步长和低带内相位噪声,同时补偿了由分频比周期性变化引起的杂散。如果最近的杂散在锁相环带宽之外,则可以通过使用高阶环路传递函数来去除分数杂散。注意,离载波最近的杂散的间距由合成器步长决定。对于步长小于传递函数带宽的合成器,使用环路LPF实际上是不可能去除分数杂散的。减少环路带宽来对抗分数杂散意味着你必须付出更长的锁定时间和由于VCO而增加的带外相位噪声的代价。即使最近的杂散在环路滤波器带宽之外,消除这些杂散通常需要一个具有急剧滚降的高阶环路滤波器,这增加了合成器的复杂性和成本。为了去除具有精细步长的合成器的分数阶杂散分量,最佳解决方案是在分数阶累加器中使用SD噪声整形器。它们的作用是在不影响平均除数比的情况下,分解循环除数时间序列的重复模式。这将导致频谱中杂散的减少或消除。

Sigma-delta调制器

SD调制器可用于控制环路分频器,使小数杂散可以随机化并转移到更高的频带,在高频可以很容易地被环路LPF去除。

基本概念

量化噪声和过采样效应

量化器将模拟信号转化成数字信号,X为模拟输入,Y为量化后的数字输出。输出等间隔∆(直线的斜率)。

所以,除非输入恰好是量化器分辨率(步长) ∆![]() 的整数倍,否则存在量化误差e。量化误差范围为:

的整数倍,否则存在量化误差e。量化误差范围为:

下图为误差电压波形图,为锯齿状,如果输入本质上是随机的,那么瞬时误差也是随机的。从样本到样本的误差是不相关的,因此可以被视为噪声。

量化噪声建模:

随机信号的量化噪声可以被视为值在−∆/2到∆/2范围内任意位置的加性白噪声。量化噪声的概率密度为下式,需要1/∆的归一化因子来保证密度的总积分=1。

对误差电压的平方进行积分,除以量化步长,得到误差电压的均方根(量化噪声的均方根):

采样系统的频谱每个采样频率重复一次,因此,量化噪声频谱以dc为中心,向外扩散到采样频率的fs/2的一半,并且在fs/2和3fs/2之间重复,考虑到所有的噪声功率都在正频带范围之内 (即0≤f≤∞),因此量化噪声功率折叠到dc到fs /2的频带。假设白噪声,量化噪声的功率谱密度由式给出

其中,样本周期T = 1/fs。对于带宽为f0的限带信号0≤f < f0,则落在该信号频带的量化噪声功率为

其中,过采样比(OSR)定义为采样频率fs与奈奎斯特频率2f0之比

在N位采样系统中,如果量化器有2^N个等间隔为∆![]() 的量化电平,则最大峰对峰幅度为

的量化电平,则最大峰对峰幅度为

如果信号是正弦的,则相关的信号功率为

因此,落在信号频带的量化噪声功率的信噪比为

log10 (x) = log10(2)*Log2 (x),上面的表达式变成

因此,量化器每增加1bit,信噪比就提高6 dB。在总量化噪声功率相同的情况下,采样频率每增加一倍,带内量化噪声降低3db。如图所示,过采样降低了带内均方根量化噪声,因为总噪声分布在整个采样带宽上。因此,就量化噪声而言,将过采样比增加一倍相当于将量化器增加0.5bit。

过采样允许在不牺牲噪声性能的情况下使用低分辨率转换器。

另一种观察方法是,将采样率加倍,我们现在有两个相关的采样信号;因此,信号功率增加了6db。但是,两个噪声采样只会使噪声功率增加一倍,因此噪声功率仅增加3 dB。换句话说,采样信号是相关的;噪声样本不是。(有点啰嗦,我简单描述一下:信号叠加的时候是幅度相加,噪声叠加的时候是功率相加,所以信号叠加:幅度从A变成2A,功率从A^2变成(2A)^2=4A^2,对应增加6dB。噪声叠加:不能加幅度,只能加功率,功率从P变成2P,对应3dB。)因此,信噪比提高了3db,对应于0.5bit分辨率的提高。过采样优点是它简化了对A/D转换器的模拟抗混叠滤波器或D/A转换器的去glitch滤波器的要求,因为过采样导致宽过渡带;因此,只需要低阶过滤器。然而,更高的采样率意味着数字电路必须运行得更快,这就消耗了更多的电力。这也意味着信号带宽必须远低于采样率,这限制了转换速率。

噪声整形

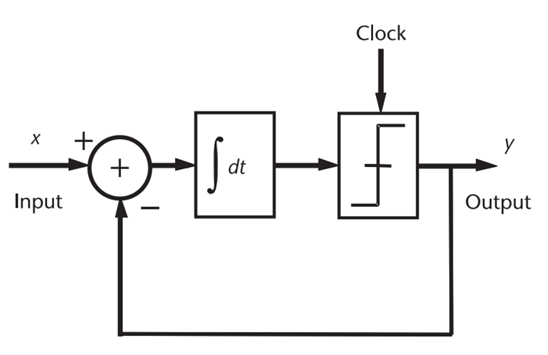

虽然过采样可以通过在更宽的采样带宽上平均随机量化噪声来减少随机量化噪声,但另一种有用的量化降噪方案是使用反馈进行噪声整形。如图所示。量化器的加性噪声模型遵循传递函数为H(s)的滤波器。然后,加入负反馈以稳定系统。

|H(s)|>>1时(如只考虑低频时),简化:

因此,信号传递函数在低频是统一的。噪声传递函数(NTF):

所以,如果H(s)低频具有高增益,则可以在低频时降低输出量化噪声。

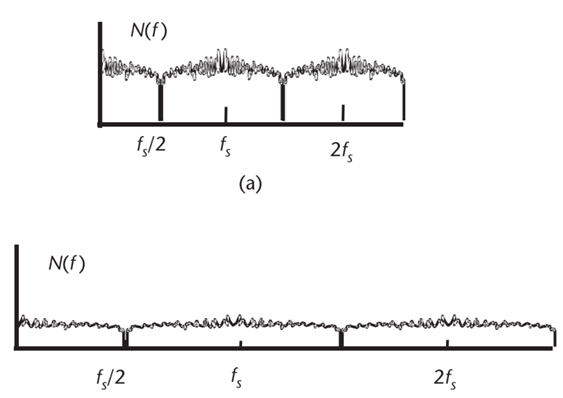

最麻烦的噪声是近距离量化噪声,因为使用LPF很难去除。在无噪声整形反馈的开环过采样系统中,如图所示,量化噪声为均匀分布于0≤f≤fs /2的白噪声,噪声功率密度为∆^2 /6fs。

在具有H(s)的低通传递函数的反馈过采样系统中,带内量化噪声的形状如图所示。合成噪声传递函数为1/[1 + H(s)],具有高通效应。因此,量化噪声由反馈回路高通整形,从而导致较低的带内噪声。注意,具有反馈和不具有反馈的两个系统的总量化噪声能量是相同的。两图阴影面积均为∆^2/12。唯一的区别是具有反馈的量化噪声被转移到更高的频带,在那里它可以被容易地滤波。

过采样和噪声整形是两个相关的技术。过采样是指超过奈奎斯特速率的采样。噪声整形是指对噪声频谱进行整形,使噪声在信号频带内降低,在信号频带外增大,使噪声易于去除。特别是,频率合成中的噪声整形采用SD调制器形成高通滤波器,使得杂散和噪声可以转移到更高的频带,在那里它们可以很容易地通过低通环路滤波器去除。当噪声整形与过采样结合使用时是最有用的。SD调制通过使用反馈系统大大增强了过采样效果。采用SD调制的过采样系统通常被称为高阶过采样系统,因为传统的不采用SD调制的过采样系统实际上是一个零阶反馈系统。

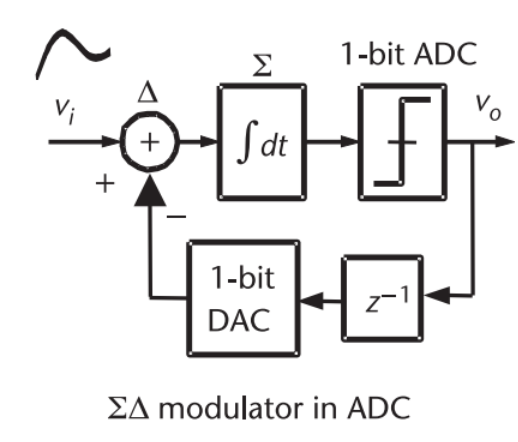

SD调制器概述

为了介绍SD转换器的概念,让我们从sigma调制器开始,如图所示,其中量化器采样的误差信号是输入信号和反馈信号之间的差或增量。反馈信号是输出的积分。因此,如果Vx<X,则y变高,使vx向x靠拢。

由于sigma调制器不会形成量化噪声,因此可以将积分器移到差分块之后的前向路径中。这种配置称为SD调制器。误差信号首先被积分,通过量化器反馈到输入。由于积分器在低频时具有高增益,因此在低频时误差电压较小。低频时的小误差意味着输出比特流的低频分量等于输入信号。因此,可以使用低通滤波器或积分器恢复低频分量。通常,输出脉冲密度代表输入电压(即该波形的低频部分跟随输入信号)。

SD调制器有时被称为DS调制器。S指的是积分,D指的是比较。由于时钟的运行速率远远高于输入信号速率,因此该系统是一个过采样系统。

一阶SD调制器

一阶SD调制器如上图所示。与没有反馈的简单量化器相比,它是一种更有效的过采样a/D转换器。假设调制器包含具有单位增益的多级均匀量化器来。积分器对馈送到量化器输入端的信号进行平均。量化输出y被反馈并从输入x中减去。因此,反馈迫使量化输出信号的平均值跟踪平均输入。

等效电路,其中量化器表示为时间步长i处的加性量化误差ei,增益∆设为1。因为这是一个采样数据电路,所以使用累加器来表示积分。累加器的输出为:

Z^(−1)是一个单位延迟,

SD调制器的输出:

联立方程得到:

一阶SD调制器量化后的信号

误差=连续采样步长中获得的误差之差。因此,一阶SD调制器对量化误差进行微分。换句话说,它将量化噪声调制为量化误差的一阶差分,信号保持不变。

频域,累加器输出可以表示为:

z^−1)是一个在z = 1处有零点,在z = 0处有极点的高通滤波器。

一阶SD调制器的噪声谱密度:

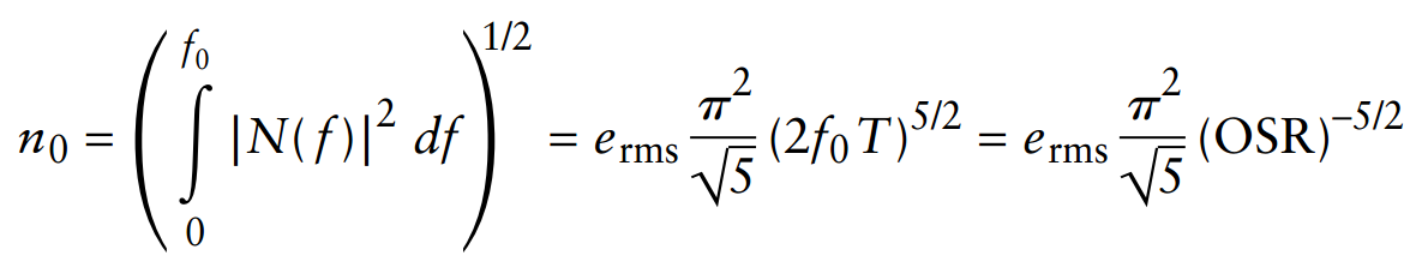

信号频带内的噪声功率为下式,假设OSR足够高,使得fs^2>> f0^2和sin(πfT)≈πfT。

噪声的均方根值由:

因此,在具有一阶SD调制器的采样系统中,过采样比每增加一倍,量化噪声减少9 dB,有效位增加1.5位。回想一下,在没有任何反馈的采样系统中,过采样比每增加一倍,量化噪声仅减少3 dB,有效位增加0.5。虽然SD效应增强了过采样效应,但这两种效应源于不同的现象。SD调制的反馈通过使噪声远离信号带来减小带内噪声,而过采样效应通过在更宽的带宽上平均噪声功率来减小带内噪声。

二阶SD调制器

通过积分的SD反馈通过将其大部分能量置于信号频带之外来塑造调制噪声的频谱。SD噪声整形效果由其高通特性决定。本节将说明噪声频谱的形状是由SD调制器的阶数决定的。

高阶SD调制器可以以各种方式配置。通过在一阶SD调制器上再增加一个累加器和反馈回路,构造一个二阶SD调制器,如图所示。

在z域:

调制器输出噪声现在是量化误差的二阶差分。二阶SD调制器的噪声谱密度

假设fs>>f0,信号频带内的均方根噪声幅值

过采样比每增加一倍,噪声就降低15 dB,从而获得2.5位的额外分辨率。

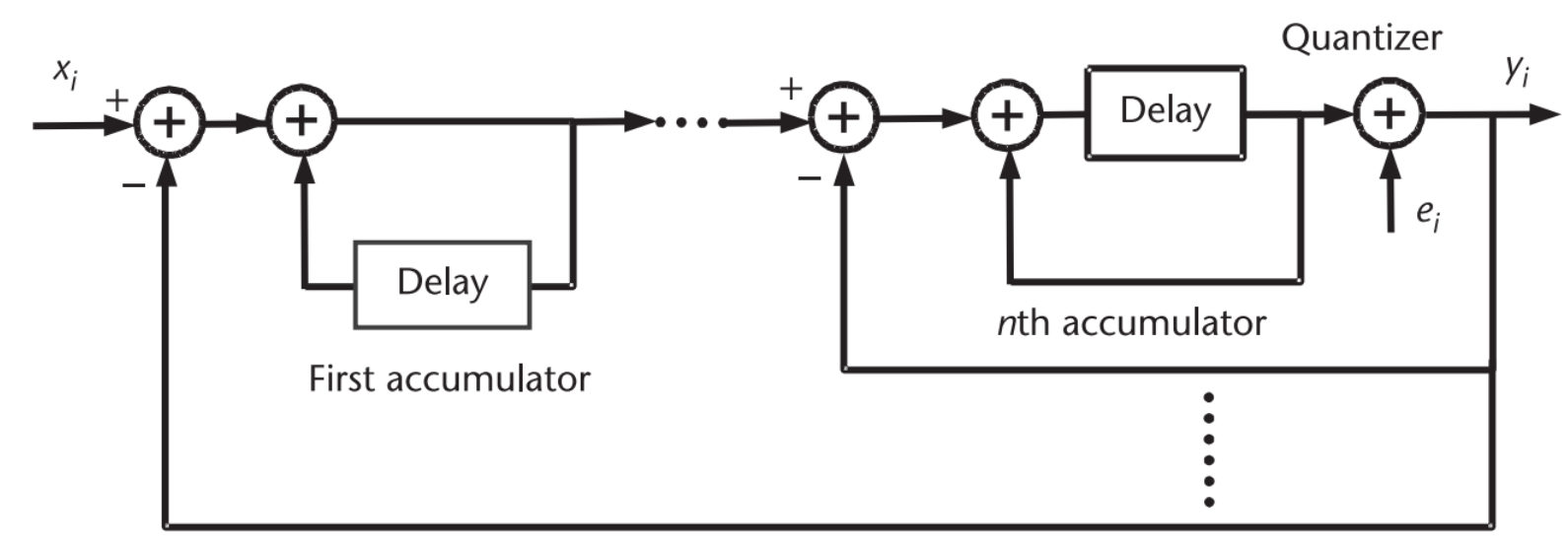

高阶SD调制器

任意阶的SD调制器。一般来说,可以通过在电路中增加更多的反馈回路来配置n阶SD调制器,如图所示。当有n个循环且系统稳定时,其输出可以在z域中表示为

其噪声谱密度为:

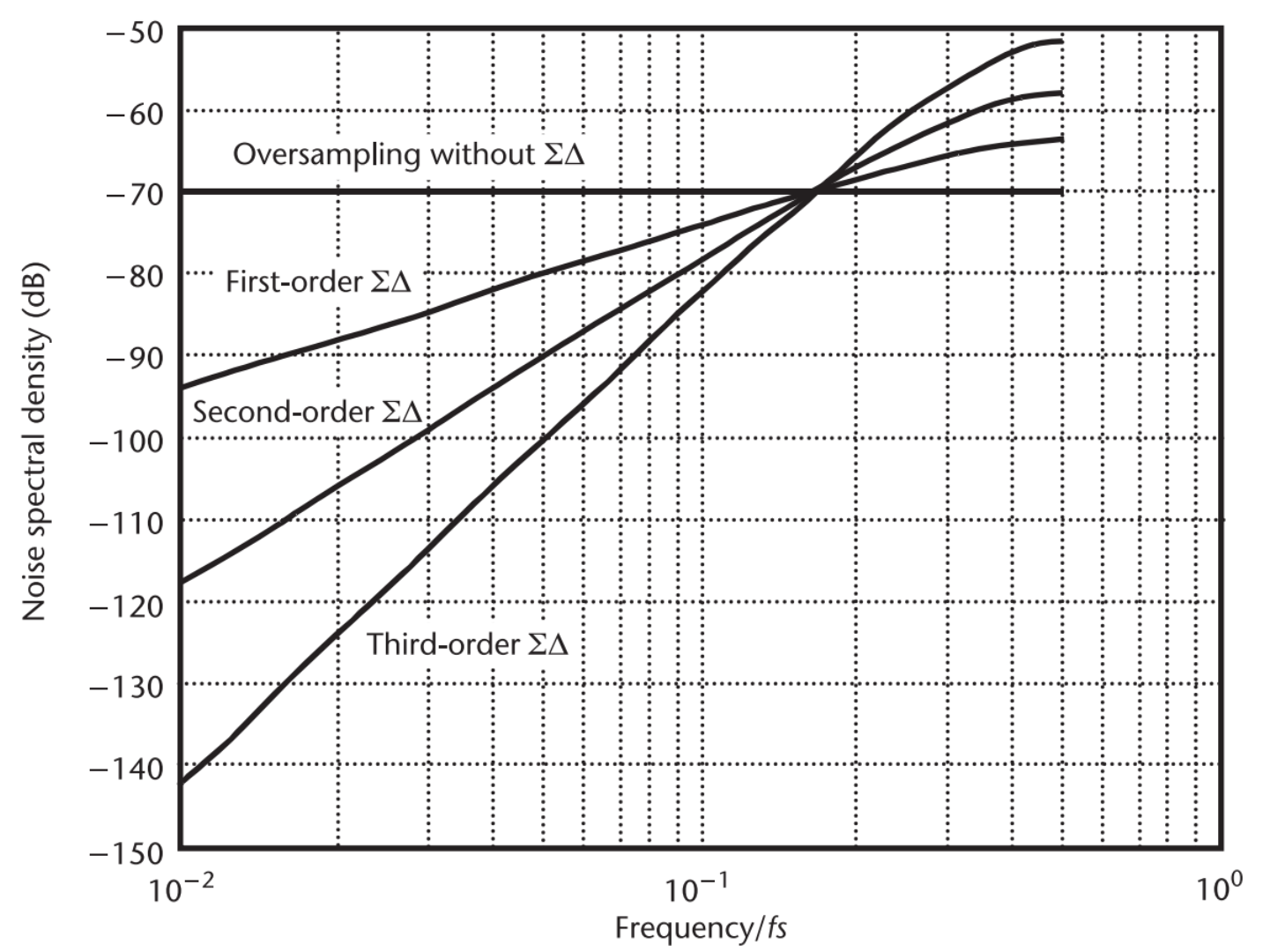

OSR = 32时不同阶SD调制器的N(f)图。

在没有SD调制器的纯过采样系统中,噪声谱密度N(f)是一个随机白噪声,均匀分布在0到fs /2之间。对于带有SD调制器的过采样系统,N(f)的形状使得较低频率的带内噪声与原始白噪声底相比减少,而较高频率的带外噪声则增加。

然而,SD调制器不影响从0到fs /2波段的总噪声功率。不同阶次的SD调制器的差异是噪声整形曲线的斜率。根据高通传递函数,n阶SD调制器的噪声整形斜率为n × 20 dB/dec,即一阶SD调制器为20 dB/dec,三阶SD调制器为60 dB/dec。如果把没有SD反馈的过采样系统当作n = 0,这个规则也有效。

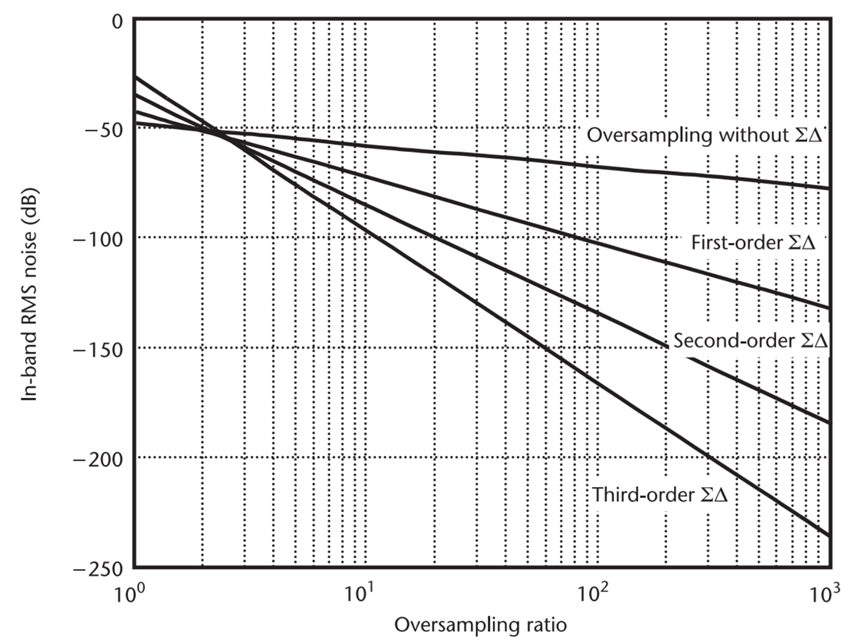

对于大过采样比(OSR > 2),带内rms噪声幅值为

假设fs>>f0,对于N阶SD调制器,可以得出结论,过采样比每增加一倍,带内rms噪声下降3(2n + 1) dB,增加n + 0.5的分辨率。这一结论对无反馈的普通采样系统(n = 0)和有SD反馈的采样系统都有效。其中,3db(0.5有效位)是由于无反馈的普通采样系统中的过采样效应,而6n dB (n有效位)是由于SD噪声整形效应。不同阶SD调制器的带内rms噪声与OSR的关系如图,展示了降噪效果。很明显,加入SD反馈增强了过采样效果。另一方面,如果OSR不够高,SD调制器将不会大大有利于降噪。OSR小于2时,SD噪声整形会增加噪声而不是降低。

由于过采样和噪声整形的性能改进可以通过有效比特数来表征,这导致在固定带宽上具有相同的信噪比。过采样和噪声整形后的信噪比:

N为量化器位数,n为SD调制器阶数。过采样和噪声整形降低了量化噪声,有效地增加了量化器比特数:

注意,如果没有明显的过采样,有效比特的数量就不能大大提高。在奈奎斯特速率(OSR = 1)下,由于SD调制器引入下式中的最后一项,有效比特数甚至减少了。通过以上分析,我们进一步比较过采样和噪声整形的概念,如下图所示。当信号带宽接近fs /2(奈奎斯特速率)时,噪声整形没有任何好处。

小数分频中的SD调制器

小数分频器的输出通过一个有理数除数与参考频率相关,该有理数除数是通过周期性地切换双模或多模分频器获得的。然而,在不同的除数值之间切换会在期望载波频率附近产生不希望的相位抖动或杂散。SD调制器可以利用其高通噪声特性将带内噪声移动到更高的频率。SD调制器在分数阶累加器输出处形成一个高通滤波器,在那里创建分数阶杂散,将接近的分数阶杂散移动到更高的频率,在那里它们可以被环路滤波器去除。SD分数N合成器如图所示,将SD分数累加器作为一个黑盒子。

当使用较大尺寸的累加器时,高阶SD噪声整形是很重要的。上图大小为F、输入字为K的分数阶累加器每F个时钟周期产生K个执行脉冲。当环路锁定时,累加器的时钟为fr /R。因此,累加器执行具有以(fr /R * K / F)为频率,周期性地产生切换循环除法比。回想一下,在时域中任何重复的模式都会在频域中引起杂散。因此,与周期性切换环路分频比相关的小数杂散分量预计为载波频率(fr /R *K / F)的倍数。当K = 1时,最接近的分数杂散出现在(fr /R *1 / F)。因此,累加器尺寸越大,分数阶杂散越接近载波频率。并且需要一个高阶SD调制器来抑制杂散。SD的阶数可根据系统噪声要求来选择。SD调制器用于打破分数N的重复时间(时域)模式,从而减少了谱杂散。与简单的小数N方案一样,任何SD架构都应该提供除数的0净变化,这意味着时间平均除数不应该被改变。基于SD的分数-N合成器按照特定的时间模式抖动除数值,这对应在频域中用高通特性调制分数-N累加器的输出。因此,由整数除数值的改变引起的分数杂散被移动到更高的频率,在那里它们可以被环路低通滤波器更有效地衰减。

分数N频率合成的一阶SD调制器

为过采样ADC引入的噪声整形概念也可以应用于分数N合成。在频率合成中,所需的分数频率相当于A/D转换器的模拟输入。双模预加量器或多模分频器的数字模控制类似于1位或多位量化器输出。SD调制器如图所示,其输入是模拟信号,输出是1位采样的数字数据流。

在分数N合成中,分数杂散来自分数累加器,输入是以数字格式表示的恒定频率字K,输出是用于控制分频器模量的1位执行。将SD到分数n累加器中,得到SD调制累加器,如图所示。积分器执行累加器功能,当延迟单元放置在反馈路径上时,其传递函数为1/(1-z^-1)。延迟单元也可以与积分器结合,形成传递函数为z^-1/(1-z^-1)。

1位比较器和1位量化器相当于累加器的执行;也就是说,1位量化器截断积分器输出的MSB并丢弃其余的位。由于输入是数字频率字,因此在分数N合成中不需要1位DAC。转换到采样后的时域,得到一个等效电路,如图所示,其中。.F(z)表示除数值的小数部分,在频域相当于K/F。" F(z) "前面的 “.”是函数名的一部分。

虽然分数阶累加器的输入是一个常数(K/F),但当多个累加器级联形成一个高阶调制器时,通常需要将SD调制器的输入定义为z域中的函数,其中除第一个累加器外,所有累加器的输入都是时变的。

SD分数N输出为:

Eq为将累加器值截断为1位执行时引入的量化误差。量化误差Eq通过加入一阶SD调制器进行了高通滤波,而分数阶频率字.F(z)不受影响。因此,由于周期性截断的杂散被移动到更高的频率,并且平均除数值保持不变,可以为分数N合成构建高阶SD调制器。对于这两种调制器,添加反馈回路的技术非常相似。

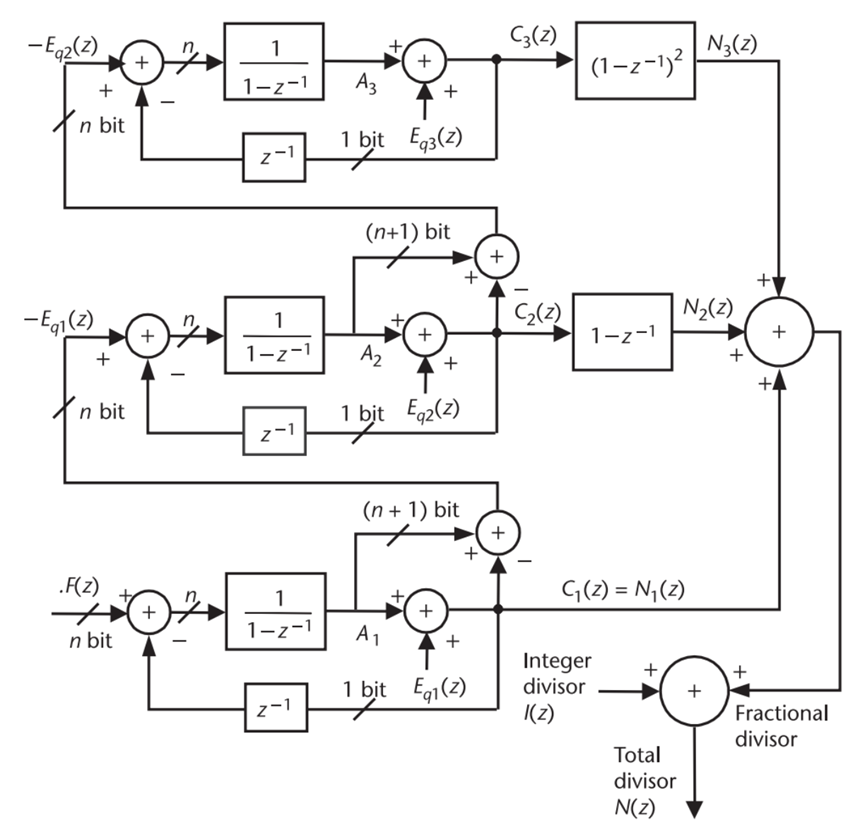

MASH SD调制器

MASH 1-1-1

图显示了一个由三个环路组成的MASH SD调制器。所示的三回路SD拓扑也称为MASH 1-1-1结构,因为它是一个具有三个一阶回路的级联SD结构。三个中的每一个环路与前面讨论的单环路架构相同。第二回路的输入取自第一回路的量化误差Eq1,第三回路的输入取自第二回路的量化误差Eq2。因此,只有第一个环路具有恒定输入,它是期望的有理数.F(z)。在三环SD调制器的输出端加入频率字I(z)的整数部分,即粗调频率字。因此,Ndiv (z) = I(z) + . F (z)是用于控制分频比的时间序列。传递函数为(1−z−1)和(1−z−1)2的微分器块分别在第二和第三个回路的输出处添加。调制器的时钟在参考频率,反映电路的采样性质。三环SD调制器的z域传递函数可推导为

第一个环路产生分数除数值. F(z)和量化误差Eq1,第二个环路通过其输出路径中的微分块(1−z−1)抵消前一个环路的量化误差Eq1。在对第一环路和第二环路输出求和后,剩下的唯一量化噪声项是量化误差Eq2,它是二阶噪声形。当该噪声项进一步馈送到第三个回路的输入时,该回路产生负噪声项,通过其输出路径中的二阶微分块(1−z−1)2来抵消前一个回路的量化误差Eq2。将三个回路的输出相加,得到调制除数的值为

I(z)和. f (z)分别是除法比的整数部分和小数部分。.F (z)不受调制器的影响,尽管使用了三个环路,但总量化噪声等于单个环路的噪声。因此,多环路SD架构提供了高阶噪声整形,而没有额外的量化噪声。

带级联m环SD调制器的分数n合成器的输出频率可表示为

第二项是由于分数杂散引起的频率噪声。

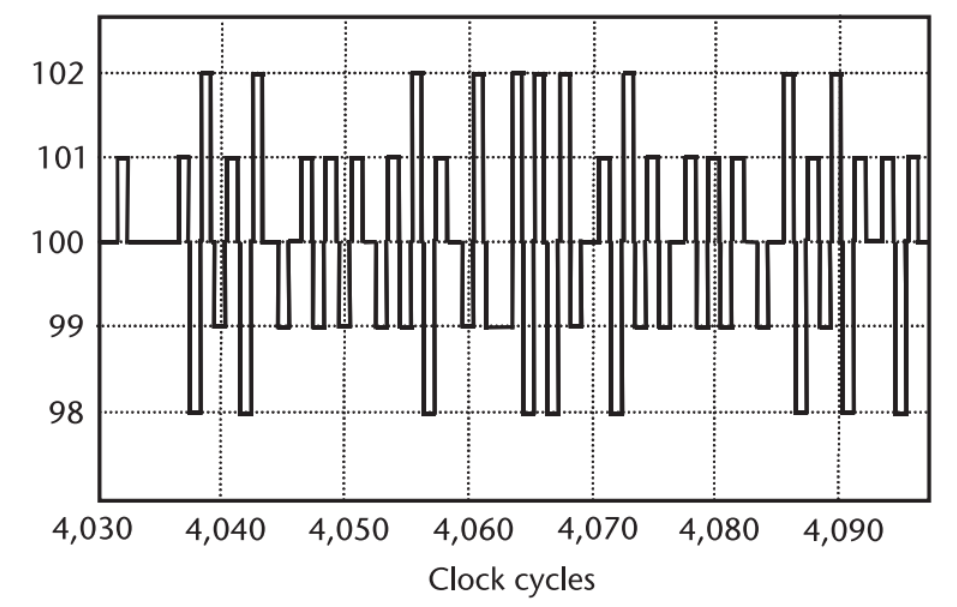

MASH 1-1-1 SD调制器与简单分数N累加器的比较,在N(z) = I(z) +.F(z) = 100 + 1/32情况下,比较分数阶累加器输出(m = 1)和三阶SD调制器输出(m = 3),fr = 10Mhz。

当m = 1和m = 3时,模拟累加器输出如图所示。不带SD调制器(m = 1)的分数阶累加器每32个fr周期执行一次,这迫使环路除法器在31个周期内除以100,然后在1个周期内除以101。除以101的周期相位校正脉冲产生均匀间隔为fr/32 = 312.5 kHz的分数型杂散,如图所示。

如果使用三个级联环路,SD累加器输出将在正确的值附近抖动。SD噪声整形器打破了分数除数序列的周期性。在频域中,离散杂散变得更随机,它们的能量推到更高频处。在SD噪声整形后的频谱中,分数杂散看起来更像频率噪声,而不是离散音阶。

对于单回路分数N累加器(m = 1),二进制执行器在I(z)到I(z) + 1的范围内抖动回路除法器,因为C1是一个1位数字,其值可以为0或1。对于双回路MASH SD累加器(m = 2),C1的值可以为0或1。C2−z−1 C2的值可以为−1、0、1;因此,求和将使环路除法器在I(z)−1到I(z) + 2的范围内抖动。类似地,对于三回路MASH SD累加器(m = 3),执行器C1、C2−z−1 C2和C3−2z−1 C3 + z−2 C3将在I(z)−3到I(z) + 4的范围内抖动环路分频器。因此,SD调制器阶数越高,环路分频比抖动的范围越宽。一般来说,m环MASH SD调制器使环路除数在I(z)−2m−1 + 1到I(z) + 2m−1的范围内抖动。

上面是三环SD调制器的系统流程图,现在要用实际电路来实现它。首先,函数1/(1−z−1)是一个积分函数,可以用一个累加器来实现。其次,检查量化器的功能。假设累加器有一个n位的输入字。如果需要保留进位位,则累加器的输出为N+1位字Ai,Ai为第i个累加器输出。量化器通过选择其MSB作为累加器输出来截断(N+1)位字Ai。MSB仅仅是累加器的进位Ci。该过程引入了Eqi=Ci−Ai的量化误差,该误差被馈送到下一个累加器中用于噪声整形。当累加器没有溢出(Ci=0)时,1位环路反馈对累加器性能没有任何影响。当累加器溢出(Ci=1)时,1位环路反馈从累加器输入 .F(z)中减去Ci。注意,为了减法的目的,Ci取{1'b1,n{1'b0}}的值,其中Verilog级联表示法表示MSB=1的(N+1)位二进制字,其余位为零。换言之,1位Ci在输入到加法器之前与累加器的模数相乘,因为它具有第(N+1)位的权重。这个过程只是N位累加器溢出。发生溢出后,累加器从剩余值Ai−Ci开始。其他循环的操作与第一个循环的操作等效,除了它们的输入是前一个循环的截断量化误差外。

可以使用下面的电路来具体实现:

函数1−z−1实现为微分器电路。因此,整个SD调制器只包括加法器和延迟单元z−1,它们可以用时钟触发器实现。多环路SD调制器的速度瓶颈是带进位的N位加法器。进位的后处理可以使用流水线前馈体系结构来实现。MASH结构绝对稳定,非常适合高速应用。

为了理解分配给每个加法器的位数,需要回顾一下从上图底部的2位加法器开始的算术运算。三个累加器的进位C1、C2和C3只能为0或1。因此,2位加法器输出C3(1−z−1)可以是−1,0或1。加C2得到一个3位项C2 + C3(1−z−1),取值范围为−1、0、1或2,可以用一个3位的二进制补字来表示。令A = C2 + C3(1−z−1)和B = [C2 + C3(1−z−1)]z−1,(A−B)的3位减法得到一个3位的二进制补字,范围从−3到+3。例如:A =−1 = 3 ' b111, B = +2 = 3 ' b010,−B =−2 = 3 ' b110,则A−B = 3 ' b111 + 3 ' b110 = 3 ' b101 =−3。将C1与A - B相加,我们得到一个4位字,范围从- 3到+4。三阶MASH SD调制器的输出为4位,最大值为4,最小值为−3。因此,调制器在I(z)−3到I(z) + 4的范围内抖动环路除数。

MASH 1-2

除了MASH 1-1-1拓扑外,(1−z−1)m的高通噪声传递函数也可以使用不同阶次的环路组合来实现。对于三阶SD调制器,如图所示的MASH 1-2拓扑由一阶环路和二阶环路组成。MASH 1-2 SD调制器的优点是简化了拓扑结构,降低了硬件和功耗。

MASH 1-1-1结构由于其稳定性、高阶带内噪声整形特性和易于实现而成为广泛应用的拓扑结构。SD调制器使环路分割比在其平均值附近抖动。同时,对于SD调制的锁相环,相位误差总是很小。然而,为了使环路锁定到所需的频率,平均相位误差应该为零。不幸的是,对于多环路MASH SD调制器,调制器的阶数越高,引起的相位误差就越大。为了在不降低噪声整形斜率的情况下改善相位误差分布,需要研究替代拓扑结构。

具有多个反馈路径的单级SD调制器

噪声传递函数(1−z−1)m也可以通过单级和多反馈路径实现,如下图所示。MASH 1-1-1是绝对稳定的,由于反馈回路减小输入范围,单级反馈SD调制器是有条件稳定的。单级反馈SD调制器可以输出单个比特或多比特,而MASH 1-1-1或MASH 1-2 SD调制器只能输出多比特。使用单级SD调制器,可以基于期望的输出量化噪声电平和环路除数变化的范围来选择其输出比特的数量。

累加器具有以下传递函数:

单级反馈SD调制器输出为

信号传递函数

噪声传递函数

信号X(z)只经历了传输延迟z−1,而量化噪声被(1−z−1)m的高通噪声传递函数抑制。

具有单一反馈路径的单级SD调制器

在累加器中插入传递函数为H(z) = 1−He (z)的块,累加器输出为

其中Y(z)是加法器输出B(z)中最重要的p位,A(z)是B(z)中剩余的(n+1−p)位。很明显,输入信号X(z)不受调制器的影响,截断A (z)产生量化噪声E(z),由He (z)的噪声传递函数滤波。若噪声传递函数He (z)为高通传递函数(1−z−1)m,反馈传递函数为H(z) = 1−(1−z−1)m,则单级调制器等效于Y(z) = X(z)−E(z)(1−z−1)m的MASH调制器。注意,当m = 1和p = 1(1位进位)时,SD调制器退化为标准分数阶累加器。因此,当m = 1时,该结构相当于没有噪声整形的标准分数阶累加器。如果输入频率字X(z)有N位,则B(z)应该有(n + 1)位以包含进位,并且A(z)H(z)不能超过N位。调制器输出Y(z)可以是任意数量的位,在选择输出位的数量方面提供了灵活性。但是,A(z)H(z)的最大位数应该仔细计算,以防止加法器溢出。

当m = 2时,H(z) = 1−(1−z−1)2 = 2z−1−z−2。二阶调制器如下图所示,其中z−2项的减法是使用2的补码格式实现的,乘以2是使用左移操作实现的。当n + 2−p < n时,通过扩展(n + 2−p)位的MSB来进行符号扩展,得到一个n位字。可以看出,需要维持n + 2−p≤n的条件,以防止输出为(n + 1)位的第一个加法器丢失溢出位。因此,二阶调制器的最小输出位数为2,一般来说,给定单级SD累加器的输出位数应等于或大于调制器m的阶数。

当m = 3时,H(z) = 1−(1−z−1)3 = z−1(3−3z−1 + z−2)。三阶单级SD调制器如图。同样,减法是使用2的补码格式实现的。乘法乘以3是通过左移操作(×2)实现的,然后是加法,数学上给出3z−1 = 2z−1 + z−1。单级SD调制器拓扑的速度受到与计算传递函数H(z)的加法相关的延迟时间的限制。SD调制器的阶数越高,延时越长。

SD调制器引起的相位噪声

离散分数杂散经过SD噪声整形后变得更像随机噪声。噪声形分数杂散的SSB相位噪声分析如下:

1位量化误差功率为∆![]() 2 /12。对于量化步长∆

2 /12。对于量化步长∆![]() = 1,量化误差功率为1/12。该误差功率分布在采样带宽上(fr = 1/Ts的参考带宽)。因此,误差PSD变为1/12fr。考虑用m阶MASH SD调制器进行噪声整形,则频率噪声PSD为:

= 1,量化误差功率为1/12。该误差功率分布在采样带宽上(fr = 1/Ts的参考带宽)。因此,误差PSD变为1/12fr。考虑用m阶MASH SD调制器进行噪声整形,则频率噪声PSD为:

下标Ω表示频率扰动,频率和相位的关系:

转化到z域

Ts = 1/fr为采样周期,整理得到相位波动:

双向带相位噪声PSD为

相位噪声φ2在rad2/Hz 域和相位噪声PN 在dBc/Hz的关系

相位噪声单边带调制(SSB)的频域功率谱密度(PSD):

f为偏移频率,fr为参考采样频率。为了找出相位噪声对锁相环输出的影响, SD的噪音被注入如图,其对输出的噪声传递函数为

由于SD噪声传递函数的高通性质,环路滚降的顺序非常重要。m阶MASH SD调制的噪声整形斜率为20(m−1)dB/dec,而n阶低通环路滤波器的滚降斜率为20n dB/dec。因此,环路滤波器的阶数必须高于或等于SD调制器的阶数,以衰减SD调制引起的带外噪声。因此,有必要在环路滤波器中包括C2的影响,因为这将提供额外的带外衰减。在这种情况下,输出的SD噪声传递函数为

SD相位噪声:

从这张图中,很容易看出一阶调制器(没有噪声整形的分数n累加器)产生太多的噪声,实际上将完全支配该合成器的噪声性能。另一方面,二阶MASH SD调制器不会降低带内噪声。但是,在1 ~ 3mhz范围内,由于SD噪声与总噪声大致相等,会使设计的相位噪声增加3db。研究滤波后SD噪声曲线的形状也很有趣。在带内,由于二阶噪声整形效应,SD相位噪声以20 dB/dec的速度上升。在环路转角频率处,由于第一环路滤波器极点的衰减而平坦。一旦环路滤波器的第二极开始生效,滤波后的SD相位噪声响应降至20 dB/dec。另一方面,三阶SD调制器的噪声远低于环路中其他元件的噪声,因此对总锁相环噪声的影响可以忽略不计。然而,请注意,即使在环路滤波器的第二个极点之后,这种噪声也只是平坦的带外。如果这种噪声性能是不可接受的,并且需要一个四阶SD调制器,那么将需要一个高阶环路滤波器来防止带外SD噪声的增长。

4153

4153

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?