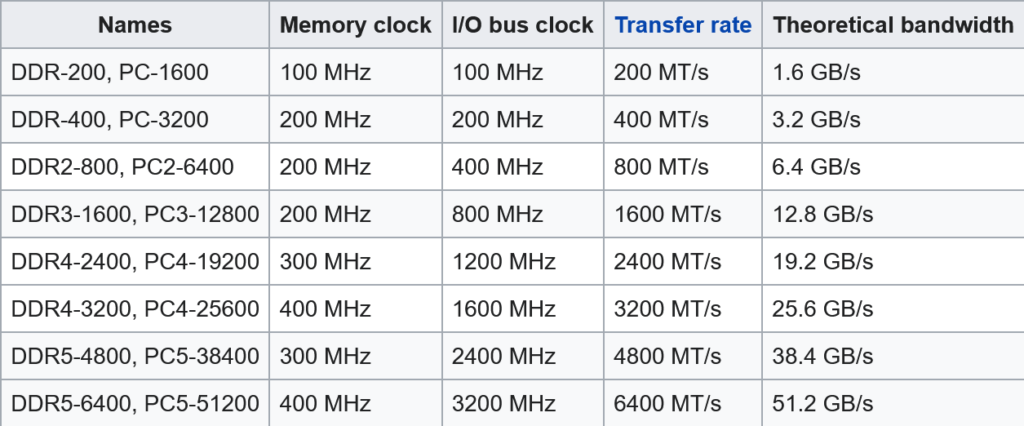

随着英特尔第 12 代 Alder Lake-S 处理器计划在今年年底推出,下一代 DRAM 即将正式问世(内存厂商已量产或小批量DDR5),DDR5 将会以4,800Mbps 起步进入零售市场。相比之下,根据 JEDEC 规范,DDR4速度只能达到3,200Mbps。

DDR5做了许多改变来提高内存传输频率。首先,增加BL将内存预取增加到 16;其次,将banks加倍到 32(每个 BG 2 或 4 个),同时还支持旧的 16 banks、刷新(基于每个bank刷新)和双通道 DIMM等:

突发长度: DDR4 的BL为 8,与 DDR3 相同,允许一次从缓存中传输高达 16B 的数据。DDR5 将其增加到 16,并支持 32 长度模式,这意味着只使用一个 DIMM 就阔以获取高达 64 字节的缓存行。

要了解突发长度(BL)的含义,就需要知道内存是如何访问的。当 CPU 或缓存请求新数据时,地址会被发送到内存模组,然后指向所访问bank、Row,然后定位Col(如果不在当前行,则加载新的Row)。请记住,每一步之后都会有延迟。

然后定位到对应列通并过内存总线以突发方式发送数据。对于 DDR4,每次突发为 8(或 16B)。使用 DDR5,它已增加到 16 个,进一步扩展到 32 个 (64B)。每个时钟周期有两个突发,它们都是以有效数据速率发生。

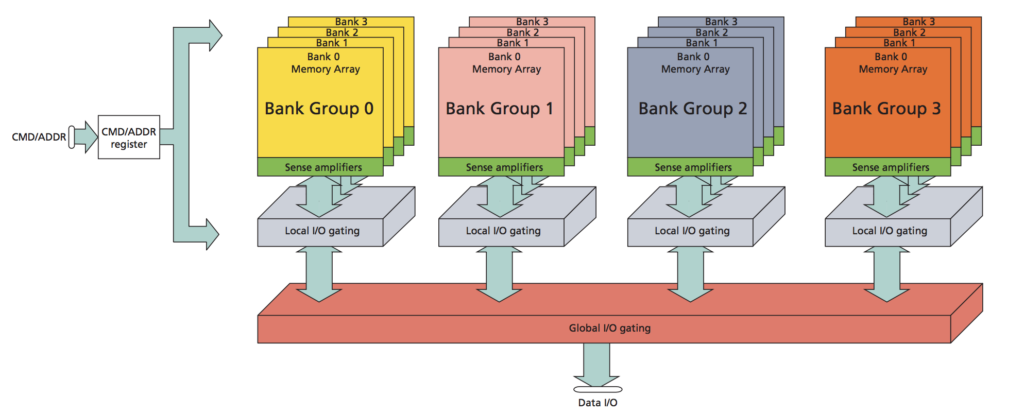

16n 预取: DDR5 预取也已扩大( DDR4 是 8n)到 16n。与 DDR4 一样,每个通道通过 MUX 连接两个内存组阵列,从而实现更高效预取(见上图)。

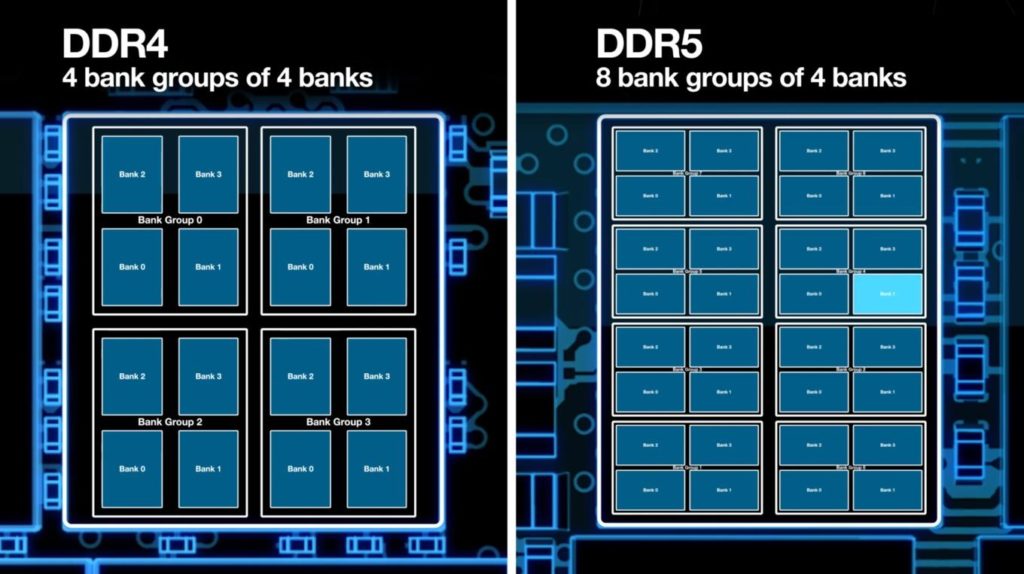

多的Bank Groups: DDR5 将banks增加到 32 个,共 8 个BGS,每个BG有 4 bank。这也增加了带宽和性能,因为内存控制器可以同时访问更多的 bank,类似于双列内存在单Rank上的改进。

bank 刷新:对于 DDR4,当内存单元被刷新时,它不能向任何 bank 发出进一步的指令,因为所有的 bank 都是同时刷新的。DDR5 允许相同bank刷新,既允许部分bank进行刷新、剩余bank仍进行工作,提高有效带宽。

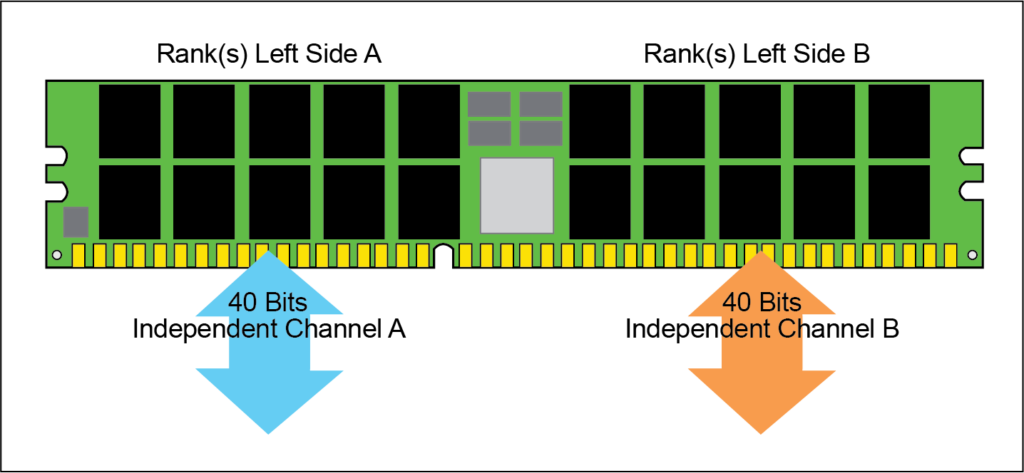

双通道 DIMMs:DDR5 每个 DIMM 有两个 32 位内存通道(而 DDR4 上只有一个 64 位)。这意味着我们将看到两个 DIMMs 四通道配置。每个 DIMM 的两个通道是独立的,可以分别发送命令。由于BL是 DDR4 的两倍,这可以增加每个 DIMM 的数据传输总数来提高整体带宽。

集成稳压: DDR5 将 VDD 和 VPP 电压从 1.2v 降低到 1.1v,降低内存功耗。DRAM 稳压器也已从主板移至内存模块,降低了前者的电路复杂性。

DDR5 还将内存密度从 16Gb 一路(向上)增加到 64Gb,同时还将运行时钟推高至 4200MHz(或 8400MT/s)。采用决策反馈均衡 (DFE)电路,消除高速反射噪声,提高每个引脚的速度。

片上 ECC: DDR5 内存上片上ECC的存在一直是消费者和媒体等众多讨论和混淆的概念。与标准 ECC 不同,片上 ECC 主要用来提高先进工艺节点的良率,从而降低 DRAM 芯片成本。片上 ECC 仅检测在刷新期间发生在cell或Row的错误。当数据从cell移动到缓存或 CPU 时,如果有位翻转或数据损坏,它不会被片上 ECC 纠正。标准 ECC 可纠正cell内的数据损坏,并将其移动到另一个设备或支持 ECC 的 SoC。

1588

1588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?