一、TTL和CMOS不适用于高速电路设计的原因(都是数字电路信号)

原因:

①电平幅度较大,电平最低都达到了2.5V或者3.3V。因此信号沿变化所需要的时间很长。不适合大于200MHZ的信号。

②容易被干扰,输出信号为单端,在传输路径容易受到干扰,不利于远距离传输。

③功耗大。功耗分为静态功耗和动态功耗。因为电平摆动大,所以导致动态功耗大。部分CMOS静态功耗较小,但是普遍都大。动态功耗很大。

二、高速电平的优势

LVDS、LVPECL、CML三种电平适用于高速电路。LVDS信号最常用。

原因:①电平摆幅窄,②支持远距离传输,③功耗小。

高速电路都是采用差分信号进行传输。差分技术的优势:

①抗干扰能力强。

②对参考平面(地平面或者电源平面)完整性要求较弱。

③抑制串扰、EMI能力强。

④功耗小,速率高、不受温度、电压波动的影响。

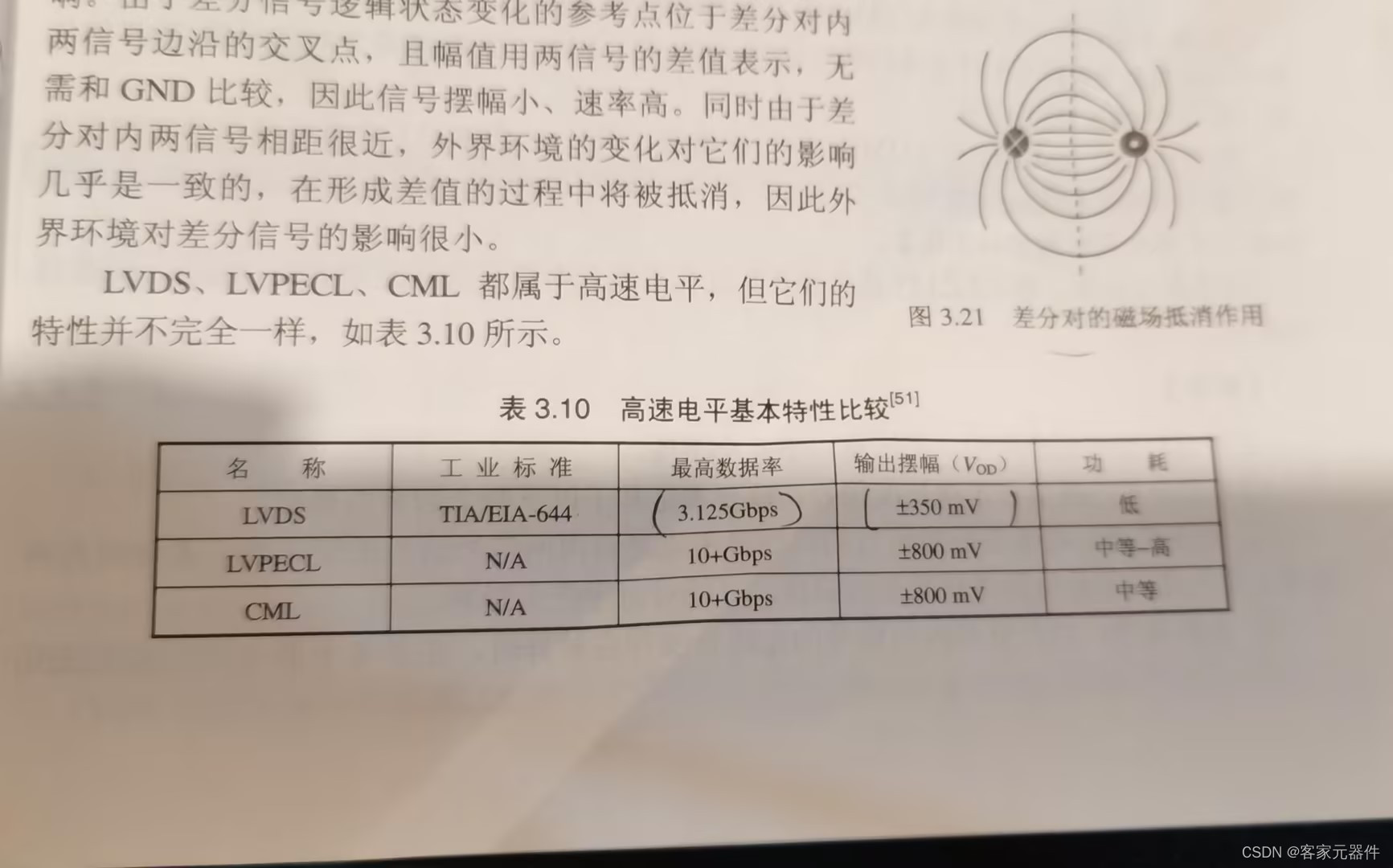

LVDS、LVPECL、CML特性图如下:

案例:

EMC测试时,发现用户面板上USB口附近,399MHz处辐射超标。

检查之后发现PCB板子:1、USB口的差分对走线相邻层有时钟信号线。距离仅为2mil。

2、与差分线走线平行,平行长度达到1400mil。

3、且距离差分对7mil有时钟线的过孔。

三种都会对差分线进行干扰。导致辐射超标。

最后通过PCB改版。将时钟和差分线间距增大到20mil,完美解决了问题。(通常是3倍走线线宽以上)

三、差分信号需要注意的问题

(1)差分对等长问题 (必须等长)

①走线长度要一致(总误差4mil以内),长度不一致会导致时序问题,导致参考平面的回流无法完全抵消,从而产生共模噪声。

②在平行和等长之间,先保证等长。

③地平面要完整。地平面不完整会产生共模噪声,严重时会产生EMI问题。

(2)差分对内两个信号的间距越小越好

①间距越小,附件的干扰对差分对内两信号的影响接近一致,方向相反,近似等于抵消。

②差分对内两信号电流相反,形成电流环路,电流环路能产生磁场,磁场又能产生电场,从而构成电磁干扰。所以减小两线间距,能较小电流环路,从而减小电磁干扰。

(3)差分对内两个信号的间距要保持一致。不一致会产生反射。

(4)差分信号需要进行阻抗控制,通常是100Ω。

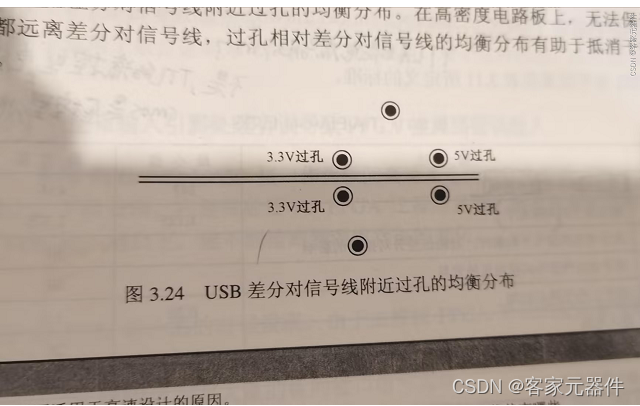

(5)尽量保证差分对信号线附件的过孔是对称的。

四、LVDS信号介绍

最高速度为3.125Gbps,一般应用于点到点的场合。

举例子:用于并行高速总线SPI4.2的I/O接口电平。

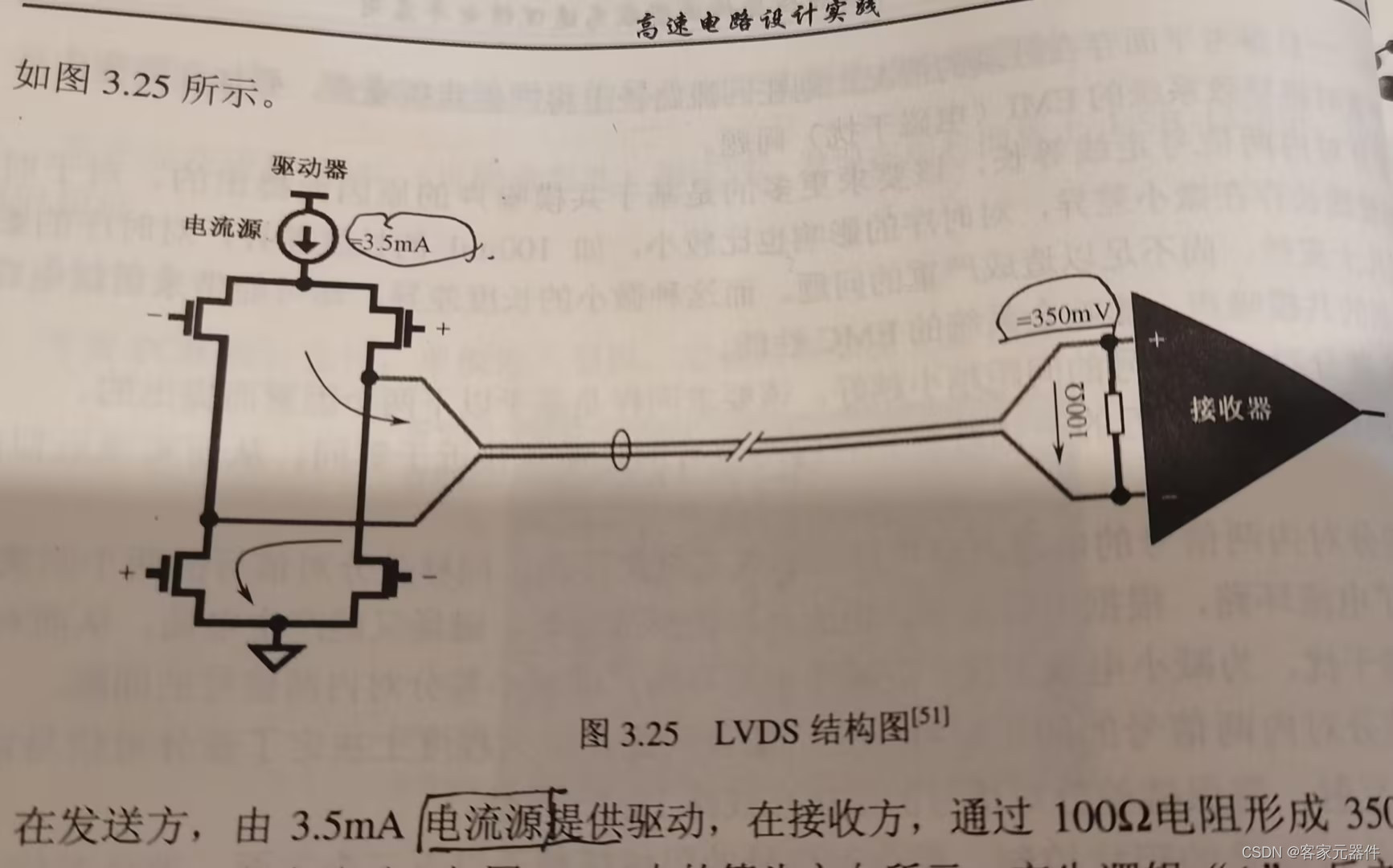

1、驱动器驱动电流为 3.5mA。

2、终端通过在差分线两端接100Ω电阻形成350mV的电压摆幅。

3、正向流动,产生逻辑电平1。反向流动,产生逻辑电平0。

4、摆幅小,功耗低,功耗为 3.5mA*350mV=1.2mW。不随着频率升高而增大功耗。

5、高速逻辑电平中,LVDS是功耗最低的。

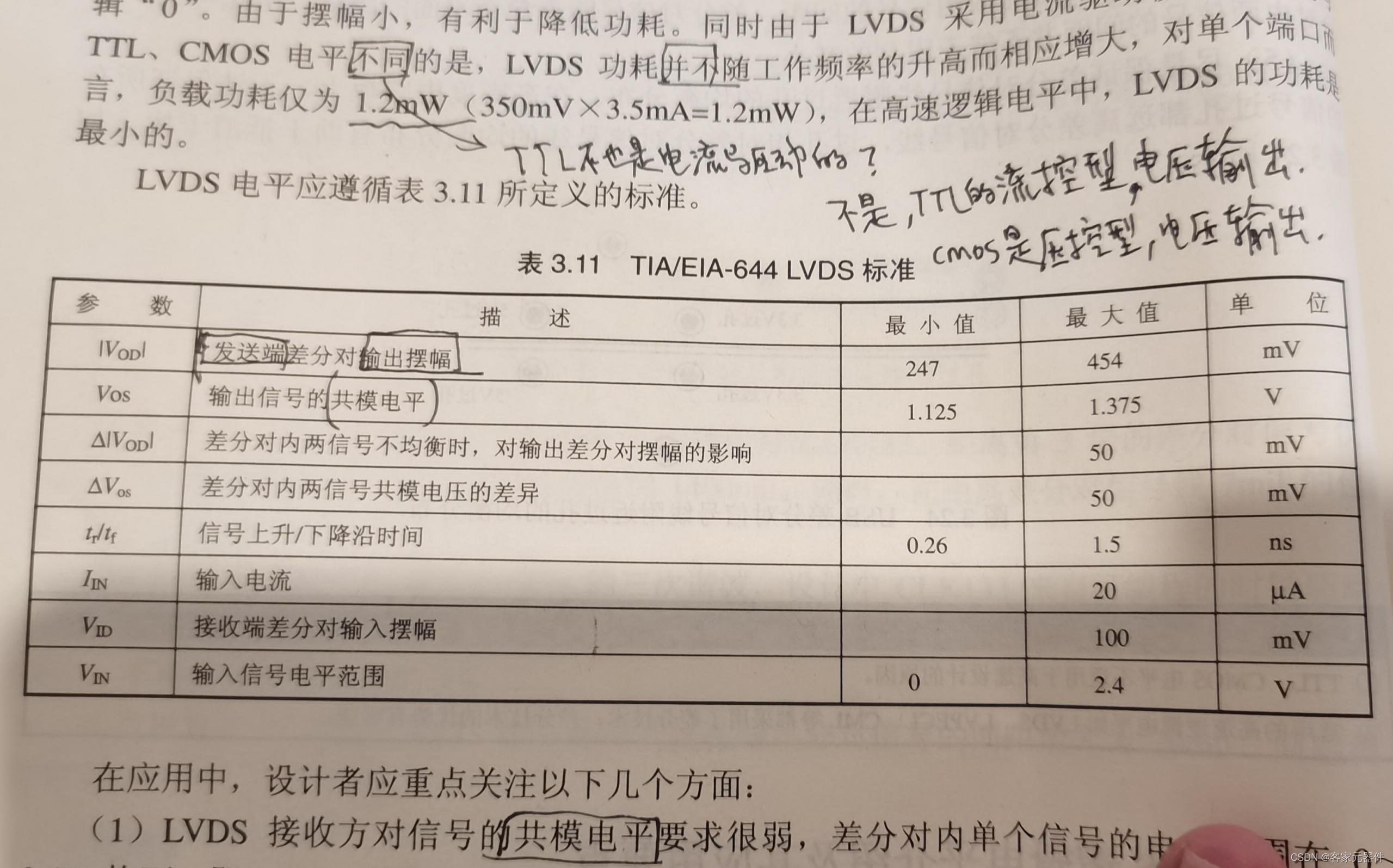

下图是 TIA/EIA-644 LVDS标准

在应用中,设计者应该关注以下几个方面:

1、 LVDS接受方对信号的共模电平要求很低。电压在0~2.4V均可以。(LVPECL不具备这种特性)所以LVDS适合板间长距离信号的传输。因为差分摆幅最大值为454mV。因此运行输入端信号携带的直流偏执电压范围为0.227V~2.173V。如果不满足上述要求。应采取AC(交流)耦合。

2、LVDS接收端对输入差分对信号摆幅的要求是100mV。(差分对的压差必须要有100mV才能正常工作)

3、LVDS信号在终端必须在差分对上串接一个100欧电阻。作用是:①用于实现电流向电压转化。②实现阻抗匹配。

4、LVDS信号的变化速率较低。爬升时间为0.5ns。所以信号沿变化速率是0.7V/ns,变化速率越低。EMI就越小。所以LVDS电平有助于减小EMI。

5、一个芯片可能有两对甚至更多LVDS差分线,空闲的输入引脚应浮空。防止产生噪声。空闲的输出引脚应浮空。以减小功耗。

6、LVDS不适用于数据速率为2Gbps以上的应用。如果速率需要超过Gbps以上,应考虑LVPECL电平。

注意:空闲的LVDS引脚就应该直接浮空,不能做上下拉处理。主控板FPGA上的空闲的LVDS引脚做上下拉处理时。PCB位置应该尽量靠近主芯片。避免因为走线距离太远。信号线与旁边的信号线产生串扰。串扰的电压大于100mV。就会使得电平状态发生变化。

解决方式:①改版时删除上下拉。②关闭FPGA内部的空闲端口。

拓展:

在高速设计中,高速差分对经常作为板间互连接的接口信号。设计者应该关注 TTL、COMS等单端信号对这些差分信号的共模噪声影响。虽然差分信号的接收端对共模噪声的抑制能力很强,一般不至于出现判断错误,但在差分信号线的上的共模噪声却可以产生对外辐射,成为一种EMI源。对此,有两种解决方法,

①在PCB上增大单端信号和差分信号的间距。

②降低单端信号的驱动电流。例如选择低驱动能力的逻辑器件,或者FPGA设计中,将输出端口设置为弱电流驱动模式。

五、LVDS端口保护

LVDS是常用的板间互连接口。当A板不在位时,B板LVDS接收器的输入端失去了驱动源,处于开路状态。此时,接收器的输出端将保持为逻辑“1”(由LVDS器件的内部逻辑保证),这种状态是正确的。

一旦输入端信号线(在B板上,从背板连接器到LVDS接收器之间的信号线)上引入了噪声,且达到接收端的阈值100mV,这种正确的状态将被打破,使接收器的输出端状态翻转为逻辑“0”。

解决方法有很多种,①某些LVDS接口器件内置有保护电路,使用时和普通LVDS器件一样,外加100Ω端接电阻即可,②某些LVDS接口器件则需要外加保护电路。

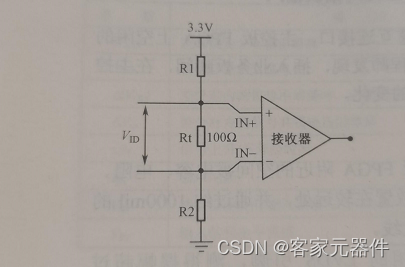

下图是一个外加保护电路的例子。

除了串接了电阻Rt外,外置保护电路增加了R1和R2两个电阻形成偏执电路。

LVDS接收器输入端浮空时,VID会有个固定的正偏执电平。从而提高更大的噪声范围,但噪声小于VID时,接收端器的输出仍可保持逻辑“1”的状态。一般这个值为mV。

举例子,以25mV为例。求R1和R2的阻值

VID=25mV=100*3.3V/(R1+R2+100)

VOS=1.25V=(R2+50)*3.3V/(R1+R2+100)

1.25V是前面的规格书里面写的输出信号的共模电平(1.125~1.375V)取中间值。

注意: R1、R2、Rt都应该尽量靠近接收端位置,且偏执电路要远远小于LVDS提供的3.5mA电流,以免影响LVDS接收器的正常工作。

3.3V/(R1+R2+100)= 0.248 mA。满足要求。

这种外部保护电路存在一定的局限性。

①可能导致LVDS信号的占空比失真。

②由于增加两个电阻会占PCB位置。

2029

2029

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?