低压差分信号LVDS(low-voltage differential singal)电路是一种常用的io电路,其有抗干扰能力强、功耗低等优点,很多协议都对lvds信号有定义,例如ANSI/TIA/EIA-644标准中定义的LVDS指标为,共模电压1.125~1.375V,差模幅度247~454mV,如下图:

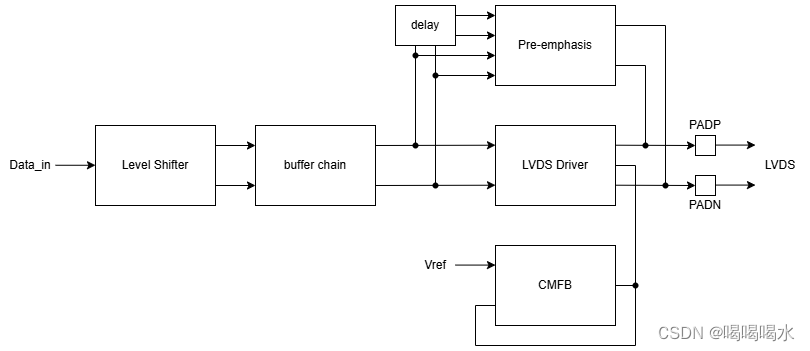

因此我们需要一个稳定的共模电压,以及一定幅度的差模电压信号,本文介绍一种Bridged-Switched Current Source(BSCS)结构的lvds电路,其框图如下所示:

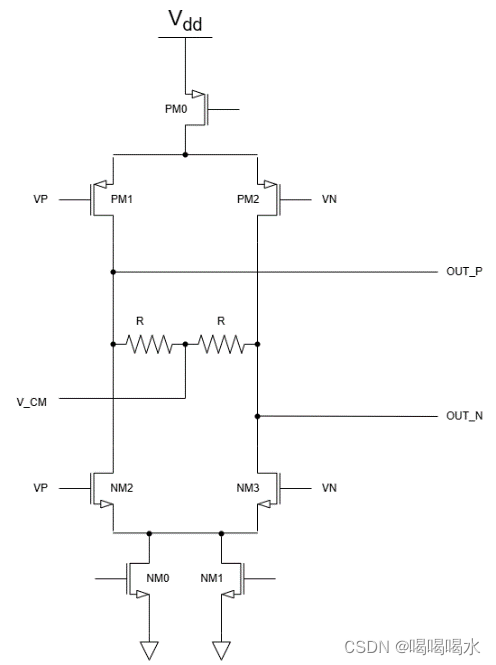

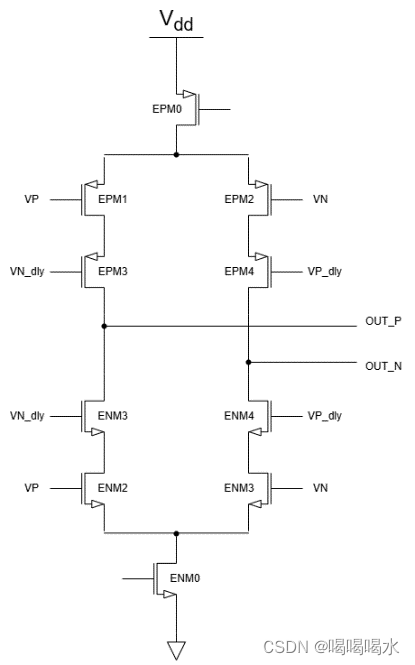

一个稳定的共模电压,一般会用基准电压来提供。如果要求不高,电源也比较稳定,可以用电阻分压来获得。外来电压一般通过共模反馈电路提供给lvds电路。差分电压可以通过电流乘以电阻实现。下图是BSCS电路的主体结构,其中PM0为电流源管,其电流与2R0相乘得到差分电压,V_CM为共模电压,OUT_P和OUT_N输出lvds电压。

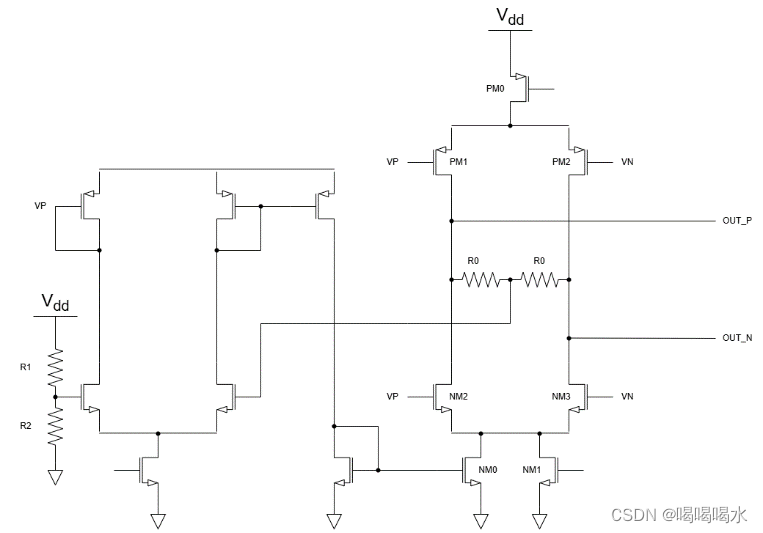

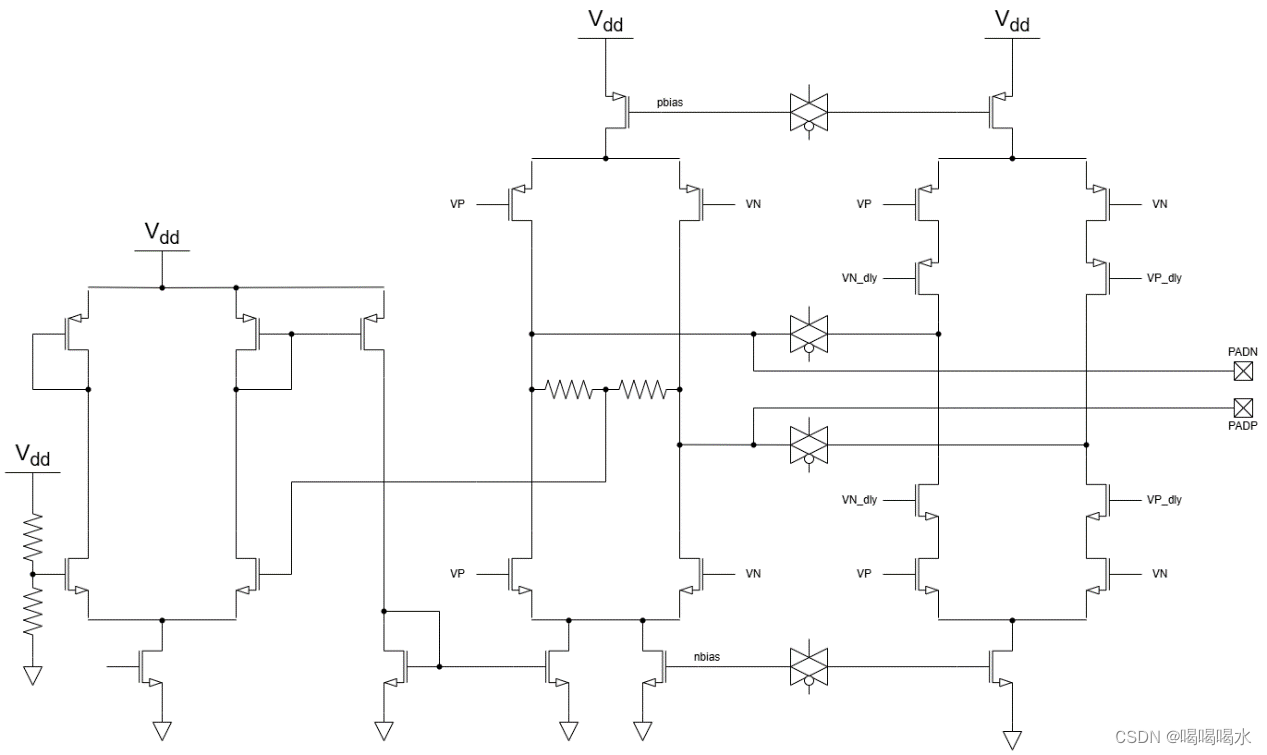

共模反馈电路可以用简单的五管运放搭建,如下图,电阻分压的基准电压提供共模电压。

VP与VN为反向的信号,控制PM1、NM3或PM2、NM2导通,当PM1、NM3导通时,电流从OUT_P流向OUT_N,当PM2、NM2导通时反之,差分信号因此产生。

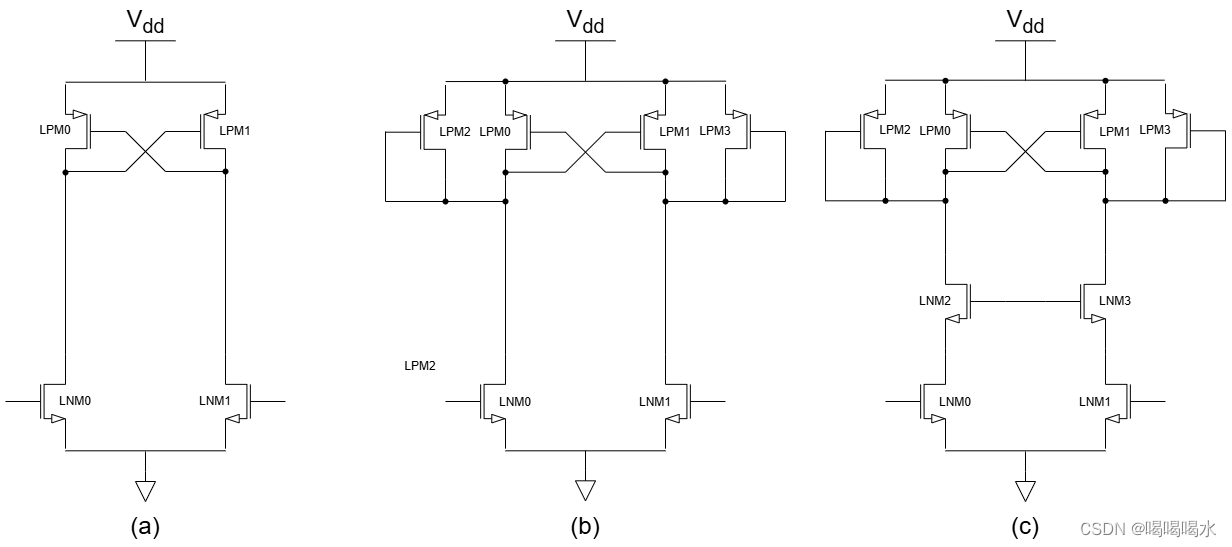

数字信号的电源域和模拟信号一般不同,以TSMC28nm为例,数字为0.9V电压,模拟为1.8V,因此需要level-shifter电路进行电源域转换,如下图所示,传统的differential cascade voltage switch(DCVS)结构level-shifter电路如(a)所示。为了保证锁死的pmos交叉对管LPM0、LPM1能迅速反转,pmos的尺寸要尽可能小于nmos(LNM0、LNM1)尺寸,但这也限制了pmos交叉对管的锁定速度,即难以通过高速信号。(b)电路增加了pmos diod LPM2和LPM3,可以加快锁定速度,因此更能适应高速信号。由于nmos管LNM0和LNM1 gate端是数字电压域的电压,使用的是薄栅的lvt管,其他管都是厚栅的hvt或者标准的svt管,因此nmos管有过压风险。(c)电路增加了nmos cascode管LNM2和LNM3承担一部分电压,减小LNM0和LNM1的Vds电压。

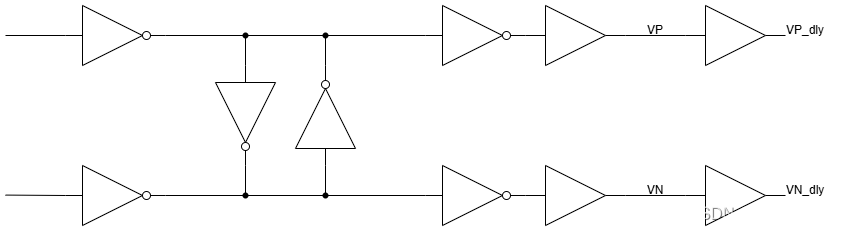

LVDS主体电路接收的VP、VN差分信号需要比较好的同步性,level-shifter电路输出后,需要buffer chain电路进行同步,如下图,可以通过增加latch电路实现,同时buffer中差分两路反相器的的尺寸逐级增大,提高驱动能力。

到目前为止,我们可以获得一个完整的lvds电路了。对于更高速的信号,如何保证lvds电路能继续工作呢?限制高速信号的瓶颈主要是OUT_P和OUT_N电压的反转速度,如果能够让上升下降沿更陡峭,则可以承受更高的信号频率,由于寄生电容的存在,提高速度一般可以简单的通过提高功耗来实现,即需要更大的电流才能保证电容充放电速度更快。但电流和电阻的乘积决定了差分电压幅度,不能随意更改,因此要想办法仅在信号上升下降沿时短暂增大电流,这对功耗增加也比较小。预加重Pre-emphasis电路就是起到这个作用。如下图:

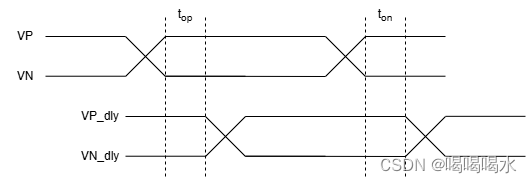

与LVDS电路基本相同,只不过开关mos管增加了一倍。需要VP、VN的delay信号VP_dly、VN_dly参与作用于新增加的EPM3、EPM4、ENM3、ENM4 mos管,关系如下图。

因此,仅在top的时间内,给OUT_P的上升沿提供更多电流,在ton时间内给OUT_N的上升沿提供电流,其他时间内都是关闭的。

最终的主体电路如下图所示:

最后放一些论文供大家参考:

- Design of LVDS Transmitter with SLVDS mode for Low Power Applications in 55nm CMOS Technology, 2018.

- Characterization of an LVDS Link in 28 nm CMOS for Multi-Purpose Pattern Recognition, 2018.

- Design of LVDS Driver and Receiver in 28 nm CMOS Technology for Associative Memories, 2017.

- Low power LVDS Transmitter Design and Analysis, 201

- LVDS Driver Design for high Speed Serial Link in 0.13um CMOS Technology, 2011.

1181

1181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?