PCIe的历史

PCIe是在PCI(Peripheral Component Interconnect)的基础上发展而来的。而PCI则是Intel在1992年提出的一套总线协议,并召集其它的小伙伴组成了名为 PCI-SIG (PCI Special Interest Group)(PCI 特殊兴趣组)的企业联盟。 这个组织就负责PCI和其继承者们(PCI-X和PCIe的标准制定和推广)。

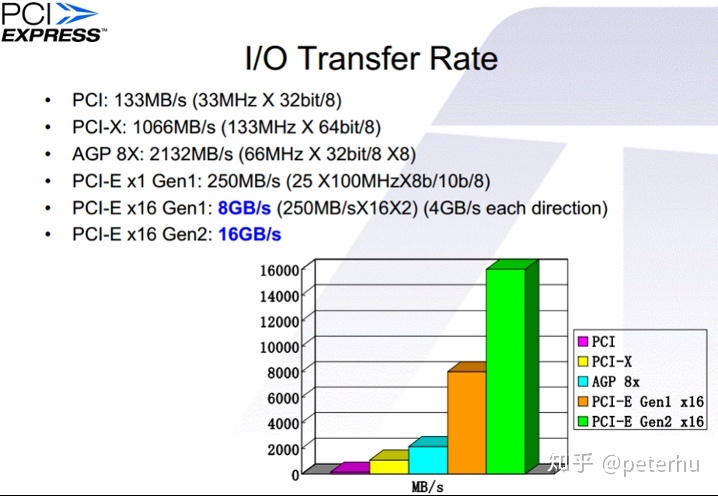

PCI的提出是为了解决当时的ISA/EISA,MCA,VLB等总线速度太慢,接口混乱不统一而提出的,因为它的统一和开放,PCI获得了厂商的欢迎和支持,各种PCI设备应运而生丰富了PC的生态。虽然PCI总线获得了巨大的成功,但是随着CPU主频的不断提高,PCI总线的带宽越来越难以满足要求。PCI总线不断的升级从32位/33MHz扩展到64位/64MHz,PCI-X甚至提升到了533MHz,最大理论带宽为4263MB。但是仍然无法解决其体系结构中存在的一些先天不足:

- PCI是共享总线,总线上的所有设备必须共享带宽,另外总线协议还有一些开销,虽然64位/64MHz理论上可以提供最大带宽为532MB,但是实际可以利用的数据带宽远低于峰值。

- PCI总线是并行的,它通过提高总线频率和位宽的方式增加传输带宽,但是这种方式的性价比比较低,因为位宽的增加需要更多的芯片管脚,从而导致64位的芯片价格远高于32位,另外在主板设计的时候也需要更多层的PCB实现64位芯片接口,增加成本和布线 难度;而且因为频率和位宽的增加带来了信号完整性的问题,也影响了总线的负载能力。比如33MHz的总线可以驱动10个负载,66MHz的总线最多只能渡情4个负载。

- PCI总线并没有考虑服务质量QoS,因为PCI总线是并行的主从式的总线,总线上的设备只能轮流使用PCI总线,当一个设备长期占用总线时将阻止其他设备对总线的使用但是有些实时的设备如数据采集卡,音频或者视频的应用需要额定的带宽,因此就没法得0以 满足。

PCIe如何解决PCI体系结构存在的问题的呢?

- PCIe使用了高速差分总线端到端的连接方式替代并行总线,与并行总线相比高速差分信号可以使用更高的时钟频率,而且更少的信号线实现之前需要更多的芯片管脚才能实现的总线带宽,而且与单端信号相比差分信号的抗干扰能力更强。

- PCIe使用了网络通信中使用的技术如基于多种数据路由方式,报文数据传送,以及Traffic class和virtual channel结束数据传输过程中的QoS问题。

- PCIe的链路可以由多条Lane组成,换句话来说它的性能可扩展。可以像搭积木一样增加Lane或者减少Lane的组合来提高性能。

- PCIe总线在系统软件编程上和PCI总线兼容,绝大多数的PCI总线事务都被PCIe总线保留,PCI设备的配置空间也被PCIe继承。

PCIe总线基础

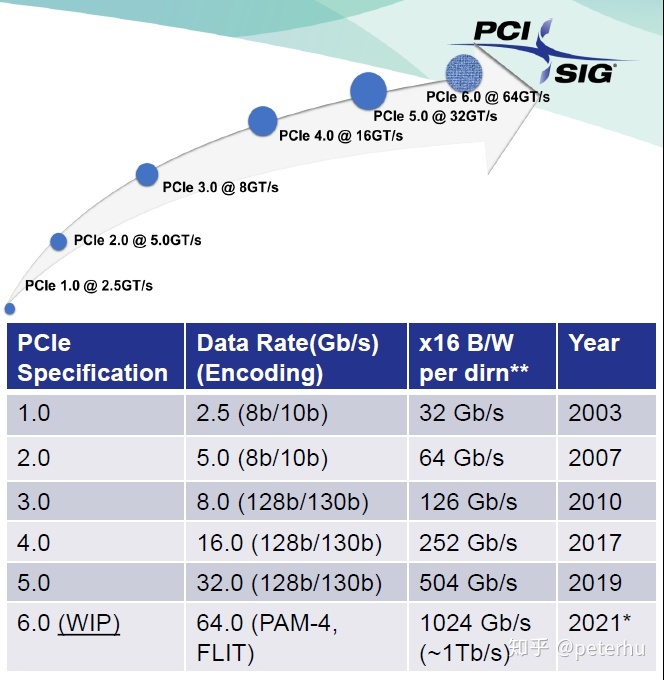

PCIe 从2003年的1.0版本开始到现在的6.0经历了数次更新,速度从2.5GT/s提升到了65GT/s。

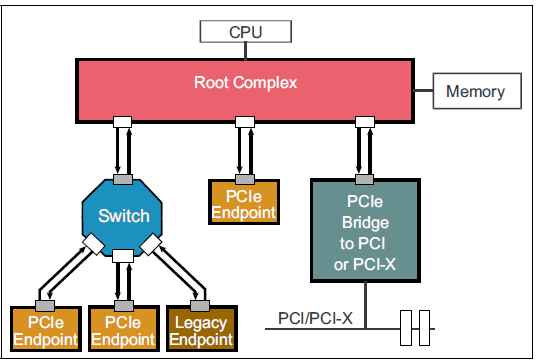

PCIe采用了端到端的全双工的传输设计,基于数据包的传输,设备之间通过link相连,link支持1到32个通道(lane)。

本文介绍了PCIe(Peripheral Component Interconnect Express)的发展历程,从PCI的局限性出发,阐述了PCIe如何通过高速差分信号、全双工传输和链路扩展来解决带宽和性能问题。内容涵盖了PCIe的结构、层次、总线频率、带宽、拓扑以及软件编程接口,如配置空间和枚举过程。

本文介绍了PCIe(Peripheral Component Interconnect Express)的发展历程,从PCI的局限性出发,阐述了PCIe如何通过高速差分信号、全双工传输和链路扩展来解决带宽和性能问题。内容涵盖了PCIe的结构、层次、总线频率、带宽、拓扑以及软件编程接口,如配置空间和枚举过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4805

4805

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?