1. 介绍

SPI是一种主从的通讯接口,主机一般是MCU,从机可以是各种外设驱动芯片(也可以是MCU)。通过片选信号的激活,主机可以实现和不同从机之间的QSPI通讯。=

Queued Synchronous Peripheral Interface (QSPI),此处的Q是指Queued (队列),内部自带FIFO,需要注意此处的QSPI并不是Standard SPI里面的四线SPI(Qual SPI)。

具体可参考文章:SPI总结

2. Feature List

- 支持全双工、半双工、单工

- 支持四线、三线(缺片选)模式,半双工、单工模式下,仅两个线(时钟、数据线)

- 支持灵活的数据格式,数据位数2~32bit可编程(加奇偶校验:3到33位);移位方向、时钟极性、相位可编程

- 支持Tx\Rx,错误状态(接收、波特率、发送错误、奇偶校验错误),传输状态(帧的开始或结束…)中断

- 支持DMA

- 硬件支持奇偶校验:奇校验;偶校验;无校验位

- 从模式下有7个从机片选输入SLSIB…H;

- 主模式下有16个从机片选输出SLSO[15:0](主模式下最多可挂在16路从机)

- Master模式下输出片选极性可配置(高 or 低电平有效)

- Loop-Back mode(回环模式)

- 高速输入捕获(HSIC)(部分型号没有该模块,具体见Part1手册,46页)

- 最高通信速率50Mbps(仅部分QSPI支持,实测使用普通引脚的SPI最高20Mbps,大于20Mbps后需要使用LVDS引脚)

3. 概述

3.1 QSPI框图

3.2 操作模式

IP本身不区分全双工、半工、单工操作模式,半工和单工都是通过外部连线进行实现。

Ifx QSPI半双工实现方式与其他SPI半双工实现不太一样,普通SPI直接将MTSR和MRST在芯片内部合并为同一个Pin输入输出,而Ifx QSPI的仅部分的QSPI可以合并,大部分半双模式下都需要外部短接来实现。具体实现方式如下

Master与Slave的MTSR、MRST四个引脚全部连接,主、从的发送端都设置为开漏输出,总线外接上拉电阻,利用“线与”特性完成数据传输。

- Master发,Slave收时:Slave会往DATAENTRY写0xFF,也就是Slave端的MRST会一直发送0xFF,总线处于“线与”状态,所以Slave收到的数据就是Master发送的数据

- Master收,Slave发时:同上

根据Pin映射,可以分为两种连接方式

1、使用内部连接(对应半双工图中实线部分)

Ifx的内部连接只针对QSPI0\1设计了,其他几个QSPI未提供这样的功能,Mater和Slave的发送都必须配置为“开漏输出”,否则会烧坏GPIO,Master的数据数据采用MRSTA引脚输入(配置PISEL.MRIS = 0即可)

由于两个输出都设置为开漏输出,所以总线需要接上拉电阻才能正常输出高电平,上拉电阻可以通过外部连接的方式给入,也可以同时设置主从的数据输入引脚为上拉输入。

2、使用外部连接(对应半双工图中虚线部分)

Master和Slave的发送接收都连在一起(四个Pin都连到一根总线上),Mater和Slave的发送都配置为“开漏输出”。

TC37x LFBGA-292引脚统计如下:

- 图中数字1表示对应Pin支持QSPI的某个功能,例如QSPI的P20.12行的1,表示该引脚支持Mater模式的输出(MTSR)、Master下的输入(MRSTA)和Slave模式下的输出(MRST)。

- 仅黄色背景的两个引脚在半双工模式下可以走内部直接连接,不用额外占用其他引脚

3.3 三线模式

缺少片选信号,仅限定一对一通信。

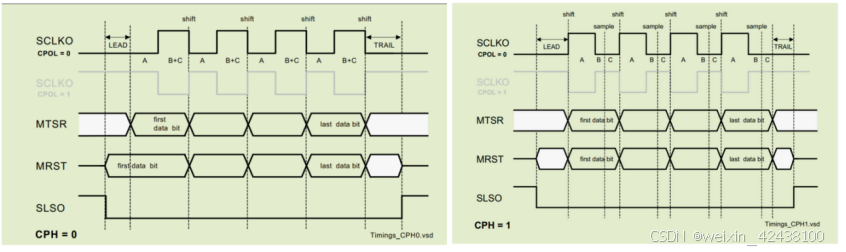

3.4 时钟极性和时钟相位

CPH: 控制时钟相位

CPOL: 控制时钟极性

4. Master模式

4.1 状态机

Master模式下除发送数据以外,还需要提供串行时钟和片选信号。

一帧QSPI信号包含5个阶段:空闲延时、前置延时、数据阶段、尾随延时和一个可选的等待阶段,其中空闲延时阶段分为空闲A与空闲B。

相应时间计算公式如下:

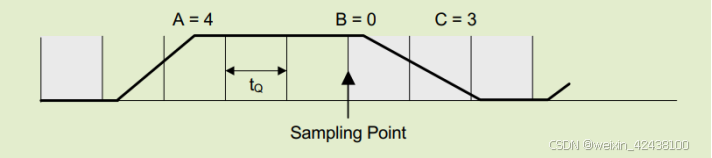

4.2 采样点

类似CAN协议,此处可以通过配置ABC三个参数偏移采样点,一般普通的SPI,则使用其中一个边沿采样数据。

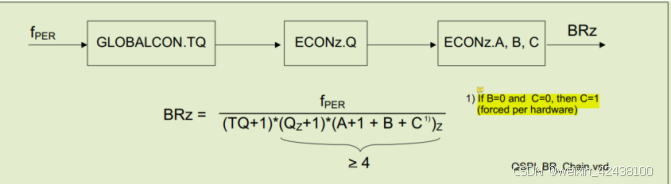

4.3 波特率

QSPI时钟除以大于4的整数,此处fPER时钟为200Mhz,故fSCLK时钟最大50Mhz(QSPI的时钟线)

计算公式如下:

备注:

1、QSPI模块有两个时钟输入,一个是fSPB用来驱动寄存器读写,一个fPER,用来生成QSPI波特率时钟。

2、时钟可参考(CCU输出时钟命名为fQSPI):Clocking System

4.4 通信模式

所有模式总结:

注意:用户并不能直接操作控制寄存器和移位寄存器的,通过其他接口进行间接操作。

- 发送数据时,用户数据都是先写入xxx_ENTRY寄存器中,硬件自动搬运到Tx FIFO中,其中传输后,硬件在从FIFO中搬配置到配置寄存器(BACON)或搬数据到移位寄存器中。

- 读取数据时,将移位寄存器的数据或状态寄存器(STATUS)内容搬到Rx FIFO中,用户通过RX_EXIT寄存器进行读取。

4.4.1 短数据模式

以bit为单位传输,一次可传输2~32bit数据,每次传输前都需要先写一次配置在写数据。配置中BACON.BYTE固定为0,BACON.LAST = 1固定为1

4.4.2 长数据模式

以Byte为单位传输,一次可传输2~32Byte数据,此处框图只是示意图,实际写一个配置后,后续最大可写入8个DATA块,一个DATA块最大32bit。

配置中BACON.BYTE = 1,BACON.LAST = 1

备注:代码中限定一个配置之后,最大跟4个DATA,可能是因为FIFO的深度为4导致,实测跟8个也能正常通信。

4.4.3 短连续模式

在短数据的基础上,传输多个短数据块,只需要在首尾各写一次配置。

第一次配置:BACON.BYTE=0,BACON.LAST = 0,开始发起通信

最后一次配置:BACON.BYTE=0,BACON.LAST = 1,在发一笔数据后,结束通信

备注:驱动代码中单独区分了短模式和短连续模式,但IfxQspi_SpiMaster_exchange接口中,会自动根据形参count进行切换,当count为1时,短数据模式,大于1时,短连续模式。

4.4.4 长连续模式

在长数据的基础上,传输多个长数据块,一个配置后面跟多少DATA,由BACON.DL参数决定,前面n-1个配置的LAST = 0,仅最后一次时,将LAST配置为1。

4.4.5 单配置多帧模式

只需要写入一次BACON寄存器值,就可以发送多帧数据,避免连续模式,发送的多个配置。单次传输数据长度最大16bit。

备注:

1、该模式下所有的配置和数据都写到MIX_ENTRY中,根据高16bit数据进行区分,高16bit非0,则认为是配置,否则是数据。

2、实际该模式为短数据模式的扩展,可以看成多个短数据拼接而成,只是数据和配置都往MIX_ENTRY写,数据长度最大16bit而已。

3、传输过程中,若修改其中的配置,,例如BYTE = 1,LAST = 1,会自动切换到长数据模式进行传输。

4.4.6 XXL模式

长数据模式的一种扩展模式,长数据模式最大可传输2 ~ 32byte,使用XLL模式可以传输2~65536byte。

使用方法

设置BACON.DL = 0,,BACON.BYTE = 1,设置XXLCON.XDL位域值(数据传输长度);

另外XXLCON.BYTECOUNT:可以显示剩余需要发送的字节数。

4.4.7 Move Count 模式

可以传输8192个短数据帧。

使用方法:MCCON.MCEN = 1;BACON.BYTE = 0;BACON.LAST = 0;

待传输数据长度通过MC.COUNT设置(1 ~ 8191),MC. MCOUNT显示还剩传输的数据块。

备注:这里的两个中断是路由到User Interrupt。

4.4.8 总结

在Ifx手册中定义了非常多的模式,这些模式都是围绕BYTE、LAST、DL三个参数进行展开的,了解这些参数后,直接操作寄存器也可以完成数据发送,注意BACON配置寄存器都是只读属性的,只能通过BACON_ENTRY或MIX_ENTRY寄存器间接写入。

DL:数据长度,可以是bits也可以是Bytes,由BYTE位控制。当DL非 0时,组成短、短连续、长、长连续模式,等于0时,组合为XXL模式

BYTE:数据传输单位,等于0,DL表示传输多少bits,等于1,DL表示传输多少Bytes

LAST:表示当前配置是否为最后一个配置,如果是,则为配置为1,不是则配置为0。硬件会根据该配置,决定数据发送完成后,是否拉高片选,所有的模式,其实都是围绕该配置进行实现的。例如单配置多帧时,LAST固定为1,每次发送完成后,拉高片选,下次发起传输后,重新拉低片选。

调用Ifx接口,初始化完成后,直接操作寄存器实现长数据传输:

Ifx_QSPI_BACON bcfgVal;

Ifx_QSPI *qspiPtr;

qspiPtr = &MODULE_QSPI2;

printf("QSPI%d longContinue mode test\t", 0);

bcfgVal.B.CS = 1;

bcfgVal.B.DL = 11;

bcfgVal.B.BYTE = 1; /*长数据模式下BYTE = 1 */

bcfgVal.B.MSB = 1;

bcfgVal.B.PARTYP = 0;

bcfgVal.B.TRAIL = 7;

bcfgVal.B.TPRE = 0;

bcfgVal.B.LEAD = 7;

bcfgVal.B.LPRE = 0;

bcfgVal.B.IDLE = 7;

bcfgVal.B.IPRE = 0;

bcfgVal.B.LAST = 0; /* 先发送12byte数据,在发送last = 1命令,结束数据传输 */

qspiPtr->MIXENTRY.U = bcfgVal.U;

qspiPtr->MIXENTRY.U = 0xAA535251;

qspiPtr->MIXENTRY.U = 0xAA535252;

qspiPtr->MIXENTRY.U = 0xAA535253;

Qspi_ldelay();

IfxQspi_read32(qspiPtr, &g_qspi.spiBuffers.spiMasterRxBuffer[0], 3);

bcfgVal.B.DL = 3;

bcfgVal.B.LAST = 1; /* 在发送last = 1命令,结束数据传输 */

qspiPtr->MIXENTRY.U = bcfgVal.U;

qspiPtr->MIXENTRY.U = 0xAA535254;

Qspi_ldelay();

IfxQspi_read32(qspiPtr, &g_qspi.spiBuffers.spiMasterRxBuffer[3], 1);

备注:由于QSPI发送数据的同时也会接收数据到Rx FIFO中,故发送数据时也要考虑将Rx FIFO数据读出,否则会造成Rx FIFO下溢。

5. Slave模式

基本功能与Master一致,在从模式下,模块简单地立即响应外部时钟沿。因此,对leading、trailing、idle延迟、占空比和采样点的设置并不关心,只关心数据长度和波特率分频设置。

注意以下几点即可:

- 从模式下的数据长度设置限制在2 ~ 32位。BACON.BYTE将固定设置为0,Ifx驱动代码中,仅在初始化时写一次BACON,后续不在写配置

- 移位时钟的相位和极性被固定为CPH=1和CPOL=0(根据BACON.CS选择的ECONz (z=0-7)寄存器进行配置)

- 支持波特率错误和尖峰错误检测,在GLOBALCON.AREN = 0的情况下,忽略错误,数据正常发送,配置为1时,若出现错误,Slave发送全1,不接收后续数据。

6. Tx\Rx中断

QSPI TXFIFO与RXFIFO可以配置为单步移动、批量移动、组合移动三种不同的工作模式。

6.1 单步移动模式

目的是保持TXFIFO尽可能满,尽可能写入一个自由的元素来重新填充TXFIFO

TXFIFO中断:软件对TXFIFO写入产生中断,TXFIFO往移位配置寄存器写入数据产生

RXFIFO中断:移位寄存器(或STATUS) 将新元素写入空的RXFIFO时产生,用户通过SPB总线读取时(RXEXIT/RXEXITD)

DMA请求源:软件对TXFIFO写入(写入BACONENTRY/DATAENTRY/MIXENTRY)

6.2 批量移动模式

TXFIFO中断:当FIFO层级低于GLOBALCON1.TXFIFOINT时才产生中断,优点是减少CPU中断次数

RXFIFO中断:当填充级别上升到编程阈值时,就会产生RXFIFO中断(默认配置为0,有多少个数据,进多少次接收中断)

6.3 合并移动模式

TXFIFO中断:结合①②,低于GLOBALCON1.TXFIFOINT时才产生中断,区别是在低于该FIFO时,发送BACON/DATA时也会产生中断。

RXFIFO中断:结合①②,高于GLOBALCON1.RXFIFOINT时才产生中断,区别是在高于该FIFO时,接受到数据也会产生中断。

7. 问题记录

7.1 三线模式

初始化引脚时,不配置CS引脚,参数设置为NULL_PTR,就对应三线模式。

该模式下,从机在时钟上升沿时发送数据,下降沿时接收数据,接收数据个数到达BACON.DL后,停止收发数据,若还收到数据(CLK还有脉冲),则产生波特率错误

7.2 最高波特率测试

最高波特率50Mbps,40Mbps可以逻辑分析仪可以正确解析,但50M无法解析,通过物理波形可以得知,数据传输正确。

无法解析原因:猜测是频率过高,由于线电容影响,导致数据解析异常。

注意事项:20M以上需要使用支持LVDS pad的引脚,否则引脚的物理特性会导致波特率达不到,这里使用QSPI4的P21.1作为时钟输出口

40M测试结果如下:

50M测试结果如下,通过轮廓可以得知数据正确:

发送4个字节的0xf0

发送4个字节的0x55 0xF0 0xF0 0xF0

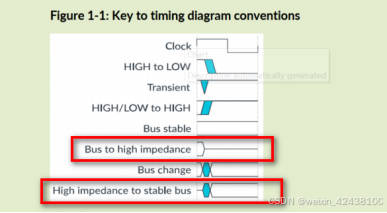

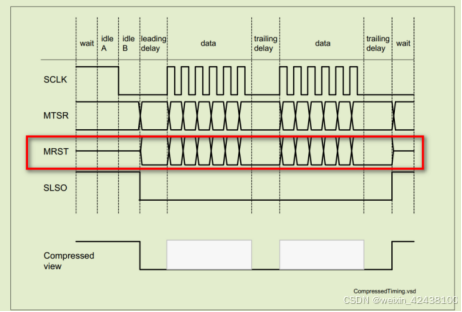

7.3 高阻态

在时序图中,高电平在上,低电平在下,高阻态在中间。

所以,Ifx的MRST引脚在片选无效时,该总线状态为高阻态。

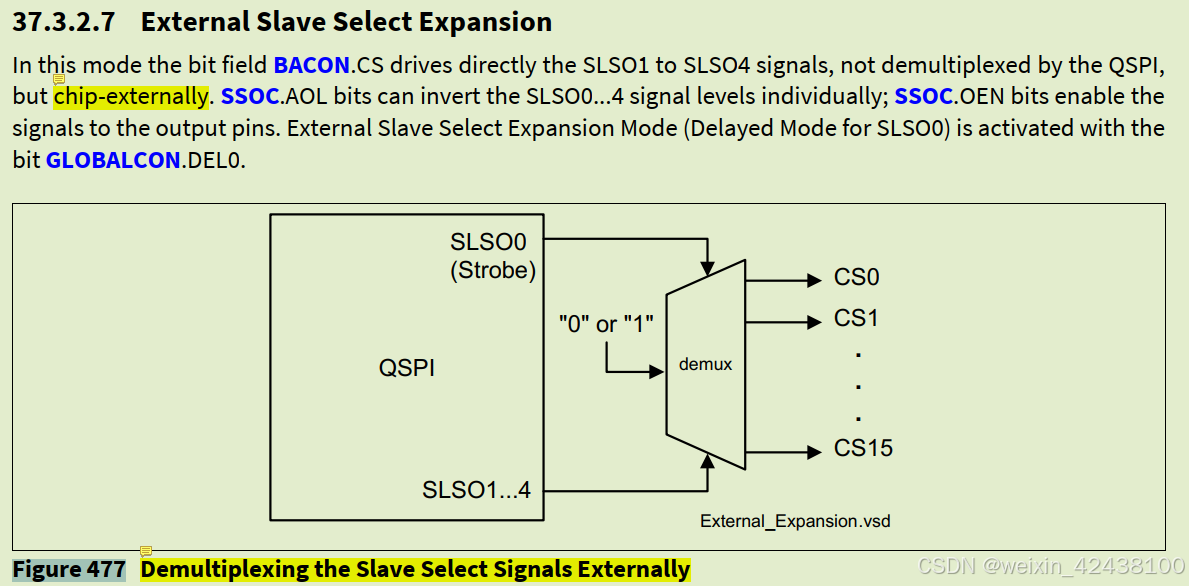

7.4 片选

QSPI输出片选有两种模式(GLOBALCON.DEL0控制),正常模式(DEL0 =0),外部扩展模式(DEL0=1),正常模式下,主机片选通过SLSO0…15输出,扩展模式下,只输出SLSO0…4,其中SLSO1…4输出到外部的数据分配器(4转16),SLSO0输出一个同步信号,选中片选。

注意这里SLSO1…4也可以不接数据分配器,直接接四个不同的从机,并且可以同时选中,达到广播的目的。

外部扩展框图如下:

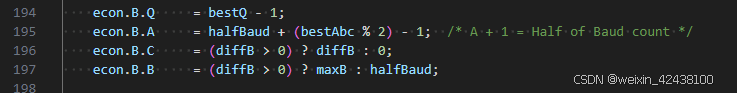

7.5 采样点与占空比

Ifx支持对时钟信号的占空比和采样点进行控制(普通SPI,50%占空比,边沿进行采样),在时钟不对称和环路延时场景下可以提高传输波特率(来源Ifx手册,具体如何提高TBD)。

采样点:B和C之间

占空比:A/(A+B+C) or(B+C)/(A+B+C)

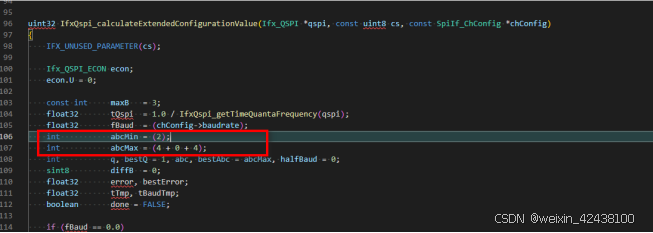

7.6 ABC参数最大、最小为多少?

最小:B\C同时为0时,硬件会把C设置为1,A至少也为1(若A为0,时钟就没有高低电平了)

注意(Qz+1)(A+1+B+C)最小值为4,通过软件去限制,寄存器处未写明相关的要求。

最大值:根据寄存器配置,最大ABC可以取到10,但是Ifx自己的这套算法,如果取到9、10,A计算出来是4,超过了对应位域

注意:TC3xx转int时,是向下取整。

7.7 单配置多帧模式

①单配置模式下什么时候数据传输完毕?不需要发送结束位么

经测试,不需要

②MIXENTRY寄存器是32bit的,这个模式下,高16bit会发送出去么

不会,会通过DL的配置去限制

③如何切换到其他模式

答:单配置多帧模式下,传输过程中可以接收其他配置,如果无效配置,则中止后续数据发送,若配置有效;按照最新的配置进行发送,无论该配置对应是长连续模式,还是短数据模式

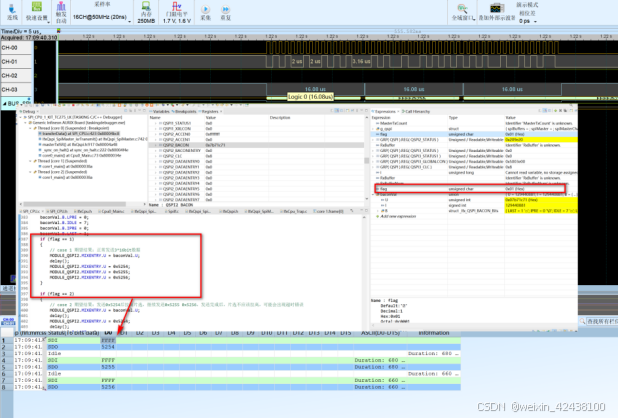

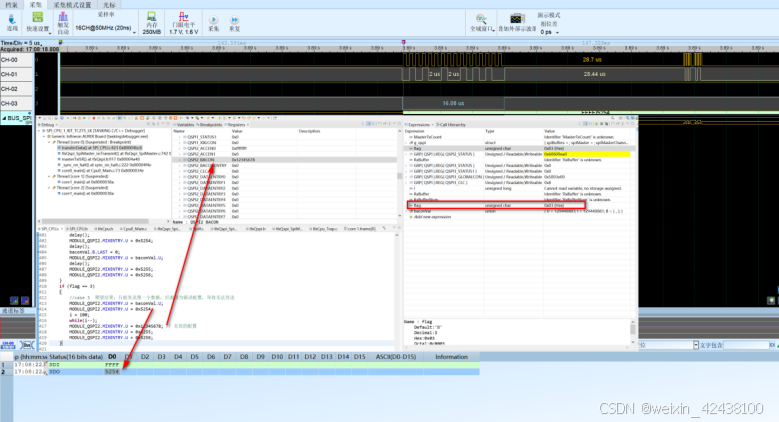

7.7.1 正常使用场景 - last = 1

每发送完一个数据块后,CS会拉起,下一个数据块写入后,正常拉低片选传输,与Ifx框图保持一致。

7.7.2 正常使用场景 - last = 0

相当于使用MIXENTRY实现短连续模式的功能,注意连续短模式下是使用BACON+DATAENTRY实现的,是不支持MIXENTRY的。

由于未发last = 1,所以最终片选未拉低,并出现超时错误。

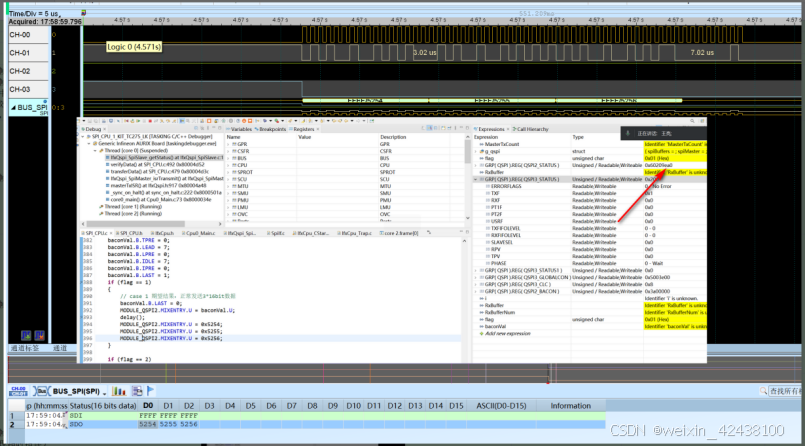

7.7.3 单配置多帧 + 短连续(未发last = 1)

未发last = 1,所以最终片选未拉低,并出现超时错误(正常现象)

7.7.4 单配置多帧 + 短连续(发last = 1)

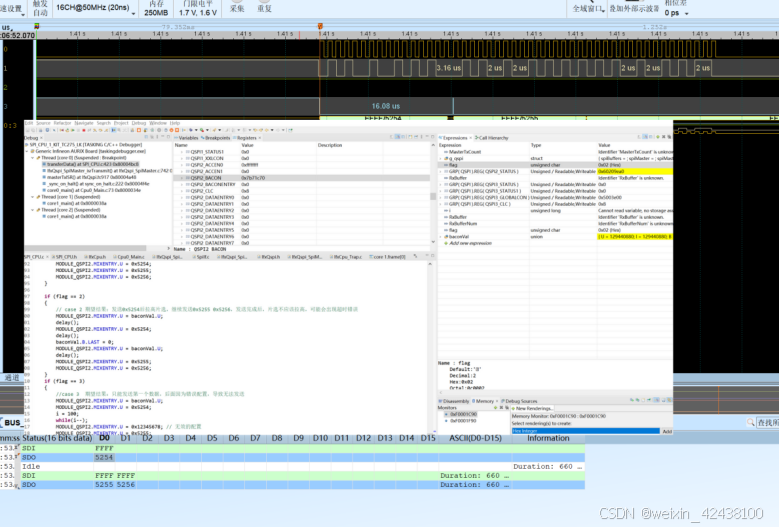

7.7.5 单配置多帧 + 长连续模式

7.7.6 单配置多帧 + 无效的配置

无效配置写入BACON寄存器,后续数据无法发送。

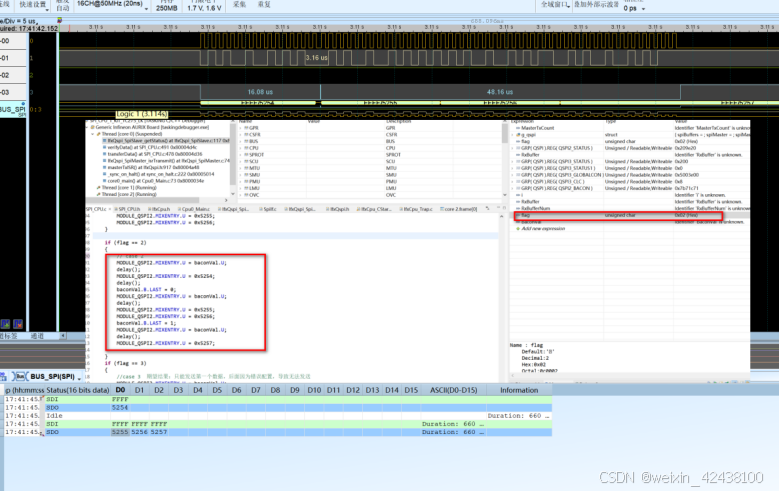

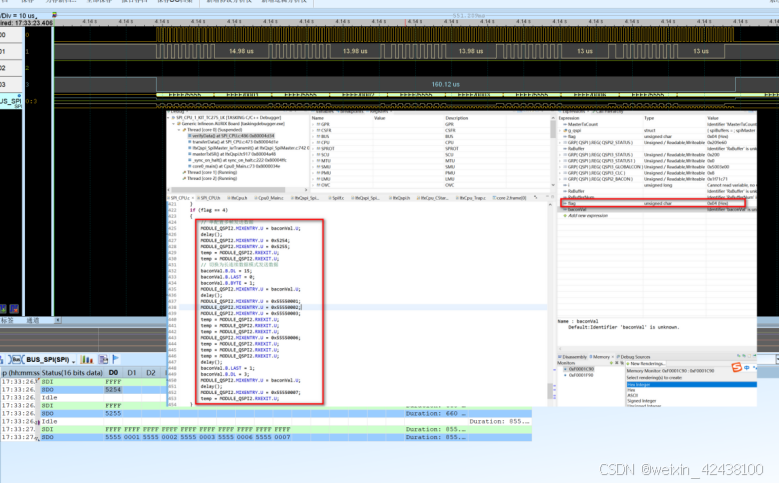

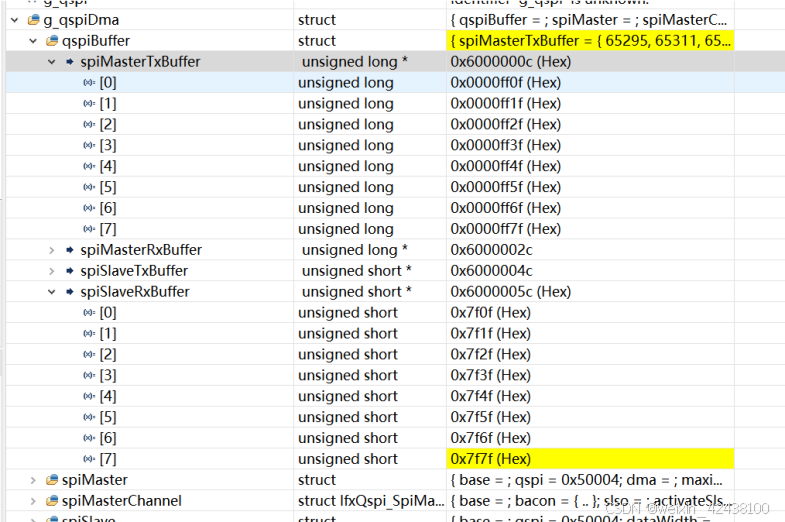

7.7.7 收发8*15bit数据测试

数据DL设置为14,(传输15bit)这里是传输的是bit0~bit14(发送buffer中bit15未发出,所以从机收到的是0x7fxf)

7.8 channelBasedCs功能测试

1、短连续模式下,不使用DMA的情况下,存在写两次BACON的情况,但是对结果无影响

备注:这里写的第一次属于短连续模式的接口,但是由于后面的逻辑未处理,所以导致写了两次。

2、短连续模式下,只有在首尾的时候才写BACON,中间是没有写配置的,所以中间的数据块是沿用了上一次的配置,这里分两种情况,根据第一次LAST写的不同值区分

- LAST = 0:QSPI硬件认为后面的数据块不是最后一个,所以发送完毕后,不会拉高片选(CS中间不会出现尖峰)

- LAST = 1:QSPI硬件认为后面的数据块不最后一个,所以每发完一个数据,都会拉高片选,直到所有的数据发送完毕。

1152

1152

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?