调用IP核实现多数表决器

该文档的MOOC的视频教程

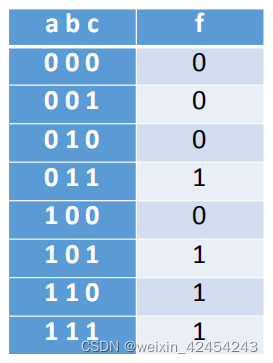

数字电路中译码器三输入的译码器可以实现任意三输入的逻辑函数,所以三变量的多数表决器也可以用译码器实现。

1 使用74x138实现多数表决器的设计

f = ∑abc(3,5,6,7)

2 构建新工程并调用IP核

1.新建一个工程 p_dsbjq_useip

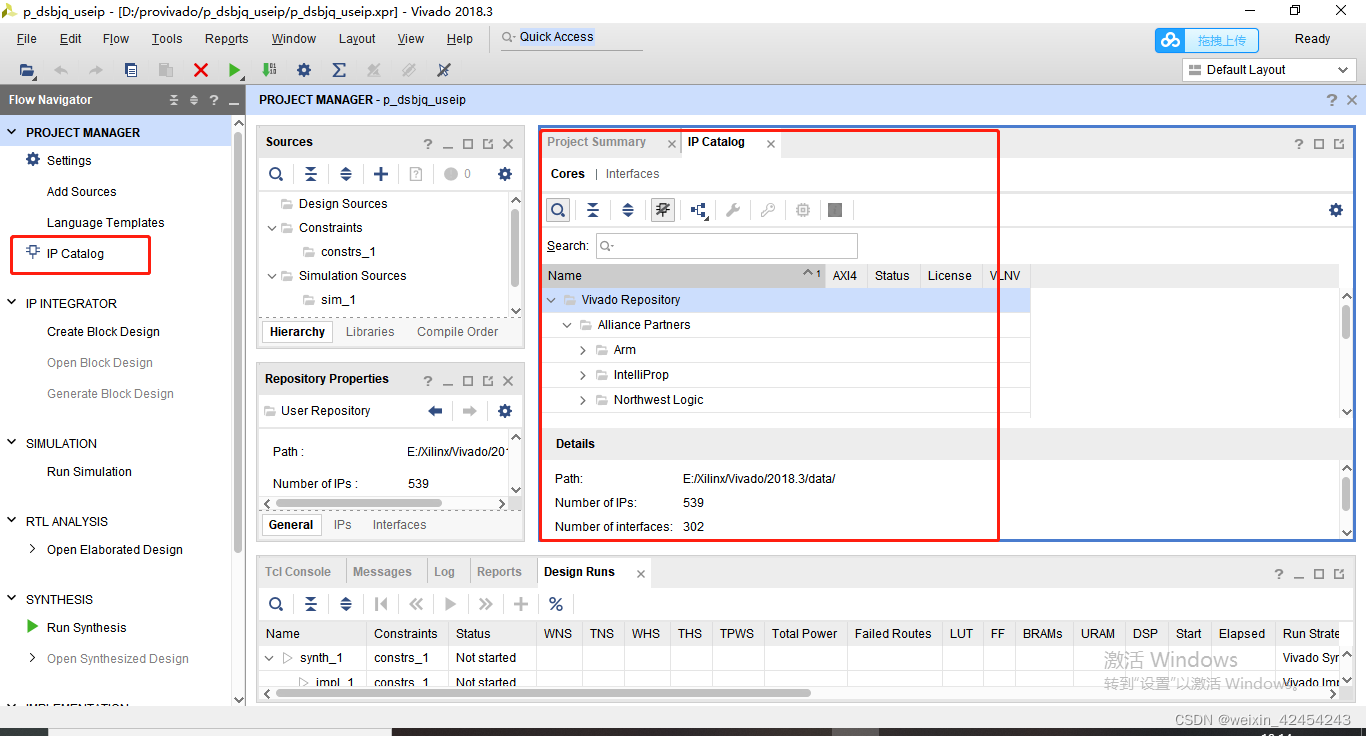

2.点击流程导航下工程项下的IP目录( IP Catalog)

3.在右边的窗口中增加了IP Catalog页框,以树状结构显示当前能够使用的所有IP核。这些IP核是VIVADO自带的,但是并不包含已经设计好的“v74x138”IP核 。

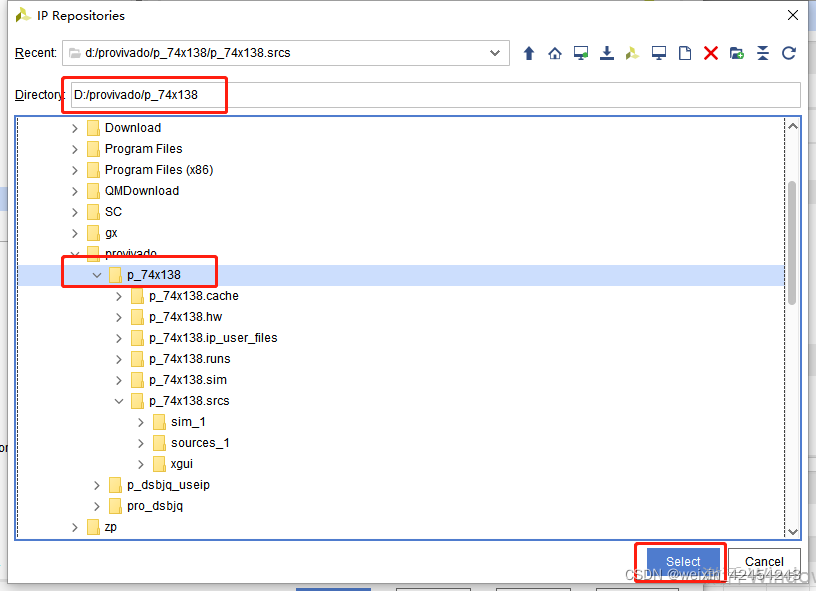

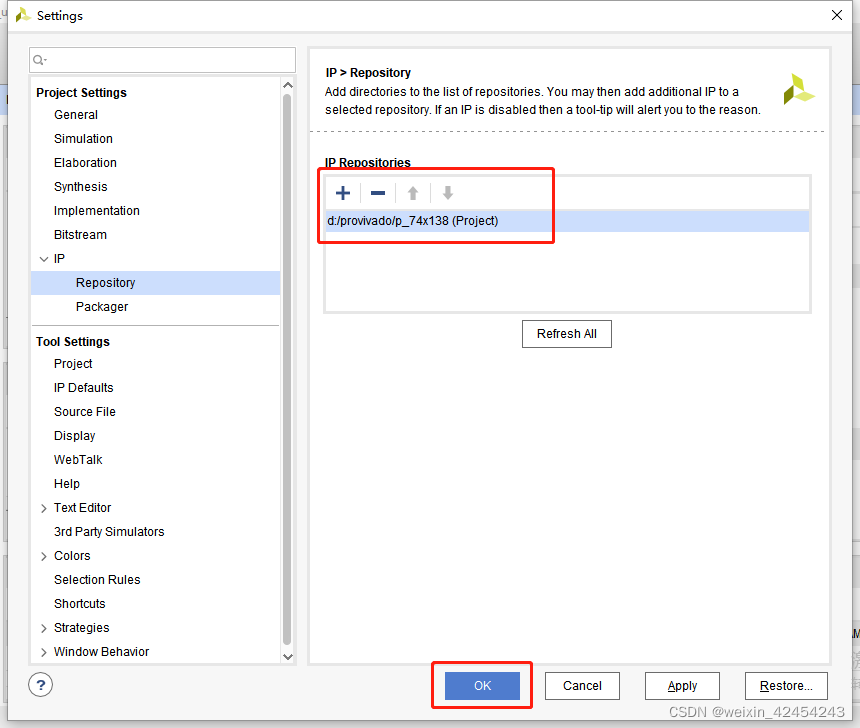

4.点击Settings 在弹出的窗口中选 择点击左侧的IP图标点击库管理(Repository Manager)页框在库管理页框中点击“+”图标增加IP目录

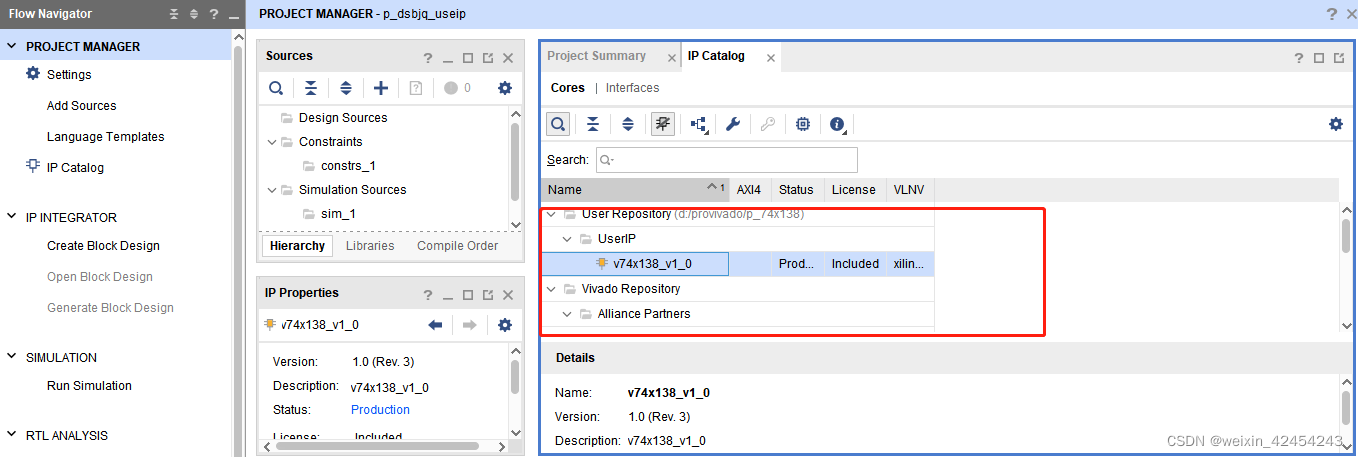

5.选择设计好了的v74x138工程目录,目录被加载进来,有一个IP

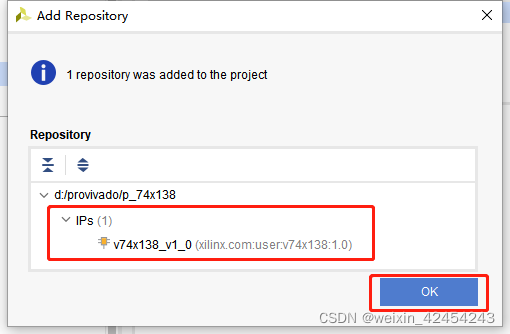

6.此时,就有了v74x138的IP核

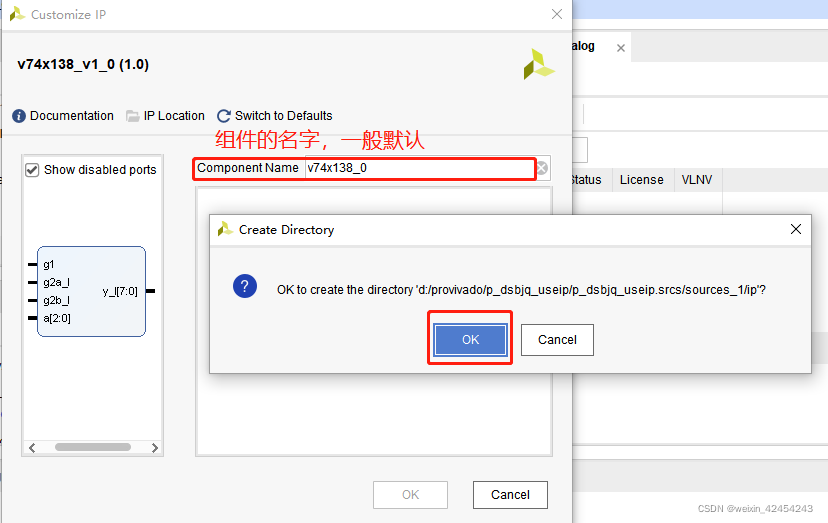

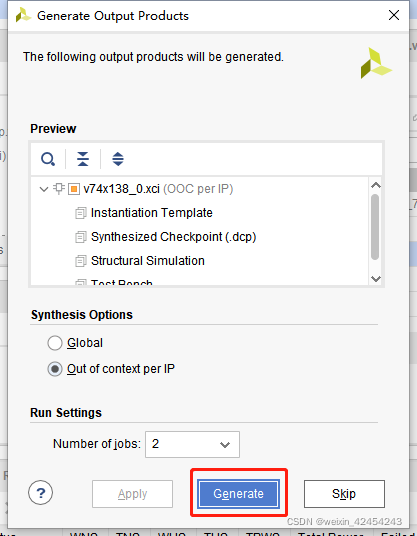

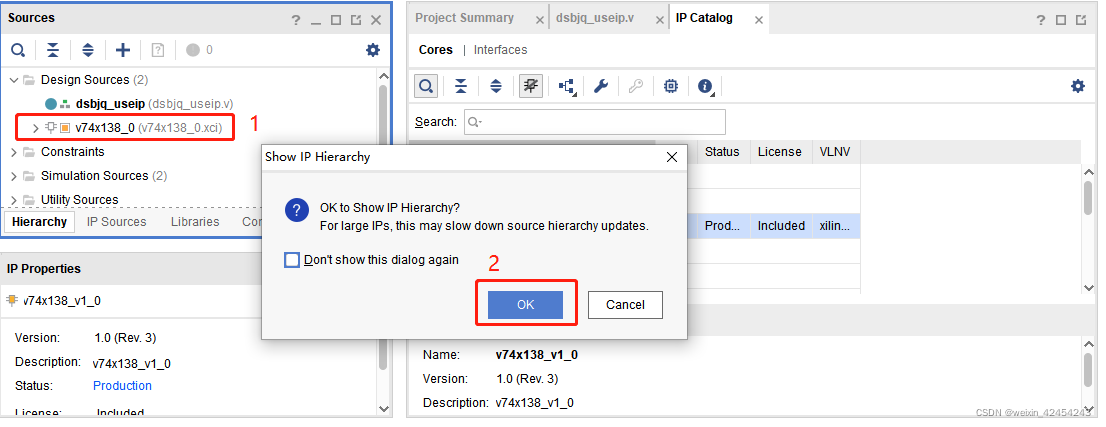

7.新建一个设计文件。接下来我们使用 v74x138IP核。 双击v74x138_v1_0 弹出客户化IP窗口。可以看到该IP核的逻辑符号如图所示。这个窗口可以用来编辑IP实例组件的名称。点击OK实例化IP

8.就可以看到v74x138_v1_0 的IP核下面的源代码,文件是只读的,不能进行编辑

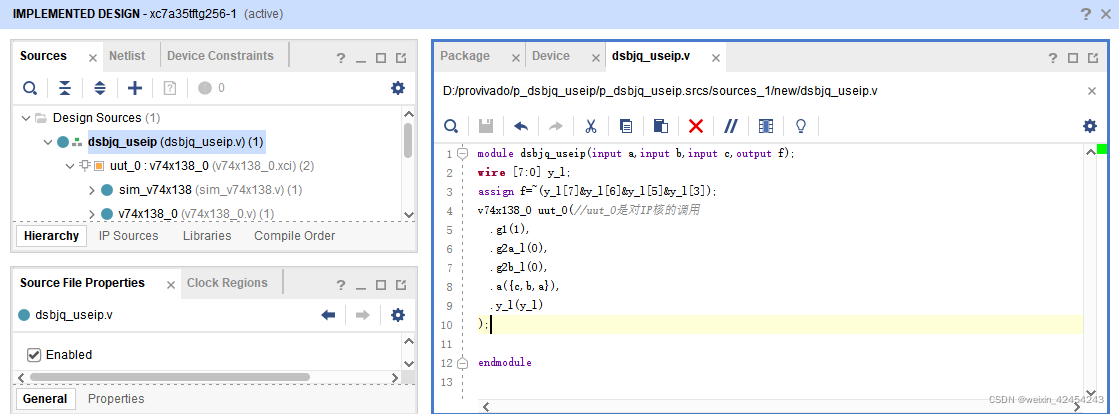

9.在顶层dsbjq_useip.v中调用v74x138_0

module dsbjq_useip(input a,input b,input c,output f);

wire [7:0] y_l;

assign f=~(y_l[7]&y_l[6]&y_l[5]&y_l[3]);

v74x138_0 uut_0(//uut_0是对IP核的调用

.g1(1),

.g2a_l(0),

.g2b_l(0),

.a({c,b,a}),

.y_l(y_l)

);

endmodule

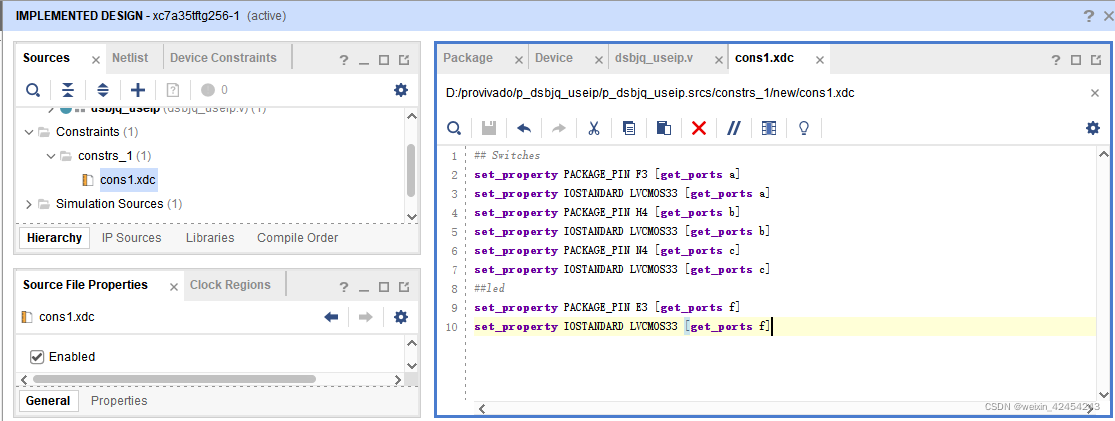

10.约束文件,新建一个约束文件

## Switches

set_property PACKAGE_PIN F3 [get_ports a]

set_property IOSTANDARD LVCMOS33 [get_ports a]

set_property PACKAGE_PIN H4 [get_ports b]

set_property IOSTANDARD LVCMOS33 [get_ports b]

set_property PACKAGE_PIN N4 [get_ports c]

set_property IOSTANDARD LVCMOS33 [get_ports c]

##led

set_property PACKAGE_PIN E3 [get_ports f]

set_property IOSTANDARD LVCMOS33 [get_ports f]

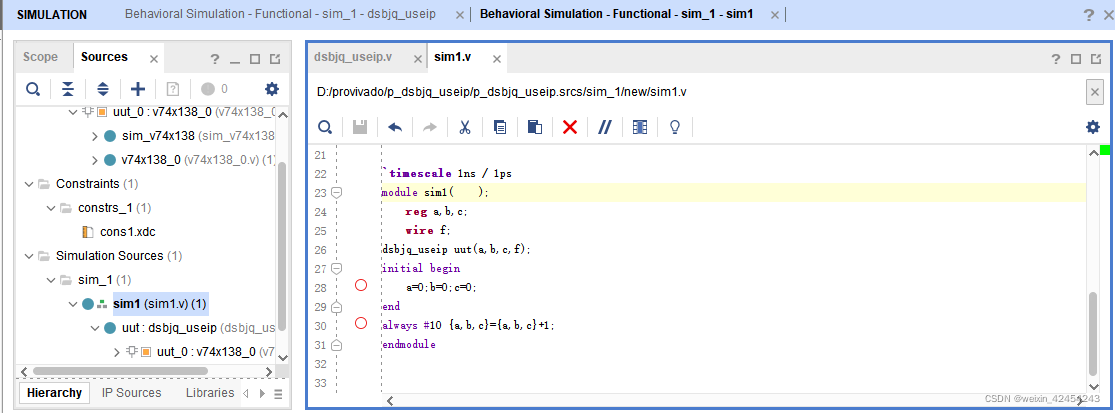

11.仿真文件,新建一个仿真文件

`timescale 1ns / 1ps

module sim1( );

reg a,b,c;

wire f;

dsbjq_useip uut(a,b,c,f);

initial begin

a=0;b=0;c=0;

end

always #10 {a,b,c}={a,b,c}+1;

endmodule

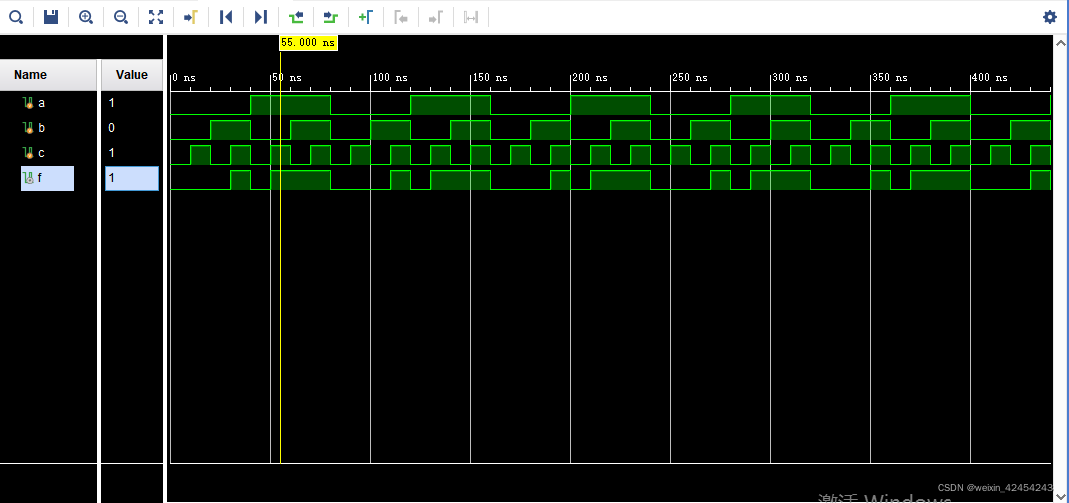

12.先综合,在仿真,仿真结果与3.1节仿真一样

2727

2727

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?