UVM平台中的关键组件

第二节目录

UVM平台的主要组件

创建用户所需的transaction(事务)

创建sequence

创建sequencer

创建driver

创建monitor

创建agent

创建environment

创建testcase

运行仿真

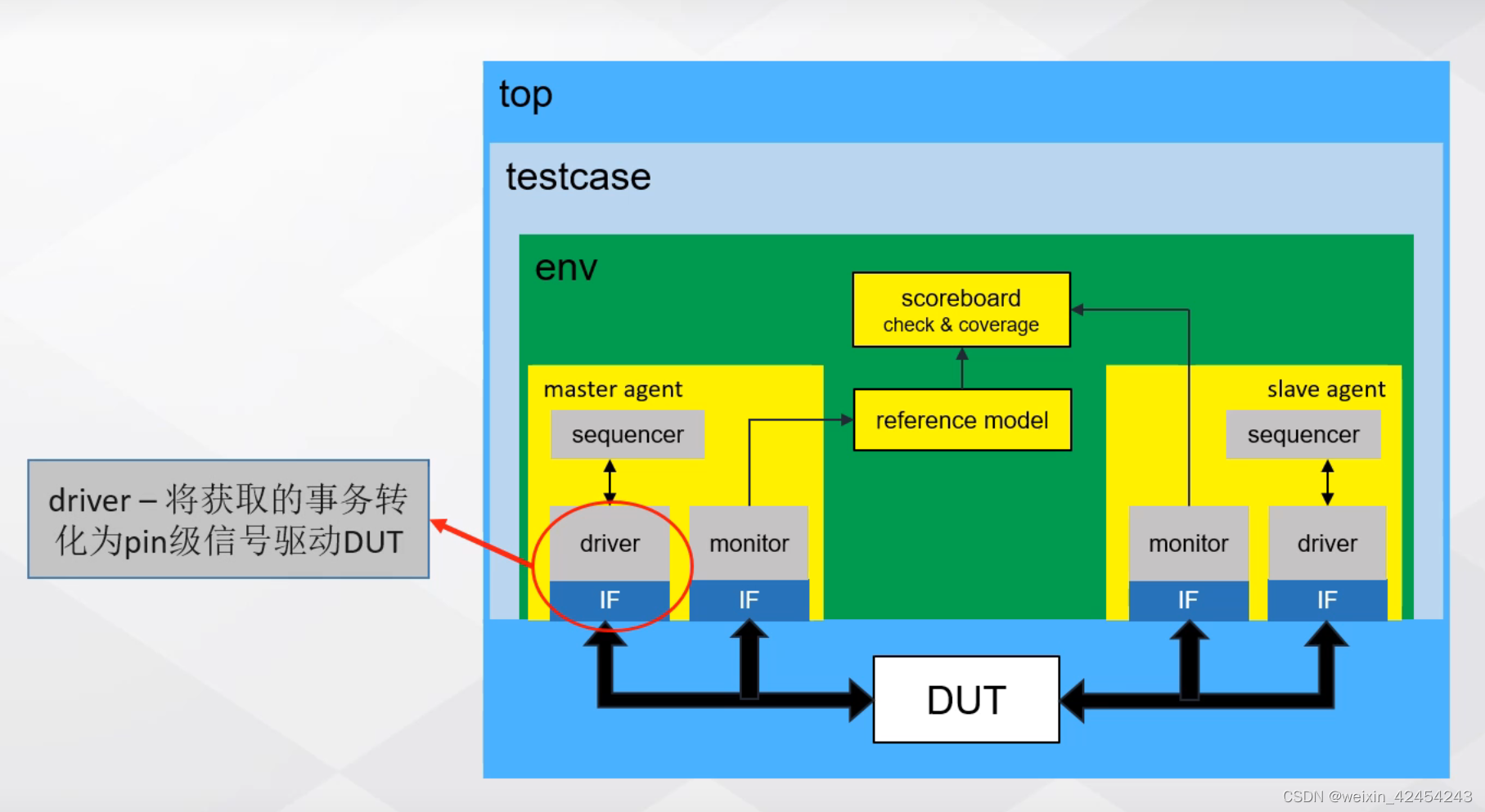

1. driver激励驱动

driver:将接收到的事务,转化为pin级信号,通过接口,驱动到被测设计的端口上

2. sequencer

sequencer:sequencer启动后,会产生事务,将事务转发给driver

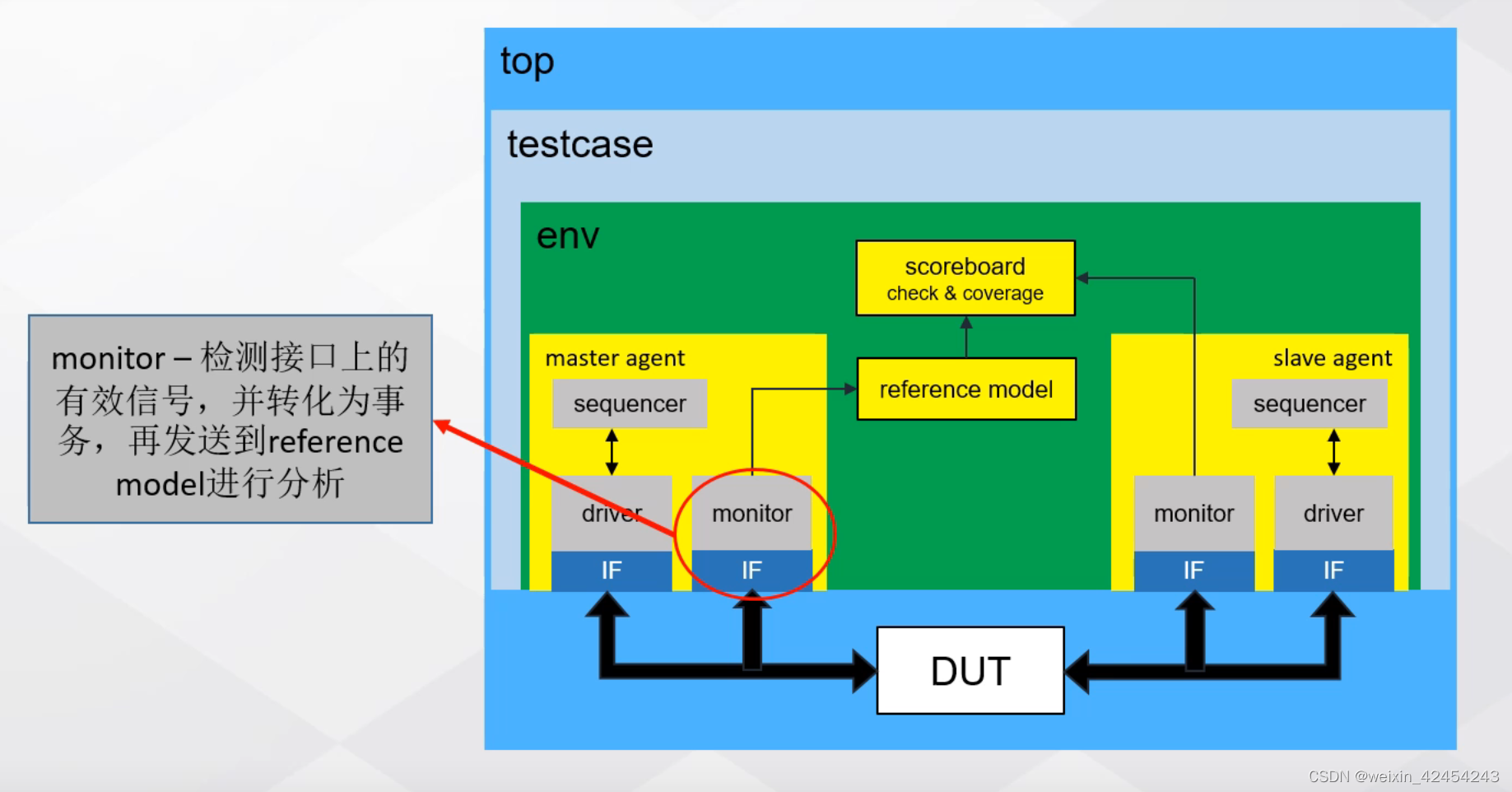

3. monitor

monitor:监视接口上的信号,包括被测设计的输入、输出信号;将获取的pin级信号转化为事务及对象,然后给其他组件进行处理。

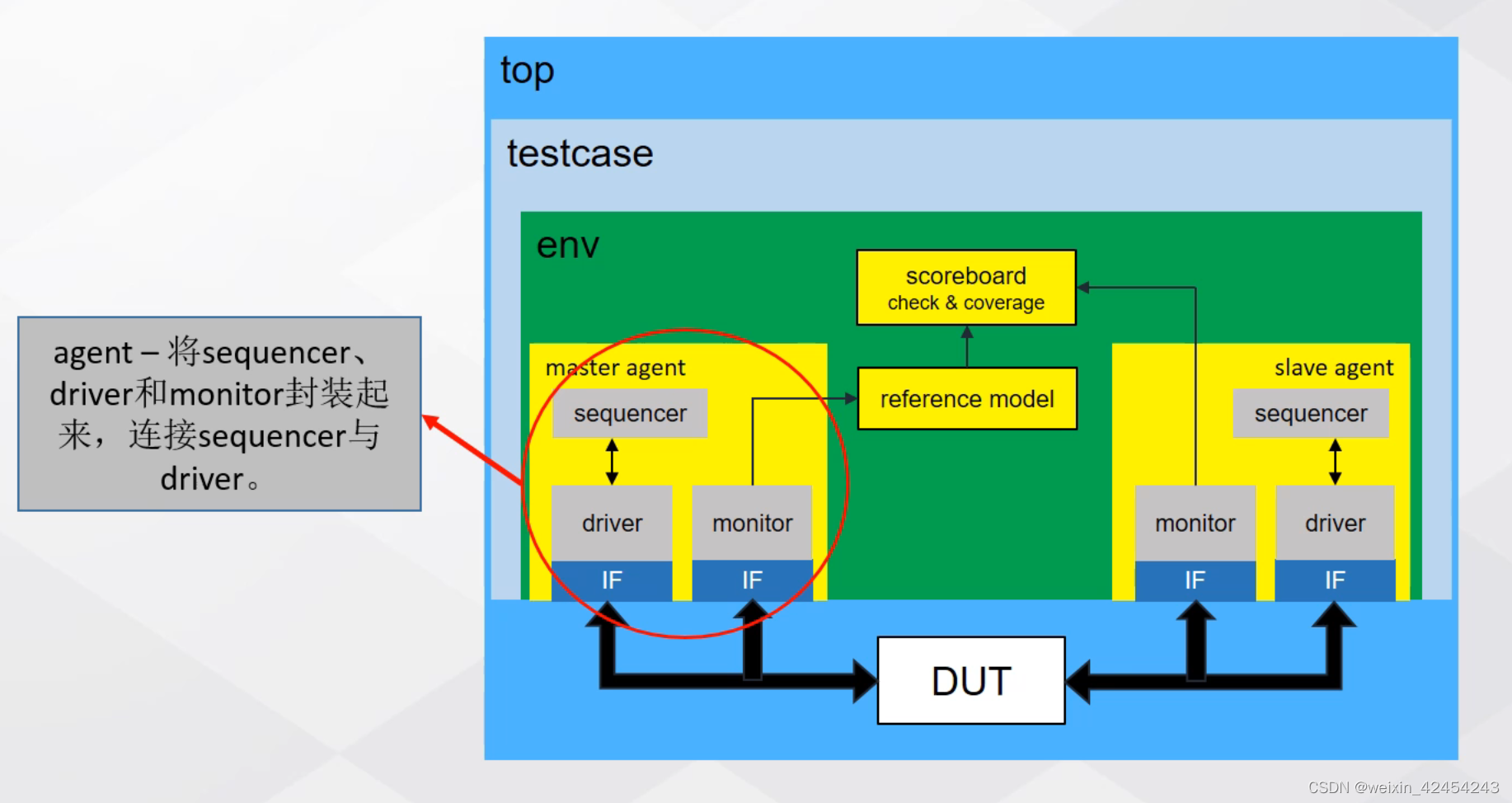

4. agent

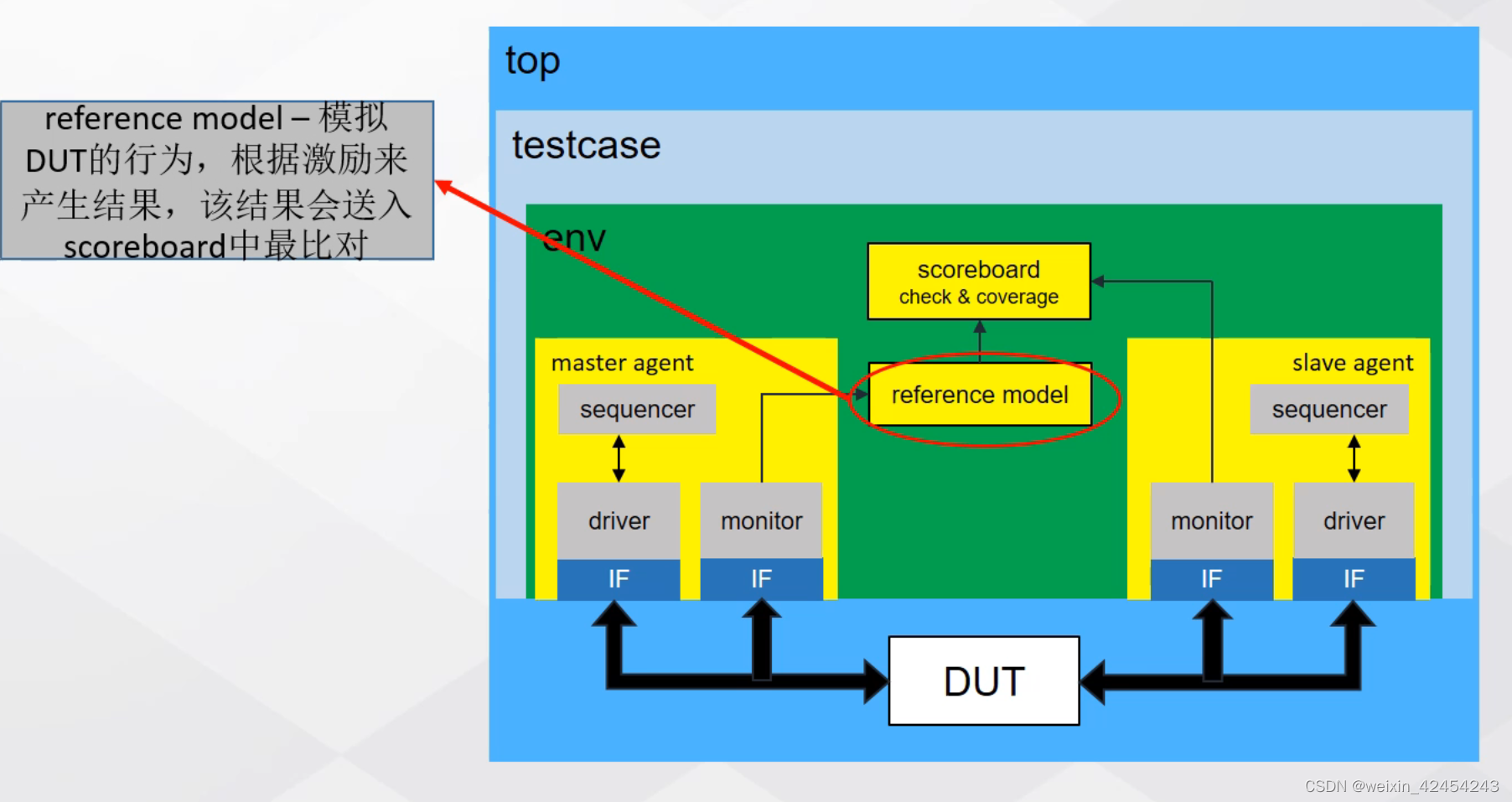

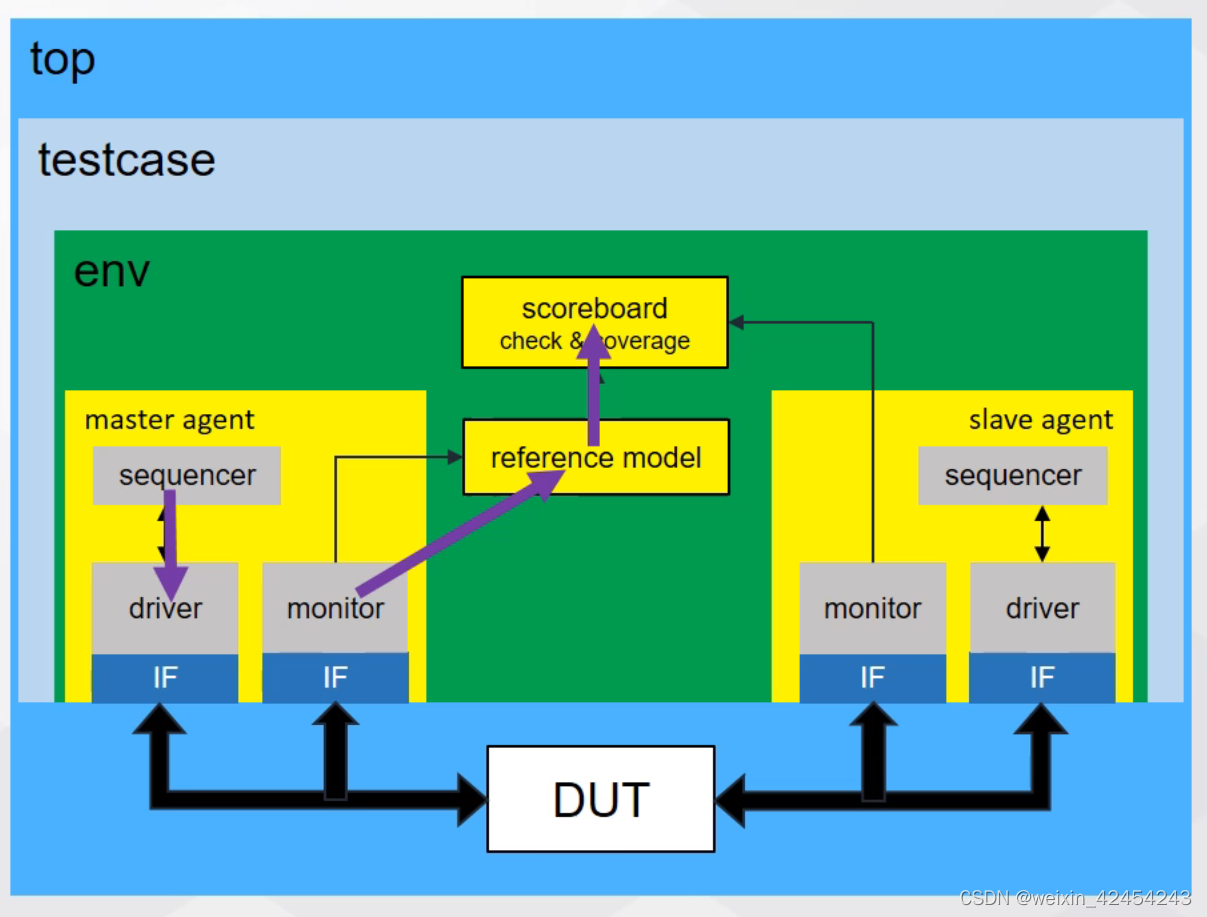

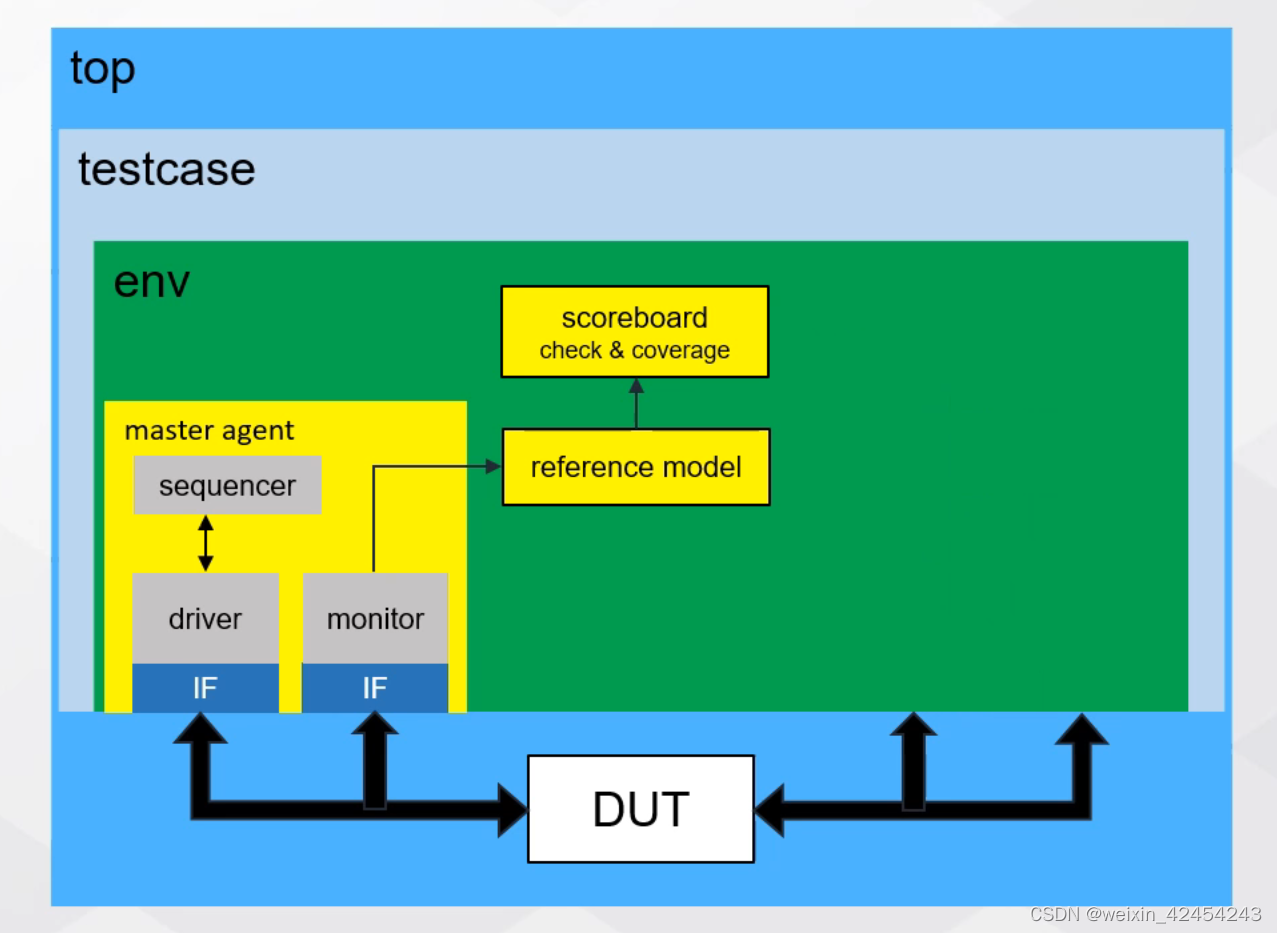

5. reference modle参考模型

reference modle:模拟DUT的功能行为,根据输入的激励产生相应的结果,该结果称为参考值或者期望值。

master agent中的monitor会将DUT的输入收集下来,发送给参考模型,作为参考模型的输入

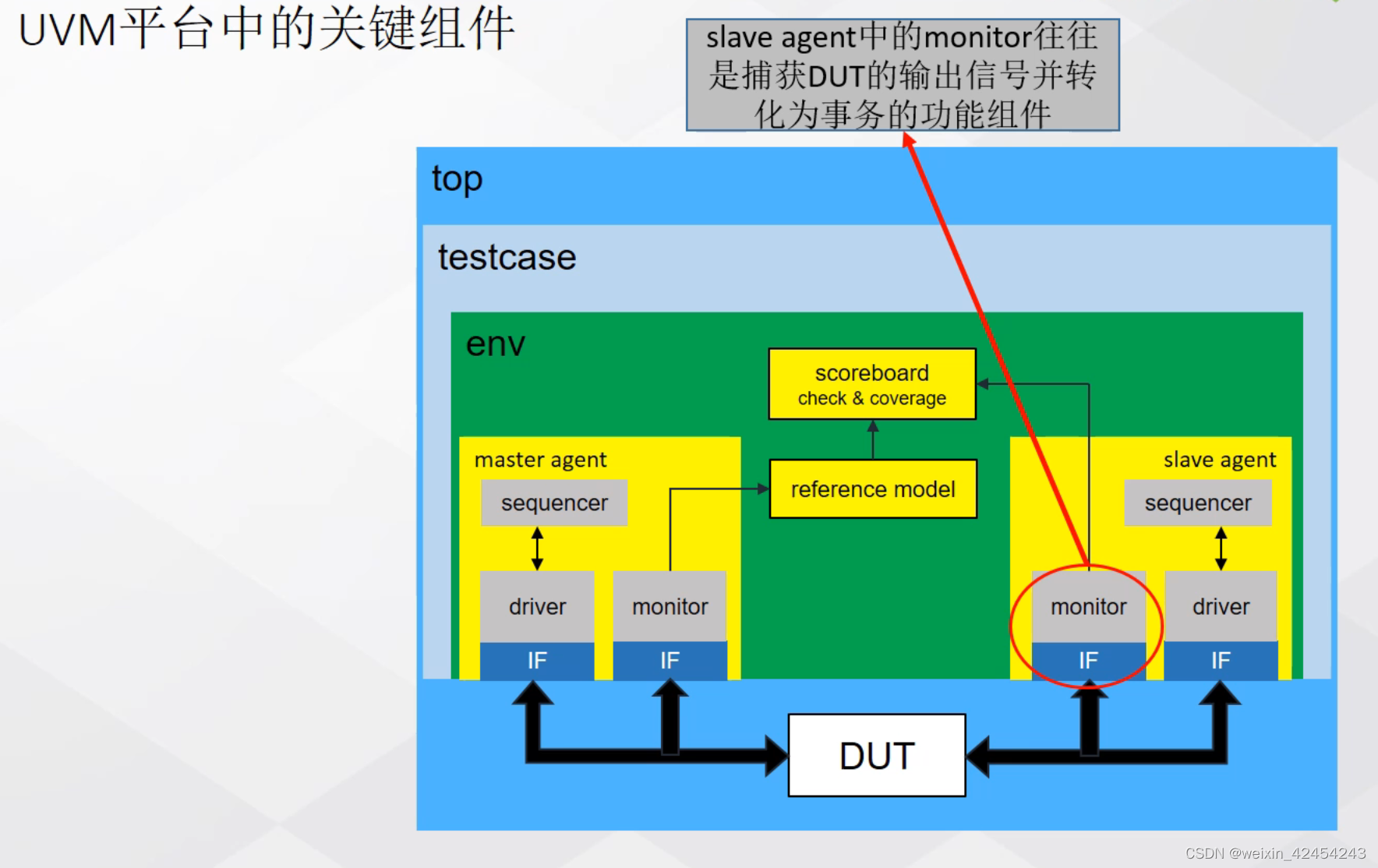

6. slave agent

slave agent中的monitor收集DUT的输出信息,将获取的pin级信号转化为事务及对象,然后发送给其他组件进行分析。

一般情况下,slave agent不需要驱动DUT,只包含monitor。

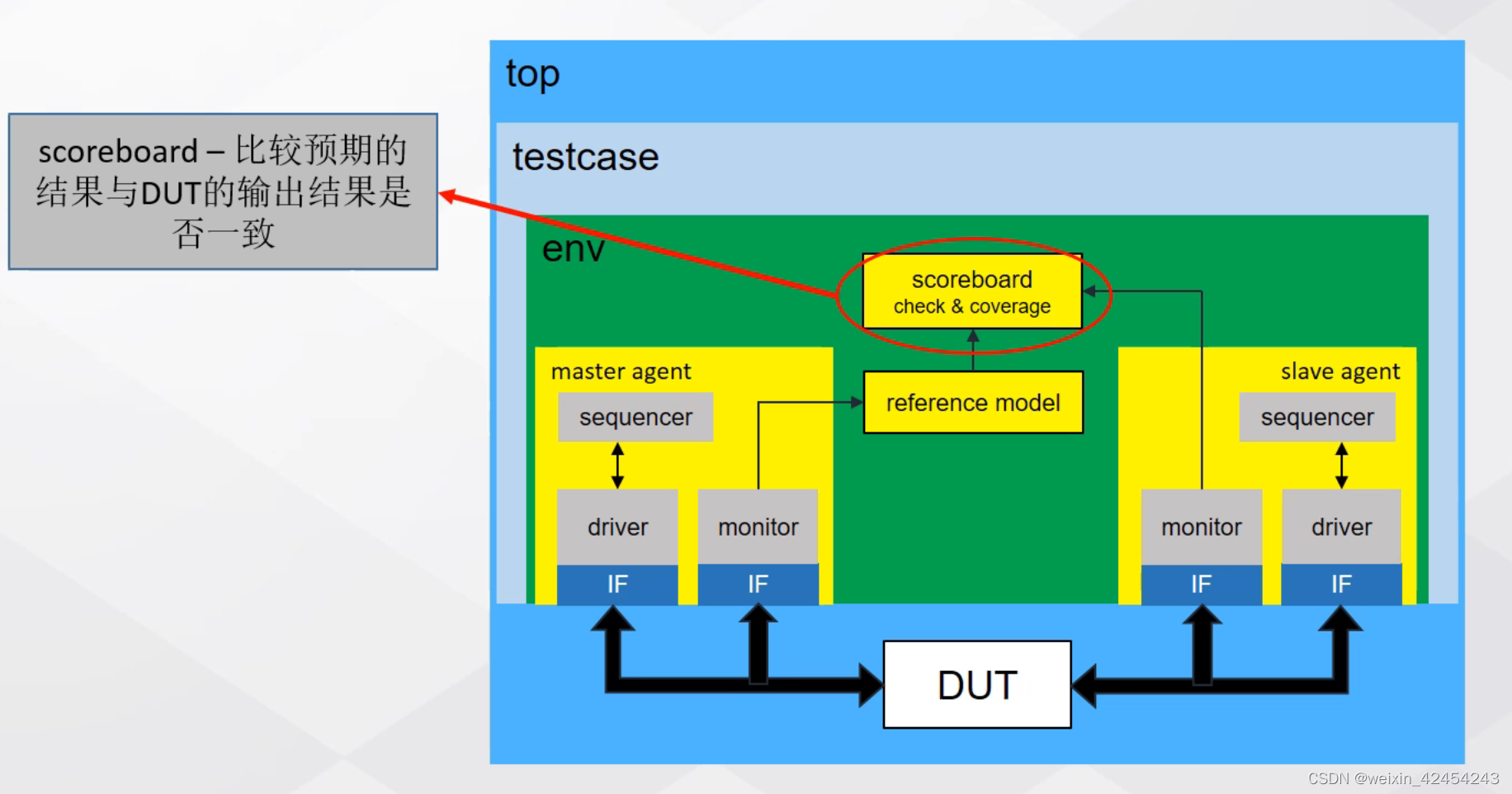

7. scoreboard

scoreboard:从两个地方获取数据,一个是参考模型发过来的期望值,另外一个是slave agent发来的DUT输出值,在积分板中,对这两个值进行比较,由此来判断DUT的功能是否正确。

同时可以将功能覆盖率嵌入scoreboard中,以实现覆盖率的收集。

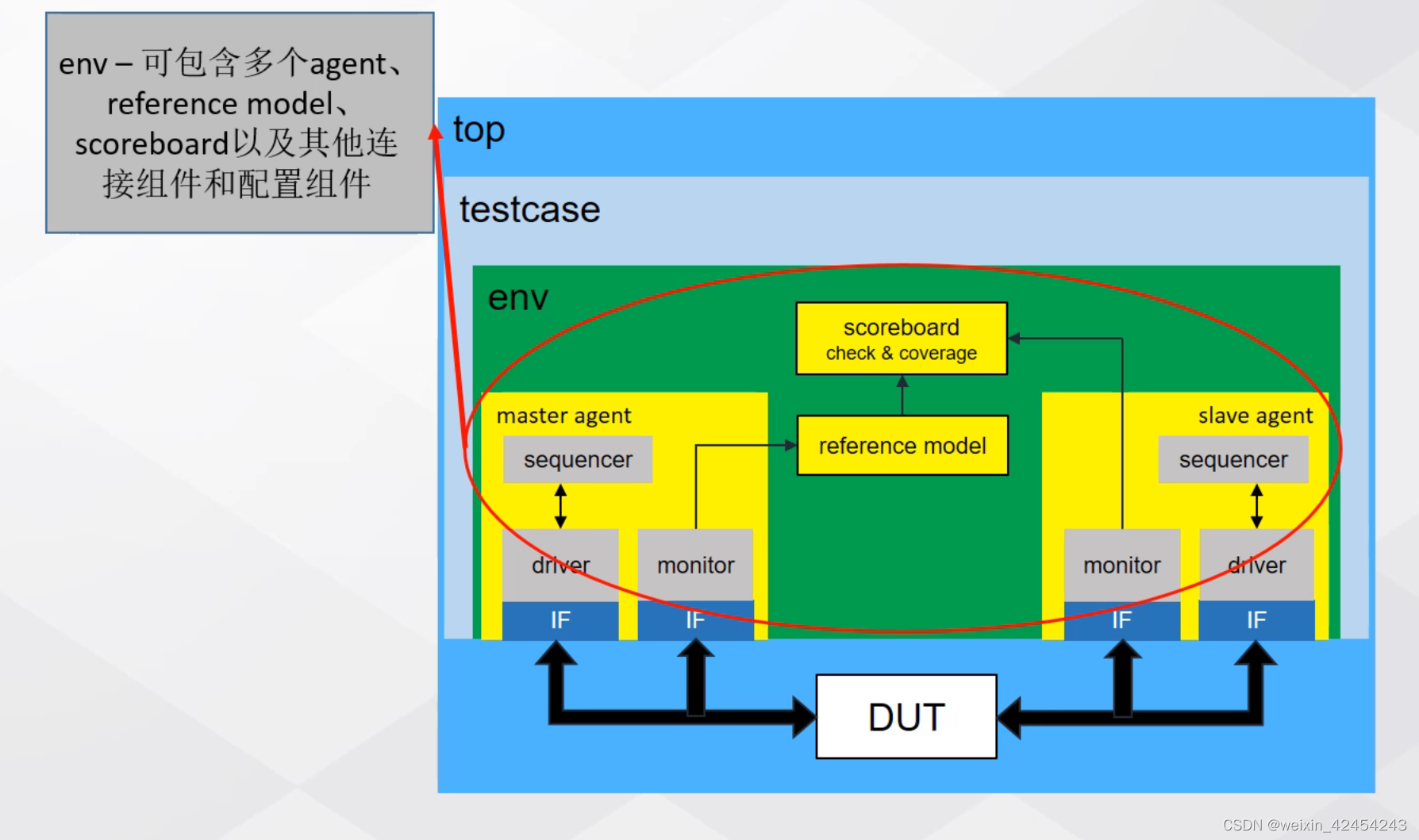

8. env

各个组件存在数据通信,将各个组件用某种方式连接起来。

一旦env完成,在后续的测试案例中,不能对其进行更改。如果需要更改env,那么之前通过的测试案例需要重新执行。

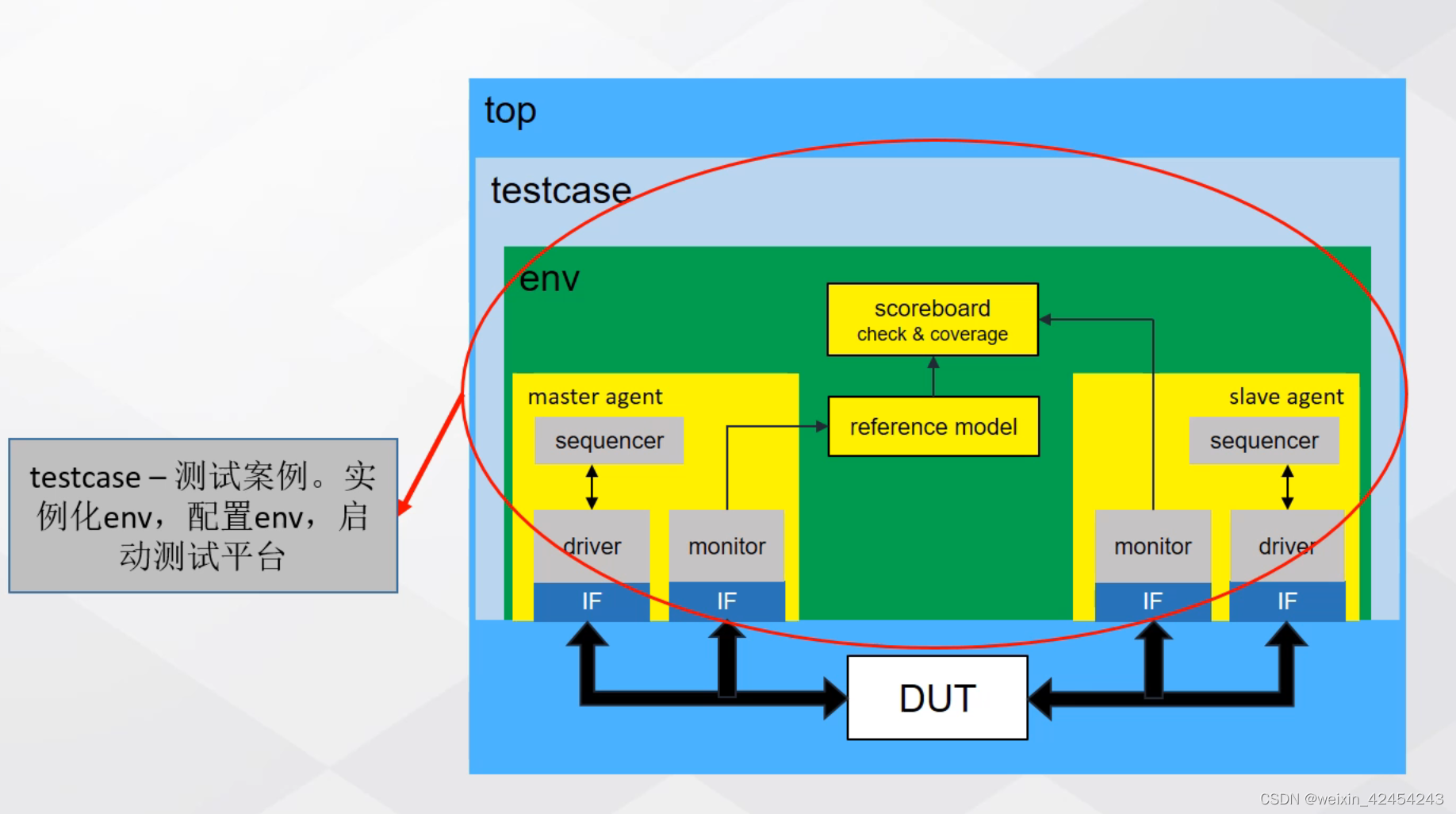

9. testcase测试案例

在一个测试项目中,测试案例可以有多个,但env只有一个,并且env一旦确定,就不能随意更改。

对整个平台的配置,都是在testcase中完成滴,因此,在构建env的时候,需要事先配置好接口,env具有可配置性。

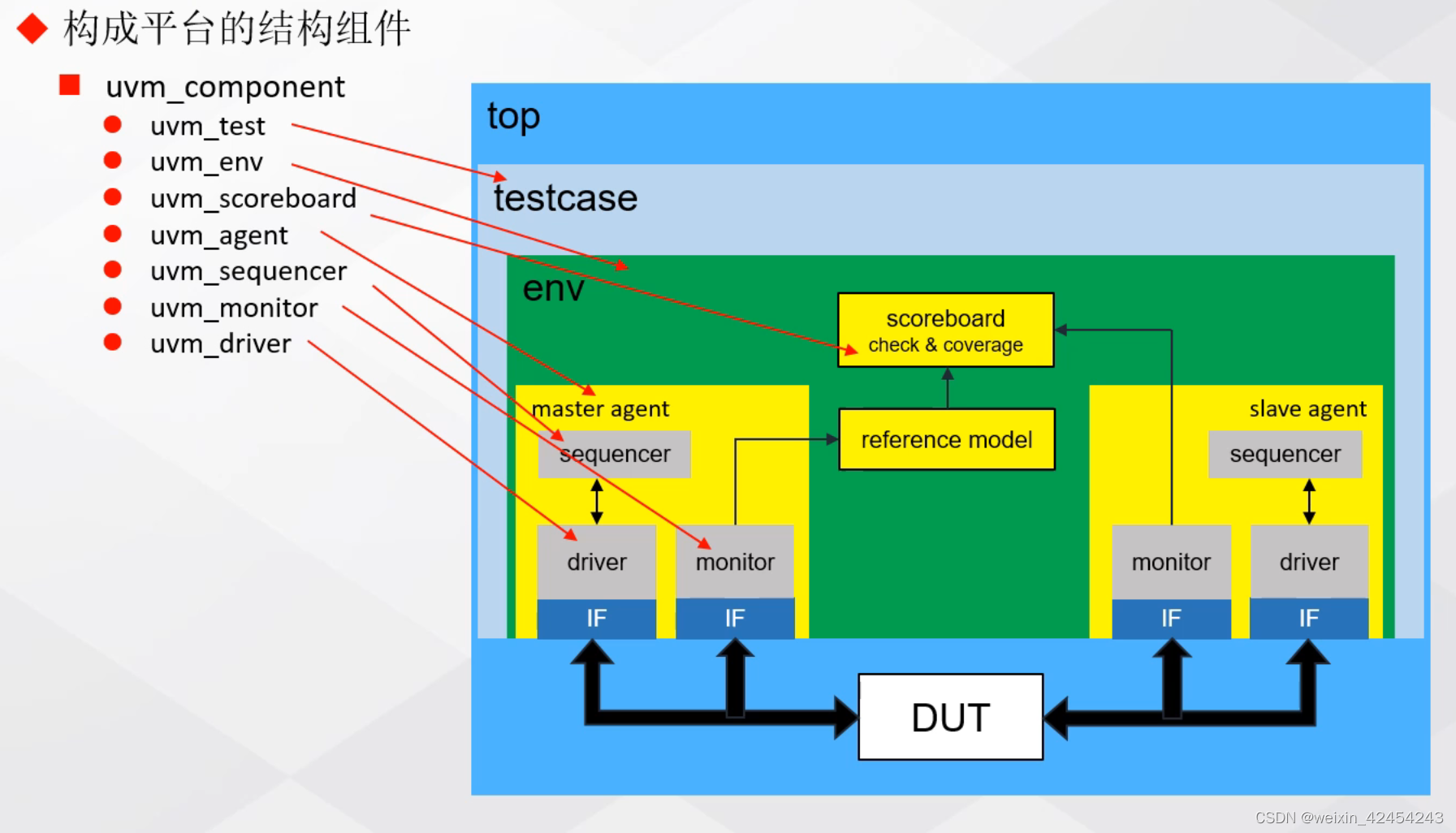

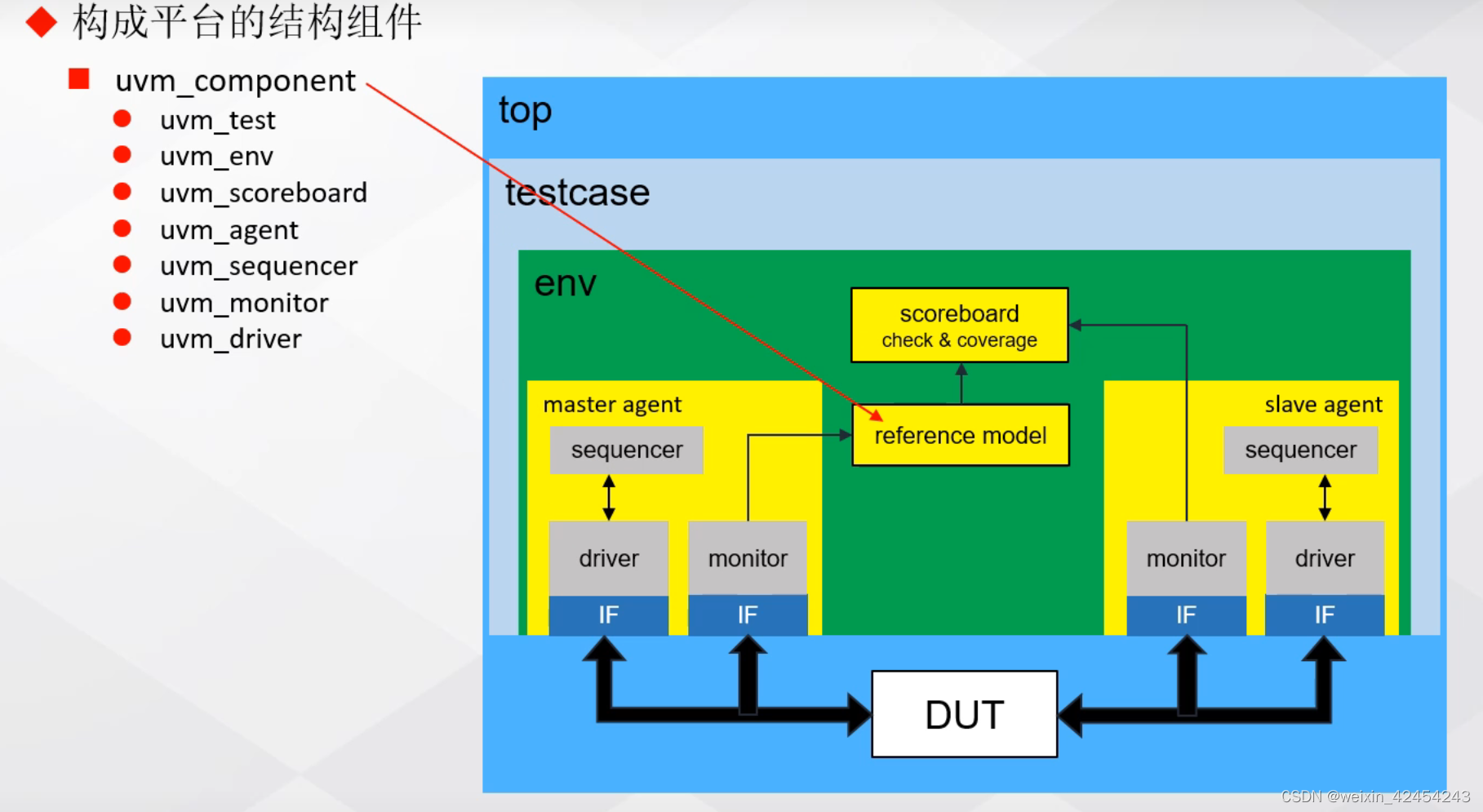

10. 构成平台的结构组件

从基类扩展

参考模型需要从uvm_component扩展

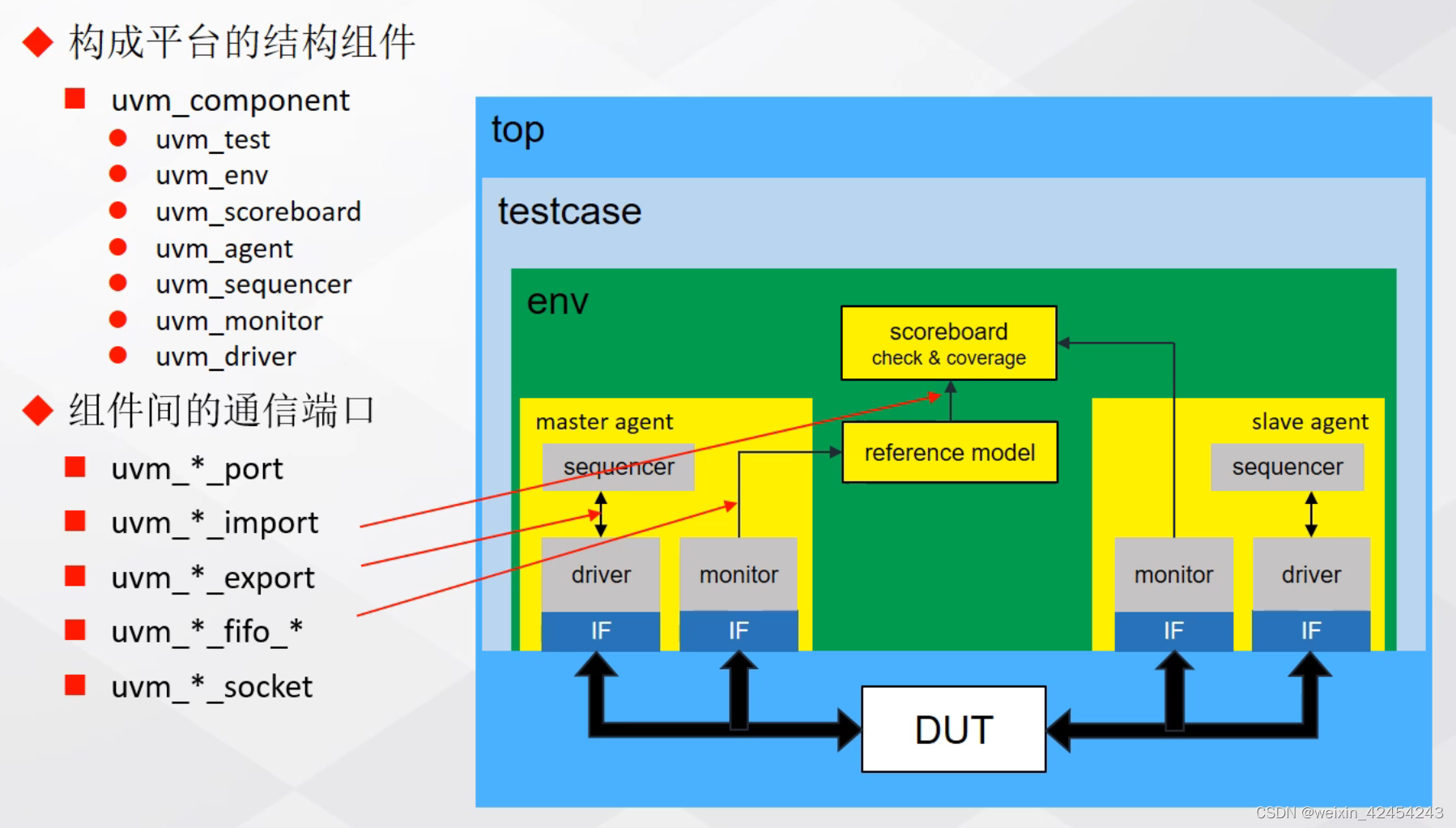

11. 组件间的通信端口

UVM需要建立某种机制,将需要通信的接口连接起来,使用通信端口来建立组件之间的连接。

uvm的端口有很多中,根据不同的场合,不同的需求来选用。

- uvm_*_port

- uvm_*_import

- uvm_*_export

- uvm_fifo

- uvm_*_socket

12. 类比举例

类比举例:组件比作工厂的流水线的设备,事务就是穿梭于设备中的产品;事务是组件的操作对象

13. 简化UVM平台

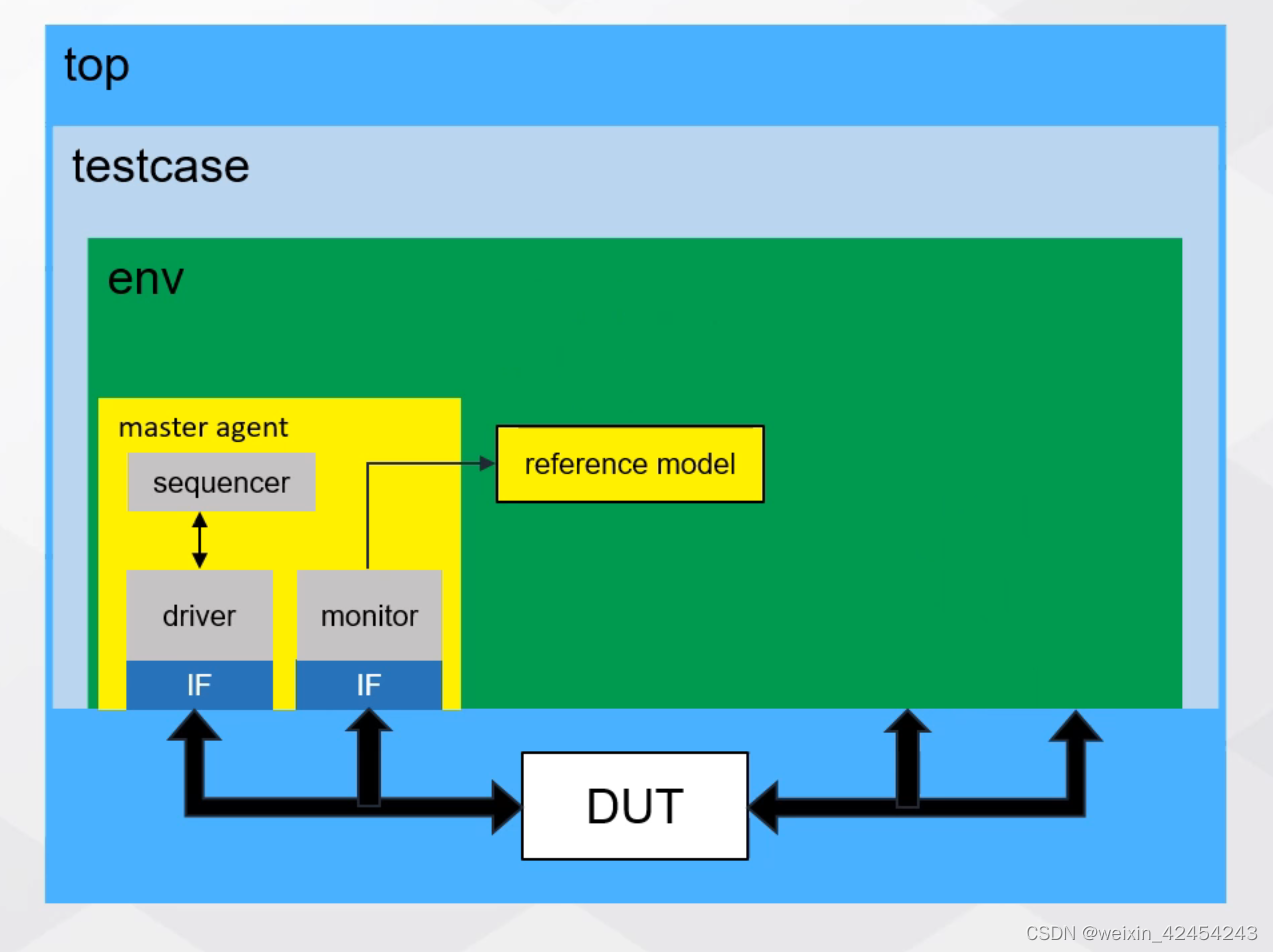

13.1 简化1—去掉slave agent

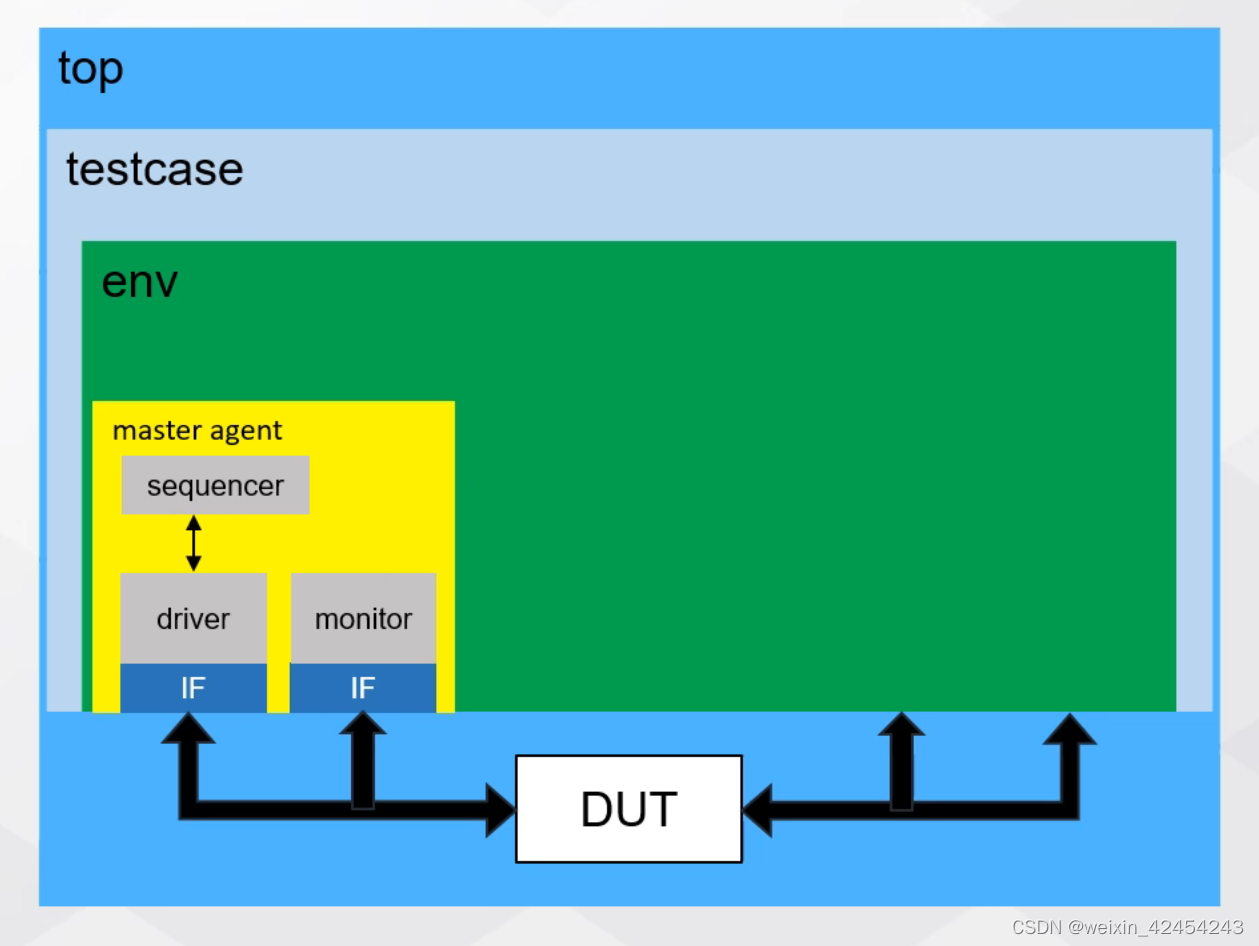

13.2 简化2—去掉scoreboard

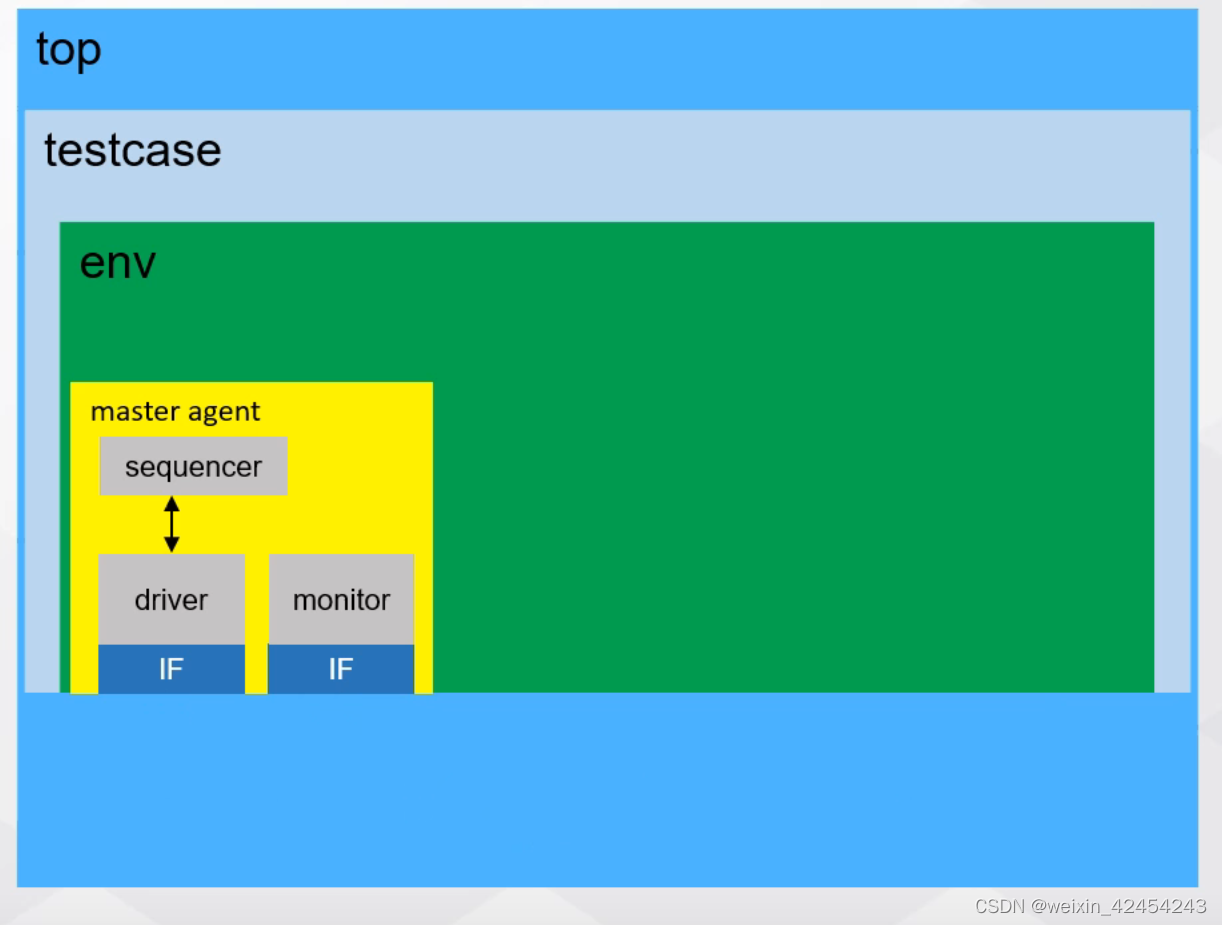

13.3 简化3—去掉reference modle(参考模型)

13.4 简化4—去掉DUT

最后,只剩下了一个master agent,实现的功能:仅产生事务,并把事务发送到driver上。

本文介绍了UVM验证平台中的关键组件,如driver、sequencer、monitor等,并详细阐述了它们的功能与工作流程。此外,还探讨了如何通过简化UVM平台来减少复杂度。

本文介绍了UVM验证平台中的关键组件,如driver、sequencer、monitor等,并详细阐述了它们的功能与工作流程。此外,还探讨了如何通过简化UVM平台来减少复杂度。

185

185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?