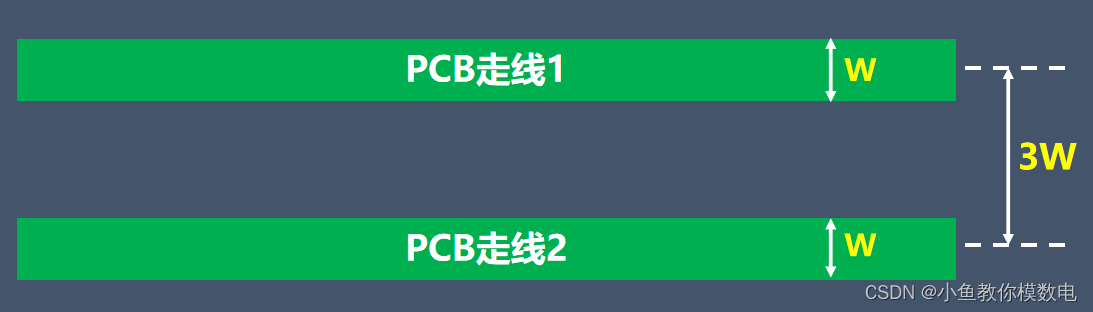

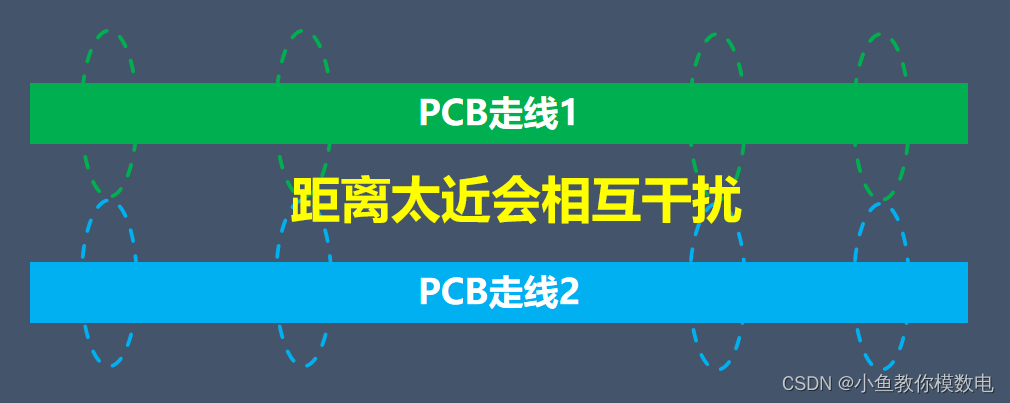

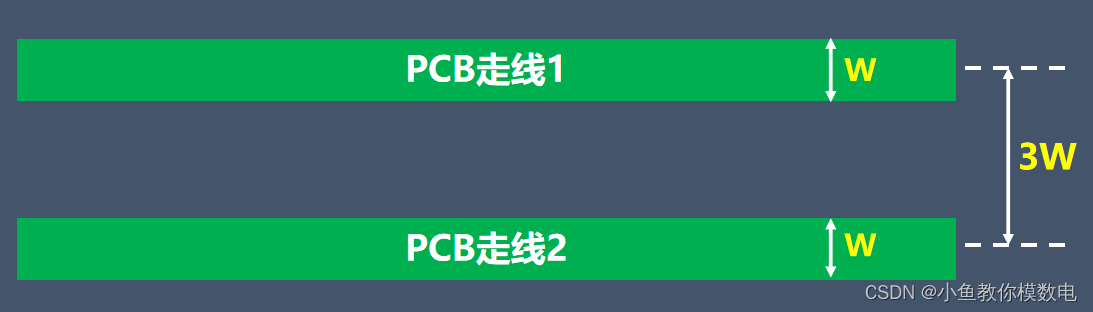

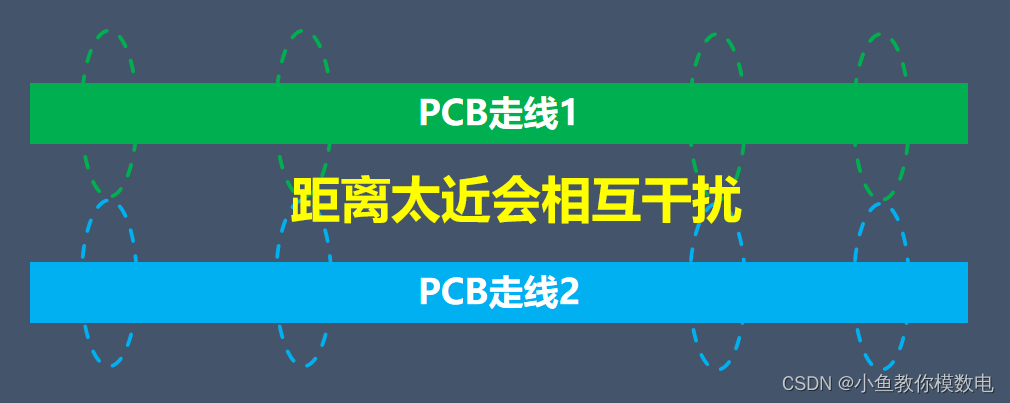

在设计PCB的时候我们会经常说到3W原则, 它指的是两个PCB走线它们的中心间距不小于3倍线宽,这个W就是PCB走线的宽度。

这样做的目的主要是为了减小走线1和走线2之间的串扰,一般对于时钟信号,复位信号等一些关键信号需要遵循3W原则。

当满足3W原则时,走线间的串扰可减少70%,如果是10W的话串扰可以减少95%。

<在设计PCB的时候我们会经常说到3W原则, 它指的是两个PCB走线它们的中心间距不小于3倍线宽,这个W就是PCB走线的宽度。

这样做的目的主要是为了减小走线1和走线2之间的串扰,一般对于时钟信号,复位信号等一些关键信号需要遵循3W原则。

当满足3W原则时,走线间的串扰可减少70%,如果是10W的话串扰可以减少95%。

< 1428

1428

3559

3559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?