简介:

TriCore是德国英飞凌科技公司旗下的第一个为实时嵌入式系统而优化的统一的、32位的微控制器-DSP(Digital Signal Processing)处理器架构。TriCore的ISA(Instruction Set Architecture),即指令集体系结构,将微控制器的实时能力、DSP的计算能力以及RISC(Reduced Instruction Set Computing)负载 / 存储体系结构的高性能 / 价格特性,结合在了一个紧凑的可重编程核心中

为了支持RTOS(Real-Time Operation System)代码中断的软件发布,TriCore架构定义了特殊的四个没有连接到外设或芯片上的任何其他模块上的CPU服务请求节点,这些SRN的中断请求位只能由软件来设置。

TriCore 提供了一种硬件的上下文机制,这种机制是专为嵌入式实时操作系统设计的,他的目的就是为了能提高线程切换的效率。

套用Tricore架构手册的话:在Tricore架构中,RTOS层可以做的非常薄,硬件可以有效处理一个任务与另一个任务的大部分切换。

该架构在任务模型的使用中有相当大的灵活性,在相对少的架构约束下,系统设计人员可以选择最优秀的实时执行和软件设计方法以使用应用的需求

一些后面要用到的操作介绍

Tricore 1.6指令(RISC):

MFCR : Move From Condition Register

MTCR : Move To Condition Register

这两个指令用来存取核心寄存器, 也就是所谓CFSR:Configurable Fault Status Register

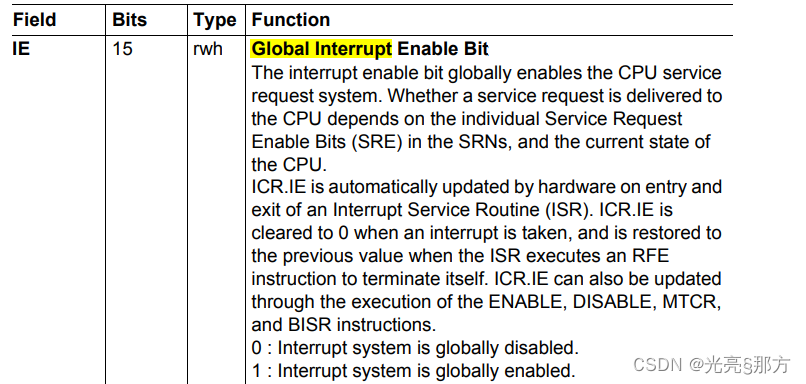

__disable(); 工具链直接提供的函数:关闭芯片全局中断 ICR.IE = 0;

IE 位是一个全局的中断使能位。进入中断时,IE 位由硬件自动置 0,当中断服务函数执行 rfe 指令(退出中断)后,IE 位自动恢复进中断前的值。另外, IE 位的值还可以被 enable; disable; mtcr; bisr; 等指令更新。

__enable(); 打开芯片全局中断 ICR.IE = 1;

上下文简介

一个任务是一个独立的控制

线程,任务的状态由它的上下文决定,当任务被打断时,处理器使用该任务的上下文恢复被打断前的执行现场,并继续执行任务。

Tricore上下文类型:

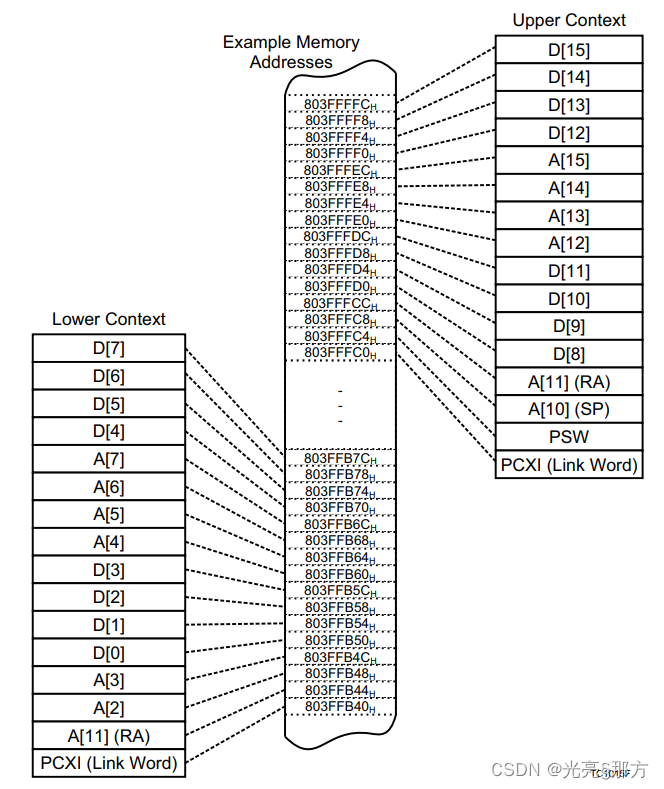

Upper context: 由上部地址寄存器A[10] 到 A[15] 和上部数据寄存器D[8] 到 D[15]组成 .上层上下文还包括PCXI和PSW.这些寄存器被设计为非易失以供函数调用 (它们的内容在调用过程中保留).

Lower context: 包含上部地址寄存器A[2] 到 A[7] 和上部数据寄存器D[0] 到 D[7],A[11] (Return Address) and PCXI

上下文保存到内存时,会占用16word的空间,这被称为上下文保存区域(CSA)

1838

1838

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?