1、PHY芯片介绍

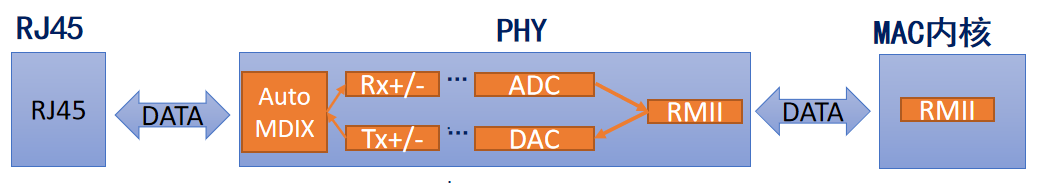

(1)在 TCP/TP 体系架构中,PHY芯片是物理层的实现,它负责将数据转换成光电模拟信号以便在网络中进行传输。

(2)一般的PHY芯片为模数混合电路,负责接收电、光这类模拟信号,经过解调和A/D转换后通过MII/RMII接口将信号交给MAC内核处理。

2、YT8512C芯片

(1)YT8512C是一款低功耗的单端口10/100Mbps以太网PHY芯片,它通过RJ45接口实现发送和接收数据所需的所有物理层功能。此外,YT8512C通过标准MII和RMII接口与MAC层进行连接。

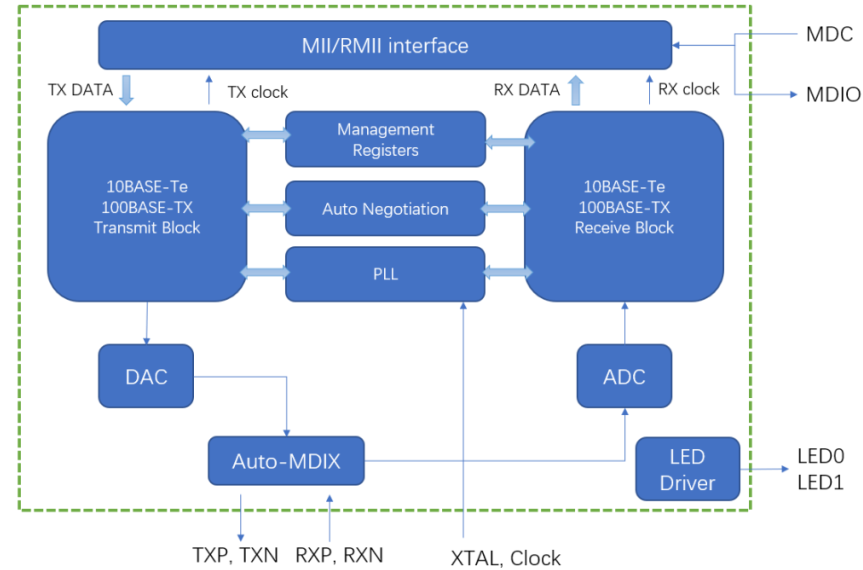

(2)功能结构图如下所示:

上图展示了 YT8512C 芯片的内部总架构示意图。从图中我们可以看出,通过 LED0 和LED1 引脚的电平来设置 PHY 地址, PHY 内部时钟由 XTAL 和 Clock 引脚提供。同时, TXP、TXN、 RXP 和 RXN 引脚连接到 RJ45(网口),用于数据的发送和接收。

2.1、PHY地址设置

MAC层通过SMI总线对PHY芯片进行读写操作。SMI总线具有强大的控制能力,可以管理多达32个PHY芯片。通过PHY地址的不同,我们可以精确地配置和访问每一个PHY芯片。对于YT8512C芯片,其PHY地址地设置方式如下表所示:

- 下表查阅YT8512C芯片手册所得

| LED0/ PHYAD[0] (PD) (Pin24) | LED1/ PHYAD[1] (PD) (Pin25) | PHY地址 |

|---|---|---|

| 0 | 0 | 0000 |

| 0 | 1 | 0010 |

| 1 | 0 | 0001 |

| 1 | 1 | 0011 |

2.2、YT8512C 的 RMII接口模式

(1)YT8512C的RMII接口提供了两种RMII模式:RMII1模式和RMII2模式。

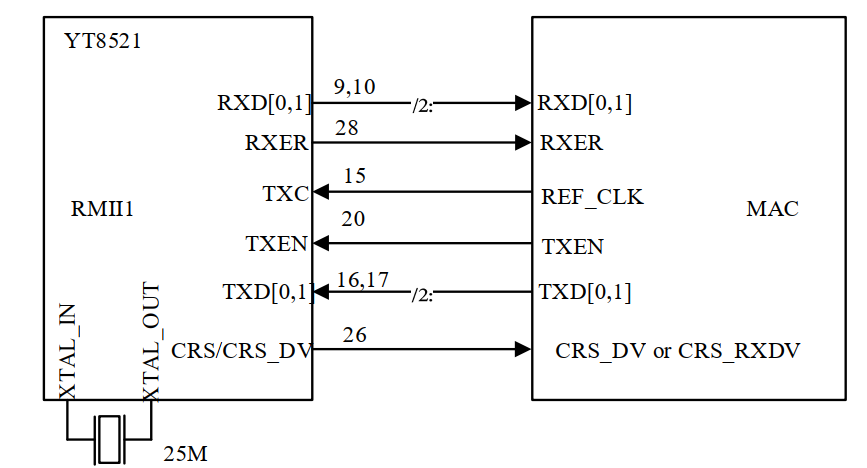

(2)RMII1 模式:YT8521C 的 TXC 引脚不会输出 50MHz 时钟,连接示意图如下图所示。

对于RMII接口而言,为了使PHY芯片与MAC内核保持时钟同步操作,需要外部提供50MHz的时钟驱动。这个时钟可以来自PHY芯片、有源晶振或者STM32的MCO引脚。如果我们的电路采用RMII1模式,PHY芯片将由25MHz晶振经过内部PLL倍频达到50MHz。但是,在这种情况下,MAC 内核并没有被直接提供 50MHz 时钟以与 PHY 芯片保持同步。因此,为了保持时钟同步,我们需要在该基础上使用 MCO 或接入外部 50MHz 晶振来为 MAC 内核提供时钟。简而言之,为了确保 PHY 芯片与 MAC 内核之间的时钟同步,我们需要根据所采用的 RMII 模式,采取相应的措施来提供准确的时钟信号。

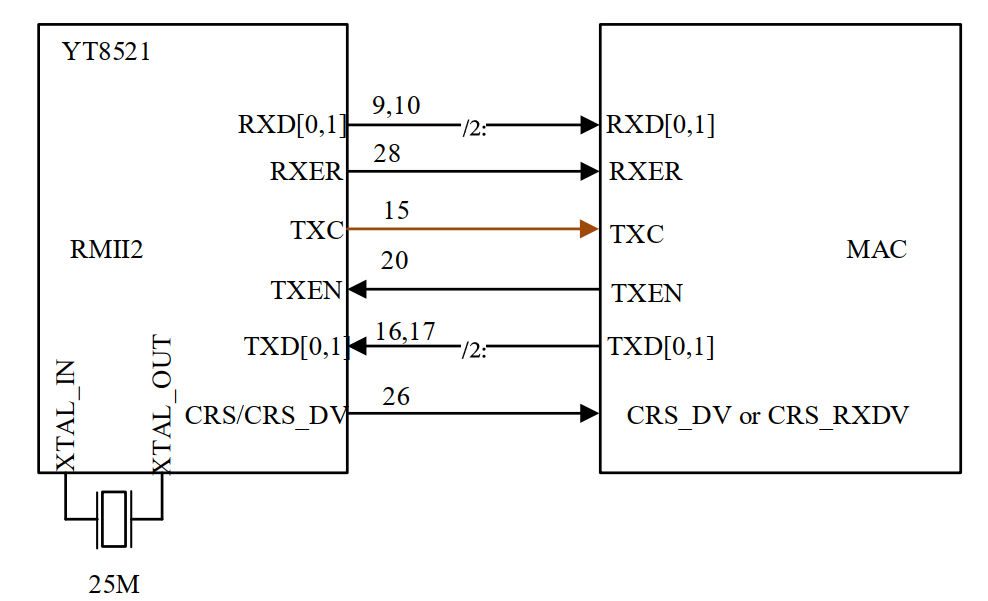

(3)RMII2模式:YT8512C 的 TXC 引脚会输出50MHz时钟,连接示意图如下所示。

如果电路按照上图模式进行连接,PHY芯片将通过外接晶振的25MHz信号和内部PLL倍频操作,生成50MHz的内部时钟。接着,PHY芯片的外围引脚TXC将输出50MHz时钟频率,这个时钟频率可以直接输入到MAC内核,以确保时钟同步。这样,我们就不需要再使用外部晶振或MCO引脚来提供MAC内核的时钟。

(4)至于RMII1模式和RMII2模式的选择,这取决于YT8512C的RX_DV(8)和RXD3(12)引脚的状态。具体如何选择查看参考手册。

2.3、YT8512C寄存器介绍

略

3、LAN8720A芯片

(1)LAN8720A 是一款低功耗的单端口 10/100Mbos 以太网PHY芯片,它通过RJ45接口实现发送和接收数据所需的所有物理层功能。此外,LAN8720A通过标准MII和RMII接口与MAC层进行连接。

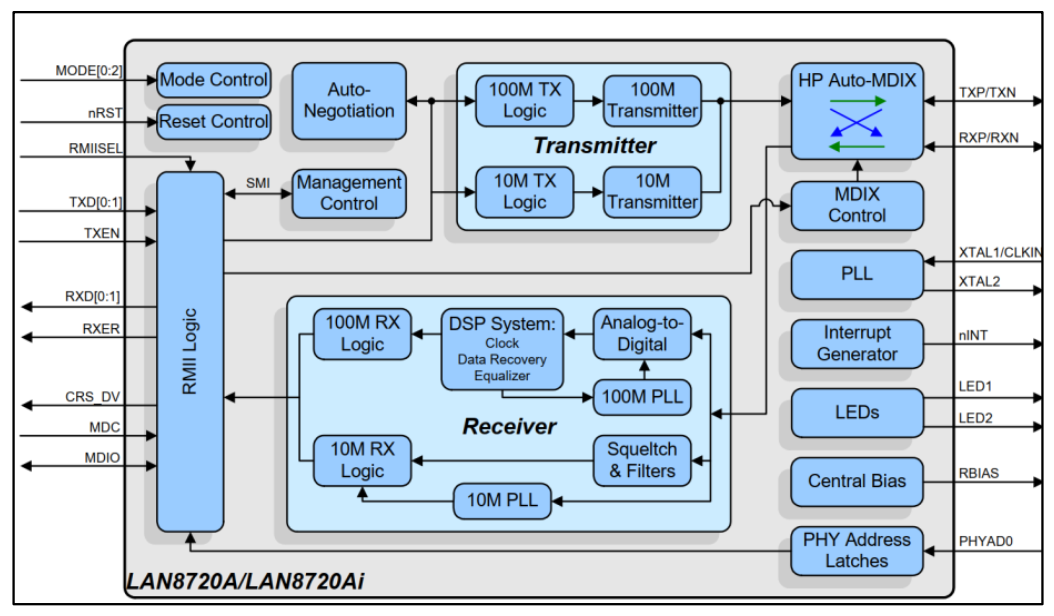

(2)功能结构如下如图所示:

3.1、LAN8720A中断管理

LAN8720A 的器件管理接口支持非IEEE802.3规范的中断功能。当中断事件发生且相应中断位使能时,LAN8720A会在nINT(14脚)产生一个低电平有效的中断信号。LAN8720A的中断系统提供了两种中断模式:主中断模式和复用中断模式。默认的中断模式为主中断模式,LAN8720A 在上电或复位后即工作在此模式下。

3.2、PHY地址设置

MAC层通过SMI总线对PHY芯片进行读写操作。SMI总线具有强大的控制能力,可以管理多达32个PHY芯片。通过PHY地址的不同,我们可以精确地配置和访问每一个PHY芯片。对于LHA8720A芯片,其PHY地址地设置方式如下表所示。

| RXER/PHYAD0引脚状态 | PHY地址 |

|---|---|

| 上拉 | 0x01 |

| 下拉(默认) | 0x00 |

通过设置 PHYAD0 引脚的电平,我们可以为 LAN8720A 芯片分配一个唯一的 PHY 地址。在 MAC 层和 PHY 芯片之间进行通信时, SMI 总线会根据这个地址来识别和操作特定的 PHY芯片。

3.3、nINT/REFCLKO配置

nINTSEL引脚(2号引脚)用于设置nINT/REFCLKO引脚(14号引脚)的功能。

nINTSEL配置如下表所示。

| nINTSEL引脚值 | 模式 | nINT/REFCLKO引脚功能 |

|---|---|---|

| nINTSEL=0 | REF_CLK Out模式 | nINT/REFCLKO作为REF_CLK时钟源 |

| nINTSEL=1 | REF_CLK In模式 | nINT/REFCLKO作为中断引脚 |

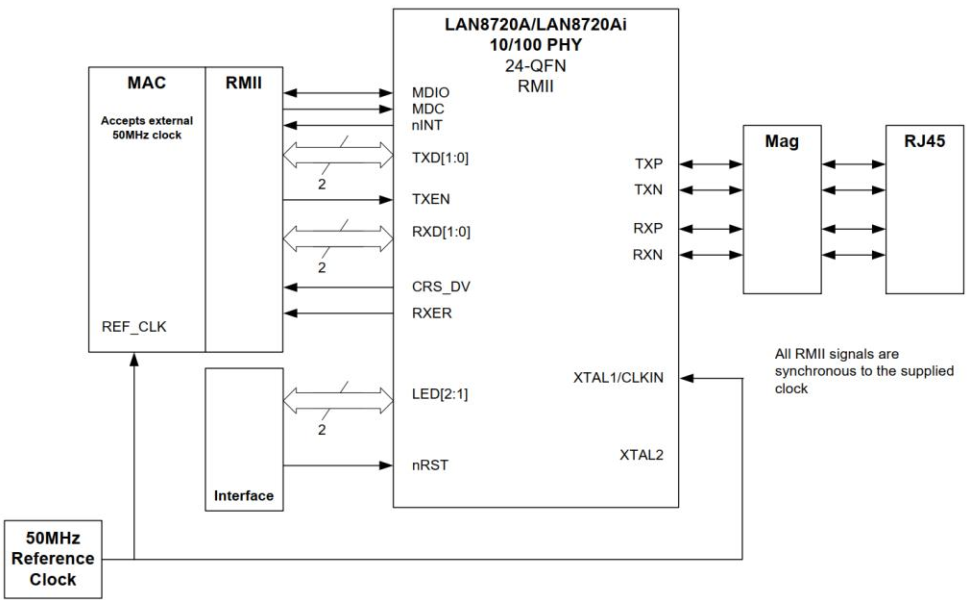

(1)当工作在REF_CLK In模式时,50MHz的外部时钟信号应接到LAN8720的XTAL1/CKIN引脚(5号引脚)和MAC内核的RMII_REF_CLK引脚上,如下图所示。

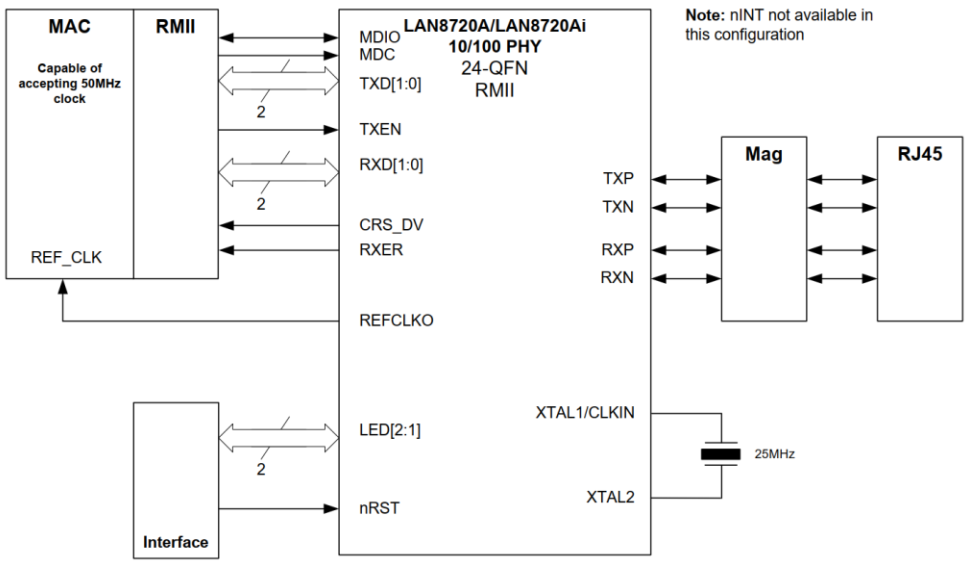

(2)为了降低成本,LAN8720A 可以从外部的25MHz的晶振中产生REF_CLK时钟。要使用此功能时应工作在REF_CLK Out模式。当工作在REF_CLK Out模式时REF_CLK的时钟源如下图所示。

3.4、LAN8720A寄存器介绍

略

82

82

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?