1 简介

具有快速边沿的时钟信号将印刷电路板 (PCB) 上的迹线视为传输线而不是简单的电线连接。 如果 PCB 走线的长度超过一定的限制,则需要走线阻抗与源阻抗和负载阻抗之一或两者的匹配。 阻抗不匹配导致信号反射在传输线上来回传播导致信号、失真,如振铃、过冲和下冲。 本应用笔记提供正确端接主要由 LVCMOS 输出驱动的单端走线的指南。本文档讨论单负载和多负载场景。

2 集总与分布式 PCB 走线

时钟源、PCB 走线和时钟接收器被认为是一个集总系统,如果响应一个输入信号,所有点都以统一的电位一起反应。 如果响应被分发沿着这个轨迹的系统被称为分布式系统。信号传播速度在任何环境是有限的,所以不可能有完美的集总系统。 这是一种常见的做法将PCB走线的长度与最快时钟信号边沿的有效长度进行比较并使用这个比率来判断是否出于实际目的该系统可以被视为一个集总系统。 这迹线中的有效信号边缘长度计算如下:

L=上升边长度,in

Tr = 10% - 90%上升时间,ps

Tpd = 每单位长度的传播延迟,ps/in。

例如,在FR4 PCB跟踪的传播延迟范围从140到180 ps/in。 假设 Tpd = 150 ps/in。 1 ns上升沿的有效长度为6.7英寸。

如果 PCB 走线的长度小于或等于信号边沿有效长度的六分之一 (L/6)。 与 20% - 80% 相比上升/下降时间,更合适的比率是L/4来决定一个迹线是否可以被认为是一个集总元素。 集总电路不需要端接。 例如,假设一个时钟1 ns 10%-90% 上升时间的信号和长于 1.1 英寸的 FR4 PCB 材料走线必须作为传输线处理。

不同负载选项和驱动强度下 SiTime 振荡器的上升和下降时间大多数零件系列的数据表中都有设置。 选择最低负载选项当使用公式 1 时,数据表上升/下降时间表(通常为 5 pF),因为电容负载在驱动传输时,接收端不会影响源端的上升/下降时间线。

当时钟驱动器向传输线发送边沿时,边沿到达负载后一些延迟。 如果负载的阻抗与传输线的阻抗不同,则一部分信号从负载反射到源。源处不匹配导致部分反射信号反射回负载(圆头反射)。 反射信号的分数由反射系数决定[附录 B]。 以下部分描述了可用于最小化的终止策略驱动单个或多个负载时反射并提高信号完整性。

3 时钟终止建议

3.1 驱动单个负载的源端接

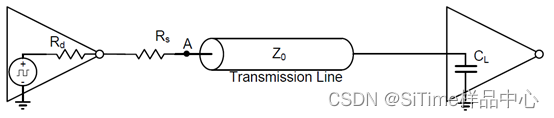

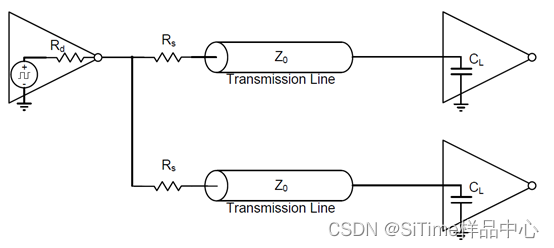

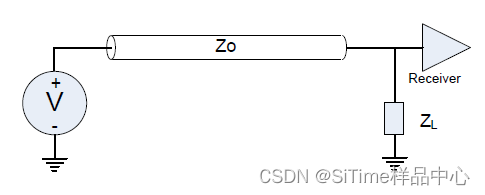

图1:串联端接

串联终端是通过插入一个与走线串联的电阻器来构建的源(见图 1)。 为了适当的阻抗匹配的输出阻抗时钟驱动器加串联终端电阻应等于走线阻抗,即:

![]()

- Rs - 终端电阻的值

- Rd——驱动器的输出阻抗

- Z0——传输线阻抗

例如,我们计算适用于 SiT8208 器件的终端电阻值具有默认驱动强度并在 3.3V 下工作,驱动 60Ω 走线。 从产品数据表 [2] 表 4 我们确定默认驱动强度代码为“F”。 使用表 1 从附录 C 我们确定了带有驱动器的 SiT8208 器件的典型输出阻抗强度代码“F”和 3.3V 工作电压为 15.3 Ω。 替代走线阻抗和将输出阻抗转换为公式 2,我们计算源终端电阻值 Rs = 60 Ω -15.3 Ω = 44.7 Ω。

使用图1中的配置,来自源的信号将沿着迹线传播,直到它达到负载。 典型负载具有非常高的输入阻抗(在兆欧范围内),所以不会吸收能量,整个信号被反射回源。 因为源端的阻抗与传输线的阻抗匹配,不会有进一步的反射发生。 串联端接信号传播详细图见附录A传输线。

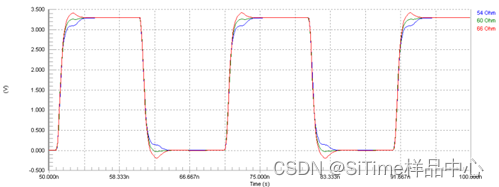

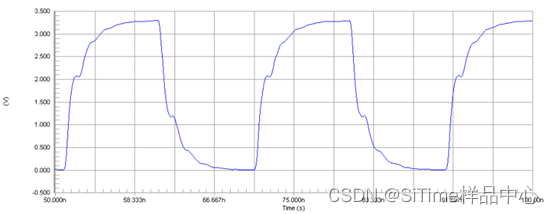

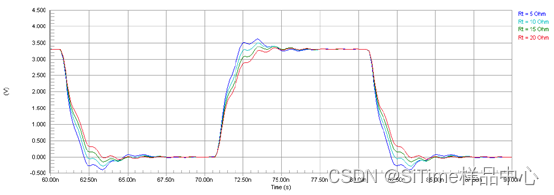

SiTime 建议使用 SiTime 提供的振荡器 IBIS 模型来模拟布局。 作为我们使用Altium Designer 软件中的信号完整性分析工具进行仿真的示例SiT8208振荡器驱动5英寸 60-Ω 传输线。 图2显示信号波形负载侧模拟。 选择终端电阻 Rs = 43 Ω 以匹配 60 Ω 线路阻抗。 使用相同值的终端电阻来模拟 ±10% 的走线阻抗变化,从而将 PCB 制造扩展考虑在内。

图 2:SiT8208 驱动负载通过传输线 5 的 Altium Designer 仿真波形。 走线阻抗 – 54、60 和 66 Ω,电源电压 – 3.3 V,源端接 – 43 Ω,负载电容 – 5 pF

有关 SiTime 单端振荡器的典型输出阻抗的信息,请参阅附录 C。

3.2 驱动多个负载

PCB上的两个或多个IC可能需要相同频率的输入时钟。 使用时钟驱动多个负载的一种方法是使用扇出缓冲器,这需要额外的电路板空间和功率。 另一种方法是将一个输出连接到多个负载。

将一个输出连接到多个负载的首选方法是在尽可能靠近负载的地方布线一条传输线,并使用星形连接通过短走线连接负载,因此负载被认为是在走线末端集总(3.2. 1)。 这种方法要求负载彼此足够接近。

如果负载彼此相距太远而无法使用集总负载配置,则在某些条件下,可以使用一个输出来驱动两条传输线以分离负载(3.2.2)。这种配置要求输出驱动器具有比驱动单个传输线更高的电流驱动能力,并且不建议与1.8V版本的 SiT1602 和表2中列出的其他设备一起使用,当使用60-Ω 和较低阻抗传输线时。 建议在将此配置纳入设计之前使用IBIS模型运行信号完整性仿真。

一些驱动器可能没有足够的驱动能力来处理两条传输线。 如果振荡器输出和负载之间的距离足够小,则可以考虑星形拓扑(3.2.3)。

典型振荡器的输出驱动器不足以驱动三个或更多传输具有可在 PCB 上轻松设计的走线阻抗的线路 (50 – 60 Ω)。 时间不建议从单个驱动器驱动三个或更多传输线。

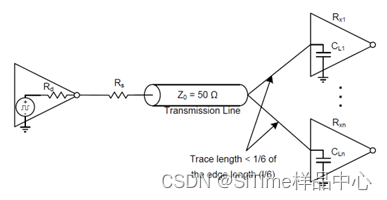

3.2.1 驱动多个负载在走线末端集中

驱动多个负载的最简单方案是在负载结束时点亮传输线(图 3)。 如果负载可以放置得足够靠近传输线的末端,以便将每个负载连接到传输线的走线是不超过信号边沿有效长度的六分之一。 负载必须是以“星形”形式连接,如图 3 所示。串联终端电阻的值为计算方式与单个载荷工况(公式 2)相同。

图 3:多个负载集中在走线末端的串联端接

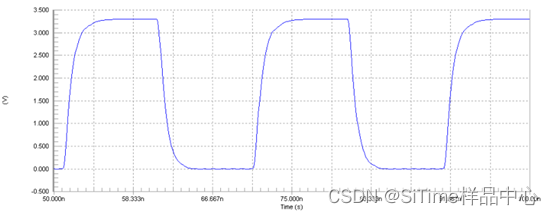

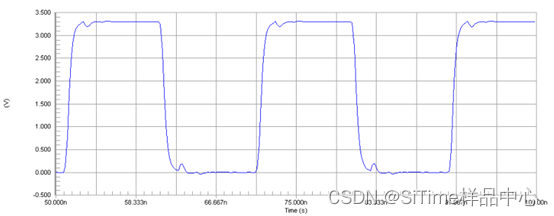

图 4 说明了图 3 中方案的 Altium Designer 仿真结果,用于 SiT8208-3.3V 振荡器,前提是 Rs = 43 Ω,CL = 5 pF,时钟接收器数量 – 2,存根长度0.5 英寸(~75 ps)。 如果存根太长,反射会导致信号完整性问题(见图 5)。

图 4:Altium Designer 仿真波形(在负载侧)SiT8208 驱动两个在 5 英寸末端集总的负载。 痕迹。 走线阻抗 – 60 Ω,电源电压 – 3.3 V,源端接 – 43 Ω,负载电容 – 5 pF。

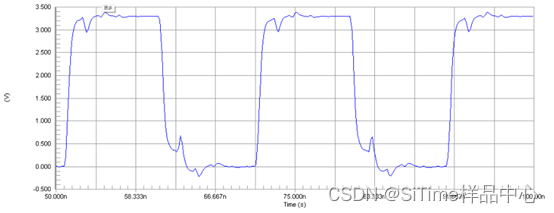

图 5:当驱动器的走线在2英寸后分裂成两个3英寸时,SiT8208 驱动两个负载的 Altium Designer 仿真波形(在负载侧)。 每个部分都连接到负载。 走线阻抗– 60Ω,电源电压– 3.3 V,源端接–43 Ω,负载电容–5 pF。

3.2.2 一源驱动两条传输线

如果时钟接收器彼此相距很远,则时钟接收器可能不会被安排在集总负载配置中。 在这种情况下,可以使用单独的传输线将信号传送到每个负载。 图6说明了一种配置,该配置可用于从单个驱动器驱动多个源端终止传输线。

图6:从一个源驱动多条传输线

这种方法成本低,因为每条迹线只需要一个终端电阻器,并提供完整的负载侧的摆动信号幅度。 需要满足以下条件才能达到最佳效果信号完整性 [1]:

- 时钟驱动器可以在边沿传输期间提供足够的峰值电流

- 所有传输线的长度相同

- 每个接收器侧的容性负载大致相同

- 终端电阻根据公式3计算

![]()

- Rs - 源端终端电阻

- Z0——传输线阻抗

- Rd——驱动器输出电阻

- N - 驱动线数

图7为SiT8208-3.3V图6方案Altium Designer仿真结果振荡器。 源端终端电阻根据公式 3 计算。上升沿后和下降沿后的小凸起多是寄生引起的负载和源极驱动器的电容会导致轻微的阻抗不匹配。

图 7:用于驱动两个 5 英寸的 SiT8208 的 Altium Designer 仿真波形(在负载侧)。 传输线。 走线阻抗 – 60 Ω,电源电压 – 3.3 V,Rs = 15 Ω,CL = 5 pF。

驱动两条 50Ω 传输线需要比驱动两条 60Ω 传输线更强的驱动器。 图 8 显示了图 6 中方案的 Altium Designer 仿真结果,使用相同的 SiT8208-3.3V 振荡器,但驱动两条 50Ω 线路。 源终端电阻设置为零,但源阻抗仍然太高,无法确保达到图 7 中实现的良好信号完整性。建议为 SiT8208 振荡器选择比默认驱动强度更强的驱动强度选项 已用于模拟。

图 8:用于驱动两个 5 英寸的 SiT8208 的 Altium Designer 仿真波形(在负载侧)。 传输线。 走线阻抗 – 50 Ω,电源电压 – 3.3 V,Rs = 0 Ω,CL = 5 pF

使用单个源驱动两条传输线的方法可确保从负载反射的信号在源处以相互抵消的方式相互交互,并且没有信号反射回负载。 从两个负载反射的信号传回源。 在源头,它们再次反射并通过驱动器耦合到另一条传输线。 如果来自一条线路的反射被另一条线路的耦合抵消,则不会将信号能量发送回负载。 为了完美消除反射信号必须同时到达源并且必须具有相同的形状。 传输线必须具有相同的长度并且需要具有平衡的负载。 图9显示了不平衡容性负载对两条线路的影响,图10显示了不匹配传输线长度的影响。

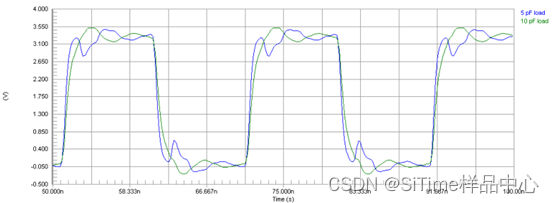

图 9:用于驱动两个 5 英寸的 SiT8208 的 Altium Designer 仿真波形(在两个负载下)。 当两个负载的电容不平衡时,传输线。 走线阻抗 – 60 Ω,电源电压 – 3.3 V,Rs = 15 Ω,CL1 = 5 pF,CL2 = 10 pF

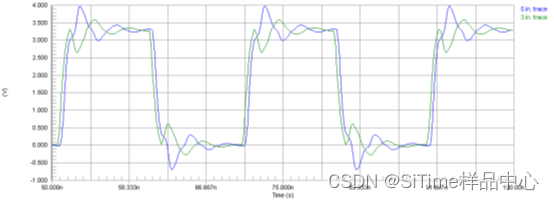

图 10:SiT8208 驱动两条不同长度的传输线的 Altium Designer 仿真波形(在两个负载下)。 走线阻抗 – 60 Ω,电源电压 – 3.3 V,Rs = 15 Ω,CL = 5 pF

3.2.3 驱动两个负载的星型拓扑

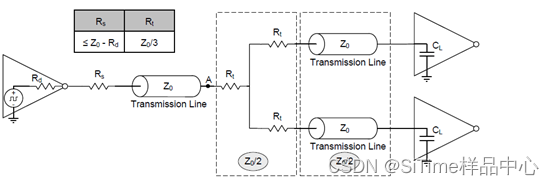

在某些情况下,当振荡器的驱动器不足以驱动两条传输线(输出阻抗太高)时,可以使用启动拓扑(图11)。Rt电阻网络用作中间终端。Rt的值通常选择为等于传输线阻抗 (Z0/3) 的三分之一,因此从任何节点看,三个Rt电阻的星形连接具有Z0/2的阻抗。 两根阻抗为Z0的传输线并联,阻抗为Z0/2,因此从A点看(图 11)朝向负载的阻抗为Z0,它等于从来源。A点的阻抗匹配,因此在那里不会发生反射。

图 11:驱动两个负载的星型拓扑

星形拓扑通常与负载端接一起使用。 在这种情况下,信号从源驱动程序通过跟踪分割点而不反射回来,到达负载,因为负载阻抗匹配不会反射回源。 负载看到一个良好的信号没有反射,但幅度非常低,这对于许多时钟接收器来说是不可接受的。

如果没有负载终端且负载为高阻抗,则所有信号能量都反射回来源。 中间点的阻抗使用 Rt 网络匹配,但两个反射信号同时传回,因此发生耦合。 这使得很难找到一个反射和耦合之间的平衡,并实现可接受的信号完整性。

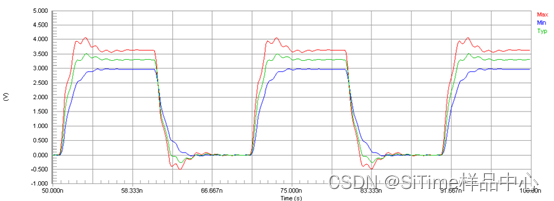

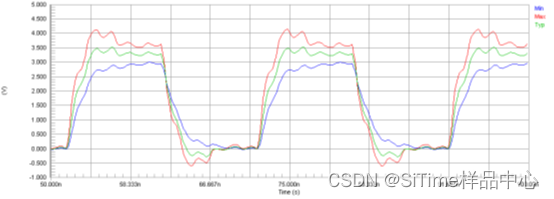

在无负载端接的情况下,不建议将此方法用于更长的传输线超过轨迹中边缘长度的三分之一(参见公式1)。 例如,对于 1 ns 的上升时间信号星段的长度不应超过2英寸。 应模拟设计对典型和极端情况使用 IBIS 模型,以确保不存在信号完整性问题。图12显示了具有2英寸的星形拓扑极端情况下的仿真结果痕迹。

图 12:SiT8208 使用星形拓扑驱动两条传输线的拐角(温度、电源电压和工艺)的 Altium Designer 仿真波形(在负载侧)(图 11)。 走线阻抗 – 60 Ω,走线段长度 – 2 英寸,标称电源电压 – 3.3 V,Rs = 10 Ω,Rt = 10 Ω,CL = 5 pF

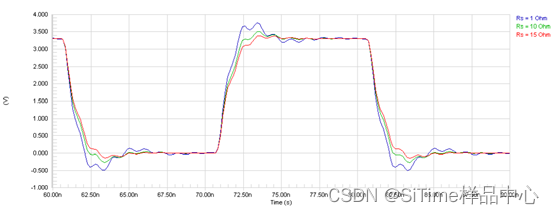

图13和图14显示的仿真结果分别说明了信号波形如何随 Rt 和 Rs 变化。

图 13:Altium Designer 仿真波形(在负载侧),适用于 SiT8208 使用星形拓扑驱动两条传输线的 Rt 值范围(图 11)。 走线阻抗 – 60 Ω,走线段长度 – 2 英寸,电源电压 – 3.3 V,Rs = 10 Ω,CL = 5 pF

图 14:Altium Designer 仿真波形(在负载侧)的 Rs 值范围SiT8208 使用星形拓扑驱动两条传输线(图 11)。 走线阻抗 – 60 Ω,走线段长度 – 2 英寸,电源电压 – 3.3 V,Rt = 10 Ω,CL = 5 pF

如果需要更长的走线并且增加信号上升/下降时间不是问题,那么可以在Rs和传输线之间的源极处使用额外的电容器 (Cs),从而创建一个时间常数为(Rs + Rd)C 。图 15 说明了如何在源极使用15pF电容器来驱动具有5英寸段的星形迹线拓扑。

请注意,说明星形拓扑的示例中上升沿和下降沿的形状不是适用于一些对抖动敏感的应用。

图 15:Altium Designer 仿真波形(在负载侧)SiT8208 使用星形拓扑驱动两条传输线的工艺角(图 11)。 源端的额外 15 pF 电容器用于减慢信号边沿 走线阻抗 – 60 Ω,走线段长度 – 5 英寸,电源电压 – 3.3 V,Rt = 10 Ω,CL = 5 pF

3.3 使用源端接时的低通滤波器效果

信号源与源终端一起驱动传输线,并将边沿送入传输线。在线路的末端,负载看不到产生边缘的驱动器,而是看到传送边缘的传输线。 传输线用作远端负载的驱动器,因此从负载的角度来看,驱动阻抗等于线路阻抗。

典型 IC 的时钟输入负载主要是电容性的。 驱动阻抗与负载阻抗形成一个低通滤波器,看起来像一个简单的 RC 滤波器。 这种滤波器的截止频率是 Z0CL。 假设 50 Ω 传输线形成一个转角频率为 637 MHz 的低通滤波器。

对于大多数应用,该滤波器的转角频率足够高,不会导致信号衰减。 但是用户必须密切监视负载电容,以确保转角频率舒适地保持在时钟的工作范围之上。

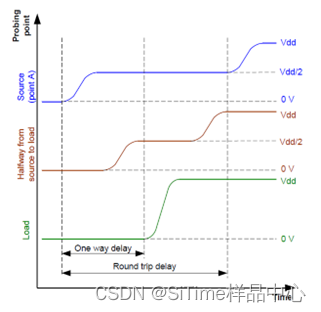

附录 A:串联端接传输线中的信号边缘传播

串联终止是终止时钟信号的一种经济方式。 它简单、便宜、耗电少、需要的电路板空间小。 串联终端适用于驱动走线末端的集总负载。 但是,它不能用于驱动沿轨迹分布的负载。

图 16:传输线不同点的信号形成

考虑图 1 中 A 点的信号。当信号向负载传播时,信号的上升沿正好达到全摆幅电压的二分之一。 由于负载侧的阻抗很高,所有信号能量都反射回源,因此 A 点的信号达到全摆幅电压,但仅在往返延迟(信号传播到负载和 回到源头)。 所有位置都存在此类信号完整性问题,沿着轨迹,除了负载端(见图 16)。

附录 B:反射系数

图 17:传输线并联负载端接

图 17 显示了以ZL的并联负载阻抗端接并由电压源信号驱动的传输线。 一旦信号到达线路另一侧的负载,其部分能量将被负载吸收,其余能量将反射回源。 反射信号与入射信号的比率称为反射系数,计算如下:

如果负载端接与走线相同的阻抗,即 ZL = Z0 ,则ΤL =0 ,这意味着没有反射信号。 如果负载阻抗与走线的阻抗不匹配,一些信号将反射回源。 反射信号的一小部分,一旦到达源,可以根据源反射系数再次反弹回负载,计算如下:

在负载处看到的整体反射是通过传输线的往返反射的结果,可以使用往返反射系数 ΤRT 计算如下:

![]()

较大的反射系数值会导致接收器输入端的信号余量减小、过度振铃和额外的触发边沿。 因此,为了在接收器端实现最佳信号完整性,应尽量减少往返反射。

附录 C:不同驱动强度选项下 SiTime 部件的输出阻抗

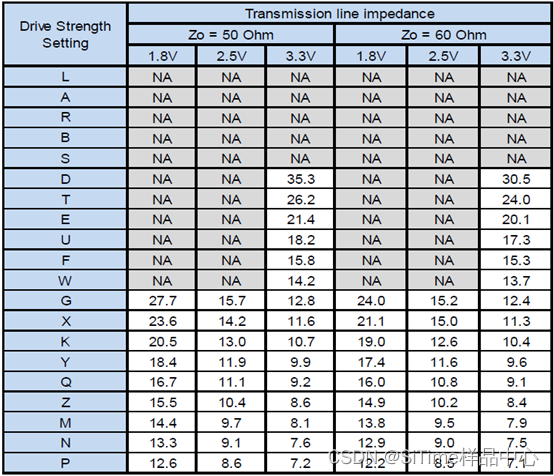

表 1:输出阻抗(SiT8208/9、SiT3807/8/9、SiT3907)

NA – 这些设置不推荐用于驱动长传输线

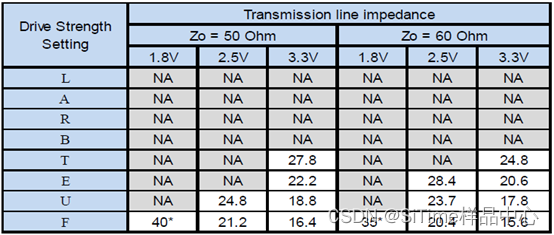

表 2:输出阻抗(SiT1602、SiT8008、SiT8009、SiT1618、SiT8918、SiT8919、SiT8920、SiT8921、SiT9201、SiT2002、SiT2018、SiT2019、SiT2020、SiT2021)

NA – 不推荐用于驱动长传输线的设置

* - 强烈建议使用 SiTime 提供的 IBIS 模型进行板级仿真,以确保可接受的信号完整性

关于SiTime公司

SiTime是一家专注于全硅MEMS时钟解决方案的Fabless半导体设计公司。公司成立于2005年,于2019年在美国纳斯达克上市。截至2021年底,全球累积出货量已超过20亿片,占据全球MEMS硅晶振市场90%以上份额。

SiTime采用MEMS技术与CMOS半导体技术相结合,依托先进的堆叠封装工艺制作而成。无需更改PCB设计,即可P2P完全替代所有传统石英振荡器产品。大尺度频率覆盖范围、国际标准封装、灵活的产品组合,快捷的可编程交付方式。所有产品可在24小时内提供32KHz--725MHz任一频率样品供应,实现更高性能时钟样品的快速交付。SiTime硅晶振以稳定的性能和超高的性价比成为了大多数高性能主控芯片的理想时钟选择和强健的心脏。不仅可以缩短研发周期,节约开发调试成本,而能降低未来产品返修风险,快给你的电路换上一颗SiTime硅晶振吧。

关于SiTime样品中心

SiTime样品中心成立于2014年,由SiTime公司联合北京晶圆电子有限公司共同创立,并由晶圆电子全权负责全面运营、客户服务以及国内的交付任务。SiTime样品中心宗旨是致力于加速SiTime硅晶振市场在大中华地区的应用普及,助力中国客户产品时钟解决方案升级换代。提供售前售后技术服务、24小时快速供样、以及国内中小批量现货支持和重要客户的全方位策略服务。更多资讯可访问SiTime样品中心官网(www.sitimechina.com)。

2384

2384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?