ch3 VHDL 语言程序的基本结构

一个完整的VHDL 语言程序通常包含实体、构造体、配置、包集合、库五部分组成。前四部分是可分别编译的源设计单元。实体用于描述所设计系统的外部接口信号,构造体用于描述系统的内部结构和行为,包集合用于存放各设计模块都能共享的数据类型、常数和子程序等,配置用于从库中选取所需单元来组成系统设计的不同版本,库存放已经编译的实体、构造体、包集合、配置。库可由用户生成或由ASIC芯片制造商提供。

3.1 VHDL 语言设计系统的基本单元及其构成

VHDL 语言设计的基本单元是VHDL语言的一个基本设计实体。由实体说明和构造体两部分组成。

3.1.1 实体说明

任何一个基本设计单元的实体说明都具有如下结构:

ENTITY 实体名 IS

[类属参数说明];

[端口说明];

END ENTITY 实体名;

VHDL 语言大小写不区分,这里只是为了阅读方便。

1 类属参数说明

类属参数说明必须放在端口说明之前,用于指定参数。

GENERIC (m:TIME:=1ns);

用于指定构造体内m的值为1ns

tmp1:=d0 AND sel AFTER m;

表示两个输入信号相与后经1ns延迟送到temp1

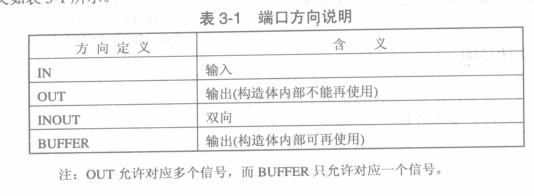

2 端口说明

端口说明对基本设计实体(单元)与外部接口的描述,也可以说是对外部引脚信号的数据名称、数据类型,以及输入、输出方向的描述,一般书写格式如下:

PORT(端口名{,端口名}:方向 数据类型名;

...

端口名{,端口名}:方向 数据类型名);

1)端口名 赋予每个外部引脚名称,通常用一个或几个英文字母,或英文字母加数字来命名。

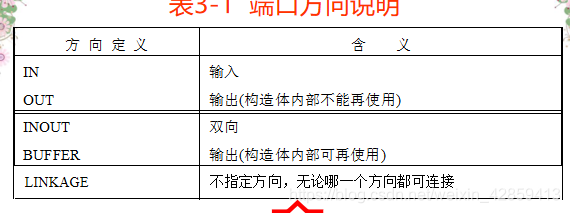

2)端口方向 定义外部引脚的信号方向是输入还是输出。

3)数据类型

VHDL有10中数据类型,但是在逻辑电路中只用到了两种:BIT和BIT_VECTOR。这里的逻辑电路并非数字电路,只是描述语言里边设计的电路

BIT是位逻辑数据类型,其值只能是两个逻辑值(“0”和“1”)中的一个。当端口被说明为BIT_VACTOR数据类型时,该端口的取值可能是一组二进制值。

PORT(d0,d1,sel:IN BIT;

q:OUT BIT;

bus:OUT BIT_VECTOR(7 DOWNTO 0));

7 DOWNTO 0 表示bus端口是一个8位端口值,由B7~B0共8位组成。位矢量长度为8位。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux IS

PORT(d0,d1,sel:IN STD_LOGIC;

q:OUT STD_LOGIC;

bus:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY mux;

3.1.2 构造体

构造体是一个基本设计单元的功能描述体,它具体指明了该基本设计单元的行为、元件及内部的连接关系。也就是说,它定义了设计单元的具体功能。构造体对其基本设计单元的输入、输出关系可以用3种方式进行描述,即行为描述(基本设计单元的数学模型描述)、寄存器传输描述(数据流描述)和结构描述(逻辑元件连接描述)。不同的描述方式只体现在描述语句上,而构造体的结构是一样的。

一个构造体的具体结构如下:

ARCHITECTURE 构造体名 OF实体名 IS

[定义语句] 内部信号,常数,数据类型,函数等的定义;

BEGIN

[并行处理语句];

END ACHITECTURE 构造体名

1 构造体名称的命名

构造体的名称是对本构造体的命名,是该构造体唯一的名称。OF后的实体名表示该构造体所对应的是哪一个实体。用IS来结束构造体的命名。

构造体的名称可由用户自由命名,但多数情况下,命名为behavioral(行为),dataflow(数据流),structural(结构)。

2 定义语句 位于ARCHITECHURE和BEGIN之间,用于对构造体内部所使用的信号、常数、数据类型和函数进行定义,例如:

ARCHITECTURE behav OF mux IS

SIGNAL nes1:BIT;

...

BEGIN

...

END ARCHITECHURE behav;

信号定义和端口说明的语句一样,应有信号名和数据类型的说明。因是内部信号的说明,不需有方向。

3并行处理语句

位于BEGIN 和END 之间,这些语句描述了构造体的行为及其连接关系。

例如二选一数据流的方式描述

ENTITY mux IS

PORT(d0,d1: IN BIT;

sel: IN BIT;

q: OUT BIT );

END ENTITY mux;

ARCHITECTURE dataflow OF mux IS

BEGIN

q<=(d0 AND sel)OR(NOT sel AND d1);

END ARCHITECTURE dataflow;

符号<=表示传送(或代入)的意思,即将逻辑运算结果送q输出。

在构造体中的语句都是并行执行的,语句的执行不以书写语句顺序为执行顺序。

3.2 VHDL语言构造体的子结构描述

一个构造体可以用几个子结构,即相对比较独立的几个模块来构成。

3种形式:(1)BLOCK语句结构

(2)PROCESS语句结构

(3)SUBPROGRAM语句结构

3.2.1 BLOCK语句结构描述

1.BLOCK语句结构

块结构名:

BLOCK

BEGIN

……

END BLOCK 快结构名;

例题3-4 采用BLOCK语句描述二选一电路

ENTITY mux IS

PORT(d0,d1,sel:IN BIT;

q:OUT BIT);

END ENTITY mux;

ARCHITECTURE connect OF mux IS

SIGNAL tmp1,tmo2,tmp3:BIT;

BEGIN

cale

BLOCK

BEGIN

tmp1<=d0 AND sel;

tmp2<=d1AND (NOT sel);

tmp3<=tmp1 OR tmp2;

q<=tmp3;

END BLOCK cale;

END ARCHITECTURE connect;

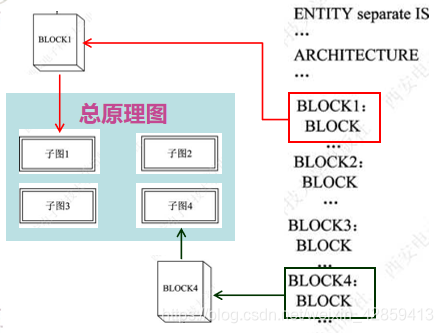

2.BLOCK块和子原理图的关系

构造体可由多个BLOCK块构成

每一个BLOCK块对应一张子原理图

采用BLOCK结构有利于编程、查错、仿真、和再利用。

3.BLOCK中语句的并发性

BLOCK语句中所描述的各个语句是并行执行的和书写顺序无关。又称并发语句。

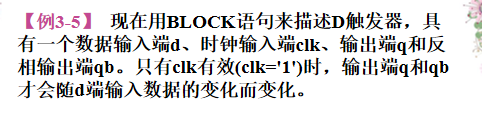

4.卫式BLOCK

(1)当某一条件得到满足时,BLOCK语句才被执行

(2)当条件不满足时,不执行BLOCK 语句。

ENTITY latch IS

PORT(d,clk: IN BIT;

q,qb: OUT BIT);

END ENTITY latch;

ARCHITECTURE latch_guard OF latch IS BEGIN

G1:

BLOCK(clk='1')//卫式布尔表达式

BEGIN

q<=GUARDED d AFTER 5ns;//前卫关键词

qb<=GUARDED NOT(d) AFTER 7ns;

END BLOCK G1;

END ARCHITECTURE latch_guard;

3.2.2 PROCESS语句结构描述

1.PROCESS语句的结构

[进程名]:PROCESS(信号1,信号2,……)IS

BEGIN

……

END PROCESS

有[]表示可以省略

【例3-6】 用PROCESS语句结构描述的程序如下:

ENTITY mux IS

PORT(d0, d1, sel: IN BIT;

q: OUT BIT);

END ENTITY mux;

ARCHITECTURE connect OF mux IS

BEGIN

cale: PROCESS(d0, d1, sel) IS

VARIABLE tmp1, tmp2, tmp3: BIT;

BEGIN

tmp1:=d0 AND sel;

tmp2:=d1 AND (NOT sel);

tmp3:=tmp1 OR tmp2;

q<=tmp3 ;

END PROCESS cale;

END ARCHITECTURE connect;

2.PROCESS中语句的顺序性

PROCESS结构中语句按顺序一条一条向下执行

SUBPROGRAM语句也是如此

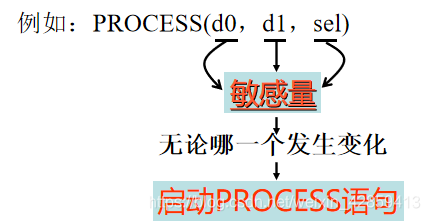

3.PROCESS的启动

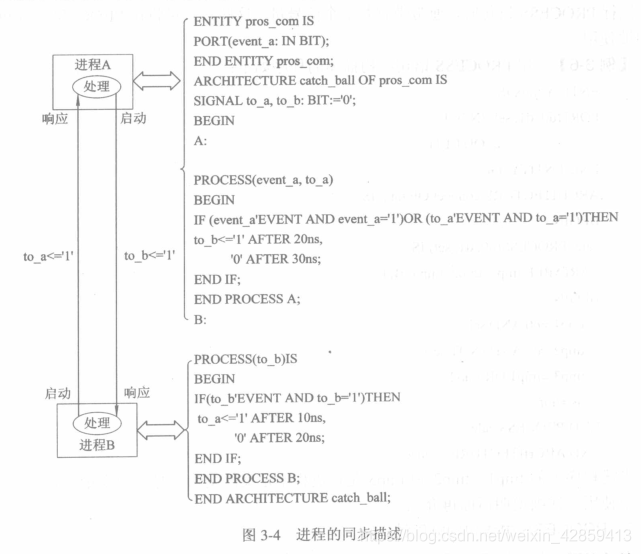

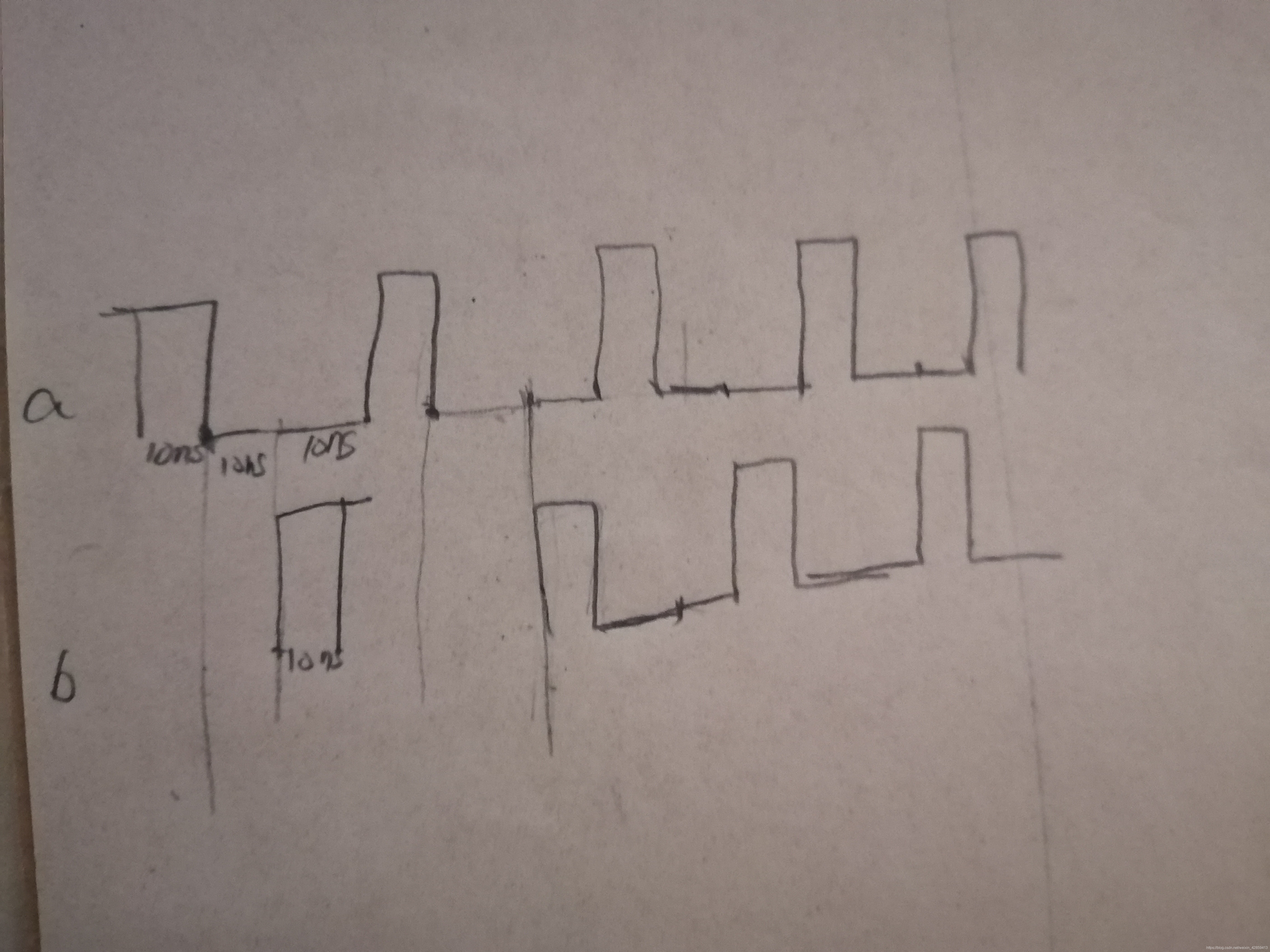

4.PROCESS的同步描述

#同一个构造体中可以有多个进程存在

#各PROCESS之间可以一边进行通信,一边并发地同步执行

周期为30ns的周期性矩形波

3.2.3 SUBPROGRAM语句结构描述

子结构在调用时首先进行初始化

执行结束后子程序终止

再调用时要再进行初始化

属于非重入的程序

(子程序内部的值不能保持,子程序返回以后才能被调用)

存放在包集合里

子程序的两种类型

(1)过程(Procedure)

(2)函数(Function)

1.过程语句

1)结构

PROCEDURE 过程名(参数1;参数2;…)IS

[定义语句];--变量等定义

BEGIN

[顺序处理语句];--过程的语句

END PROCEDURE 过程名;

这里的定义语句是局部变量,构造体开始时的定义语句是全局变量

参数包含输入参数和输出参数

【例3-7】用过程语句来实现将位矢量转换为整数

PROCEDURE vector_to_int

( z: IN STD_LOGIC_VECTOR;

x_f1ag: OUT BOOLEAN;

q: INOUT INTEGER) IS

BEGIN

q:=0;

x_f1ag:=FALSE; -- q和x_f1ag 均为该过程中的变量 FOR i IN z'RANGE LOOP

q:=q*2;

IF(z(i)=1) THEN

q:=q+1;

ELSIF(z(i)/=0) THEN //z[i]不为0

x_f1ag:=TRUE;

END IF;

END LOOP;

END PROCEDURE vector_to_int;

该过程调用后,如果x_flag=true,则说明转换失败,不能得到正确的转换整数值。

2.函数语句

1)函数语句的结构

这里的参数只有输入参数,所以IN可省略

FUNCTION 函数名(参数1;参数2……)

RETURN 数据类型名 IS

[定义语句];

BEGIN

[顺序处理语句];

RETURN [返回变量名];

END FUNCTION [函数名];

例3-9包集合中的FUNCTION语句的程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

**PACKAGE bpac IS

FUNCTION max(a: STD_LOGIC_VECTOR;

b:STD_LOGIC_VECTOR)

RETURN STD_LOGIC_VECTOR;

END bpac;** 包首

PACKAGE BODY bpac IS //包体

FUNCTION max(a:STD_LOGIC_VECTOR;

b:STD_LOGIC_VECTOR)

RETURN STD_LOGIC_VECTOR IS

VARIABLE tmp:STD_LOGIC_VECTOR(a'RANGE);

BEGIN

IF(a>b) THEN

tmp:=a;

ELSE

tmp:=b;

END IF;

RETURN tmp;

END FUNCTION max;

END bpac;

2)函数调用及结果的返回

例3-10 调用FUNCTION语句的过程

LIBRARY IEEE;

LIBRARY WORK; //放用户定义的库

USE IEEE.STD_LODIC_1164.ALL;

USE WORK.bpac.ALL;//用户定义的包集合

ENTITY peakdetect IS

PORT(data:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

clk,set:IN STD_LOGIC;

dataout:OUT STD_LOGIC_VECTOR(5 DOWNTO 0));

END ENTITY peakdetect;

ARCHITECTURE rtl OF peakdetect IS

SIGANL peak:STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

dataout<=peak;

PROCESS(clk) IS

BEGIN

IF(clk'EVENT AND clk='1') THEN

IF(set='1') THEN

peak<=data;

ELSE

peak<=MAX(data,peak);

END IF;

END PROCESS;

END ARCHITECTURE rtl;

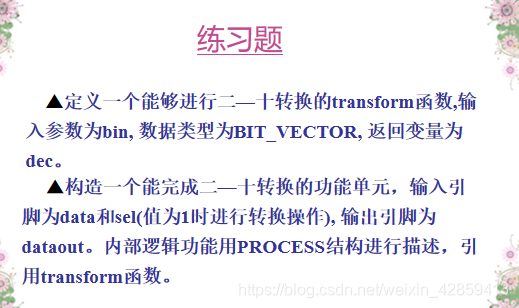

包有包首和包体。

PACKAGE bpac IS

FUNCTION transform(bin:BIT_VECTOR)

RETURN INTEGER;

END bpac;

PACKAGE BODY OF bpac IS

FUNCTION transform(bin:BIT_VECTOR)//不指定位数,使包的输入值位数不受限制

RETURN INTEGER IS

VARIABLE dec:INTEGER;

BEGIN

dec:=0;

FOR i IN bin'RANGE LOOP//取bin的位标号,不指明i,就为默认int型,由高到低,从左到右

dec:=dec*2;

IF(bin(i)='1') THEN

dec:=dec+1;

END IF;

END LOOP;

RETURN dec;

END transform;

END bpac;

LIBRARY WORK;

USE WORK.bpac.ALL;

ENTITY value IS

PORT(data:IN BIT_VECTOR;

sel:IN BIT;

dataout:OUT INTEGER);

END ENTITY;

ARCHITECTURE behav OF value IS

SIGNAL v:INTEGER;

BEGIN

dataout<=v;

PROCESS(data)

BEGIN

IF(sel='1') THEN

v<=transform(data);

END IF;

END PROCESS;

END behav;

BIT_VECTOR不用声明库,它在标准库里,默认有标准库。

BIT_VECTOR是VHDL十种数据类型中的一种

定义的变量在is和begin之间

循环语句有两种

logic有9种值,在2-10转换时需要判断是否为“0”或“1”。

功能单元说明要设计一个实体

特殊的子结构都有begin

3.3包集合、库及配置

除了实体和构造体之外,包集合、库及配置是VHDL语言中另外3个可以各自独立进行编译的源设计单元。

3.3.1库

定义:库(Library)是经编译后的数据的集合,它存放包集合定义、实体定义、构造体定义和配置定义。

库和库之间是独立的,不能互相嵌套。

1.库的种类

1)IEEE库(STD_LOGIC_1164)

2) STD库 -VHDL的标准库

3)面向ASIC的库(门级仿真中使用)

——存放着与逻辑门对应的实体

4)WORK库(现行作业库)

——存放用户自己设计的工程项目

5)用户定义库

——存放用户为自身设计需要而开发的包集合

WORK库是用户自定义库的一种,作用等同STD库

2.库的使用

除了WORK库和STD库以外,其他三类库在使用前都要做出说明。

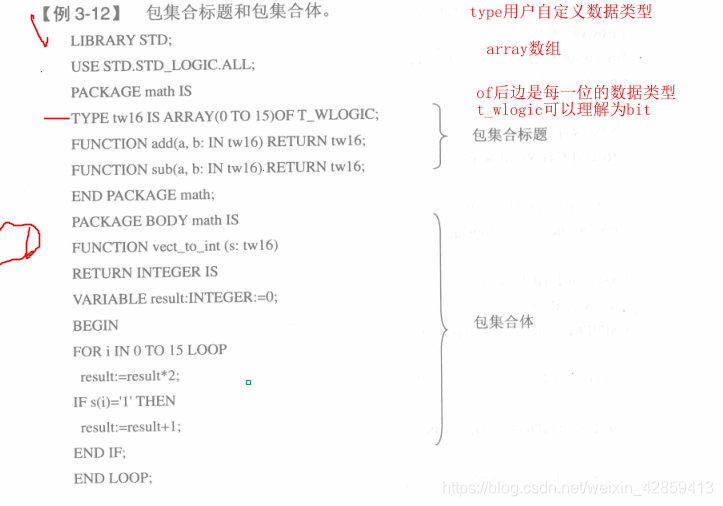

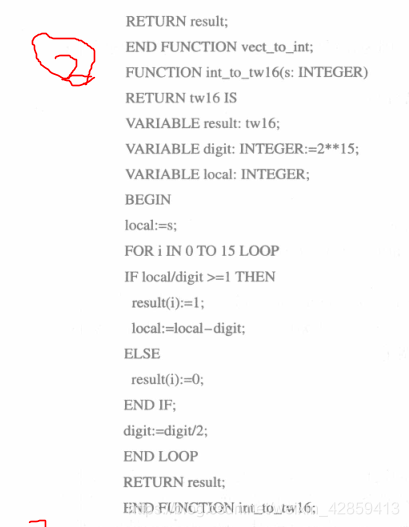

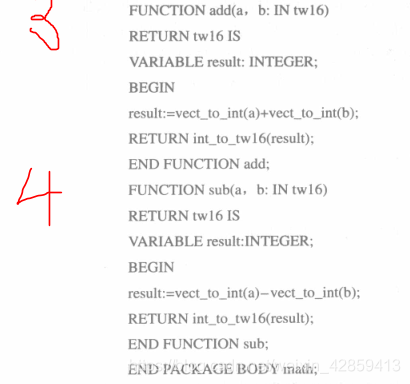

3.3.2包集合

包集合(Package)用来罗列VHDL语言中所要用到的信号定义、常数定义、数据类型、元件语句、函数定义和过程定义等,是一个可编译的设计单元,也是库结构的一个层次。要使用包集合时可以用USE语句说明,

包集合的结构

PACKAGE 包集合名 IS

[说明语句];

END PACKAGE 包集合名;包集合标题

PACKAGE BODY 包集合名 IS

[说明语句];

END PACKAGE BODY 包集合名;包集合体

一个包集合由两大部分组成:包集合标题(Header)和包集合体。包集合体(Package body)是一个可选项。也就是说,包集合可以只由包集合标题构成。一般包集合标题列出所有项的名称,而包集合体具体给出各项细节

使用包集合时用USE语句说明

USE IEEE.STD_LOGIC_1164.ALL;

包集合可以只有包集合标题

包集合只有一个包集合标题举例

LIBRARY IEEE;

USE IEEE STD_LOGIC_1164.ALL;

PACKAGE upac IS

CONSTANT k:INTEGER:=4;

TYPE instruction IS(add,sub,adc,inc,srf,slf);

SUBTYPE cpu_bus IS STD_LOGIC_VECTOR(k-1 DOWNTO 0);

END PACKAGE upac;

声明的一个常数

CONSTANT k:INTEGER:=4;

用户自定义的数据类型,枚举类型 是()中的一个

TYPE instruction IS(add,sub,adc,inc,srf,slf);

用户定义的一个类型,k位数据,即4位

SUBTYPE cpu_bus IS STD_LOGIC_VECTOR(k-1 DOWNTO 0);

调用

USE WORK.upac.inctruction;

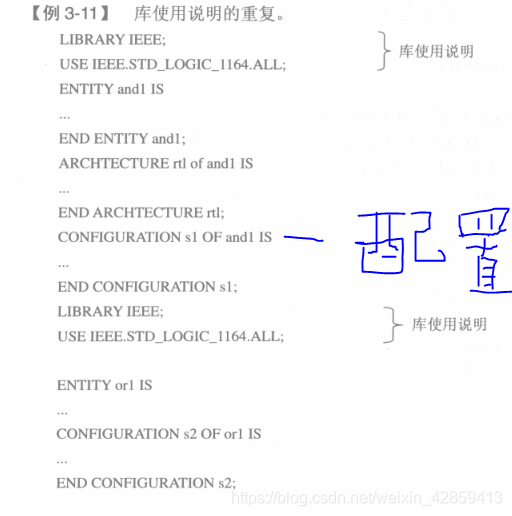

3.3.3配置

配置(Configuration)语句描述层与层之间的连接关系以及实体与结构之间的连接关系。

配置的基本格式

CONFIGURATION 配置名 OF 实体名 IS

[语句说明];

END CONFIGURATION 配置名;

1630

1630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?