引脚组成

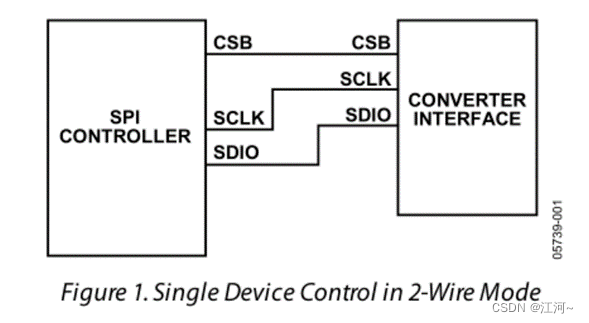

SPI端口由三个引脚组成:

串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)和芯片选择条引脚(CSB)。 某些芯片包含串行数据输出引脚(SDO),为了最大限度地减少引脚数量,大多数芯片都省略了此引脚。 SDO仅用于从设备读取数据。

引脚定义

SERIAL CLOCK (SCLK)

SCLK:串行移位时钟输入引脚。该引脚由施密特触发器实现,以最大限度地降低对时钟线上噪声的敏感性。SCLK用于同步串行接口的读写。输入数据在该时钟的上升沿记录,输出数据传输在下降沿记录。

SERIAL DATA INPUT/OUTPUT (SDIO)

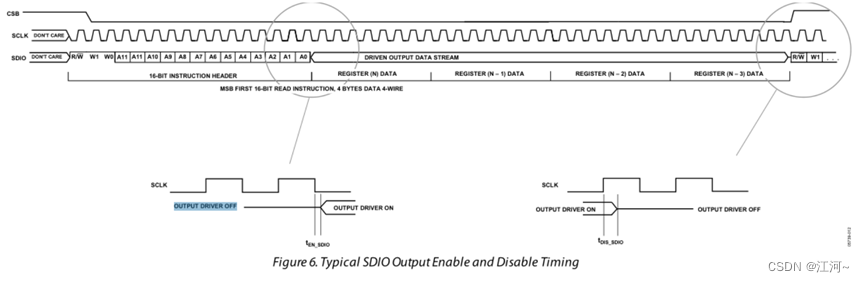

SDIO引脚是一个两用引脚。该引脚的典型作用是作为输入或输出,这取决于发送的指令(读或写)和时序帧中的相对位置(指令或数据相位)。在写入或读取的第一阶段,该引脚用作将信息传递给内部状态机的输入。如果该命令被确定为读取命令,则状态机将该引脚(SDIO)更改为输出,然后将数据传回控制器。如果设备包括SDO引脚,并且配置寄存器被设置为利用它,则SDO变为活动,而不是SDIO引脚变为输出。在所有其他时间,SDO引脚都保持在高阻抗状态。如果该命令被确定为写入命令,则SDIO引脚在该指令的持续时间内保持输入。

CHIP SELECT BAR (CSB)

CSB是一种对读和写周期进行门控的有源低电平控制。

当CSB线路为低电平时,设备被选择,SCLK和SDIO线路上的信息被处理。如果该引脚为高电平,则设备将忽略SCLK和SDIO线上的任何信息。通过这种方式,可以将多个设备连接到SPI端口。在只连接一个设备的情况下,CSB线可以选择性地连接为低电平,并且设备将永久启用。

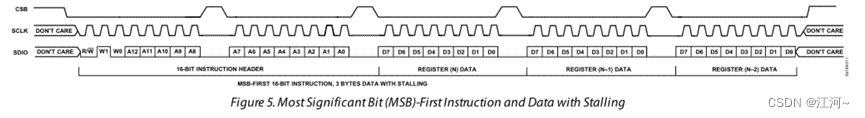

在某些配置中,CSB可能会停滞在高电平,即在多个时钟周期内保持高电平(见图5),以允许额外的外部定时。如果一次通过接口传输三个或更少的字(不计算指令信息),则CSB可能在包括指令信息的字节在内的字节之间停滞在高位。如果CSB在字节的中间停在高位,则状态机被重置,并且控制器返回空闲状态,等待新指令的传输。该机制允许在检测到故障后进行恢复。要检测重置,必须至少出现一个且不超过七个串行时钟。一旦状态机进入空闲状态,CSB的下一个下降沿启动新的传输周期。

一些设备使用SPI引脚实现辅助功能。通常,这些功能包括输出数据格式、占空比稳定器或其他常见功能。这些引脚功能由CSB引脚启用。如果CSB引脚连接为高电平,SPI功能将置于高阻抗模式。在这种模式下,辅助功能将打开,从而允许在不需要SPI操作的情况下控制芯片上的功能。这些功能因设备而异。

时序图

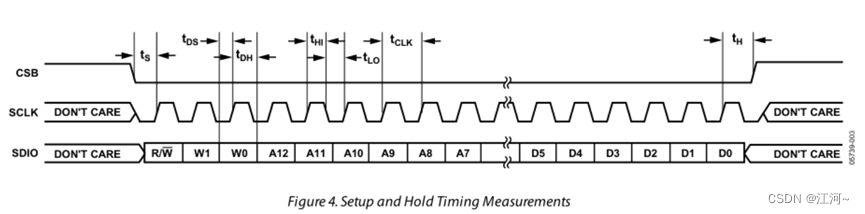

CSB的下降沿与SCLK的上升沿一起决定了成帧的起始点。一旦确定了帧的开始,时间就很简单了。传输的第一个阶段是指令阶段,它由16位组成,后面是可以是8位倍数的可变长度的数据。如果设备配置为CSB为低电平,则成帧从SCLK的第一个上升沿开始。

5978

5978

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?