stm32f103系统时钟初始化(寄存器)

一、思路

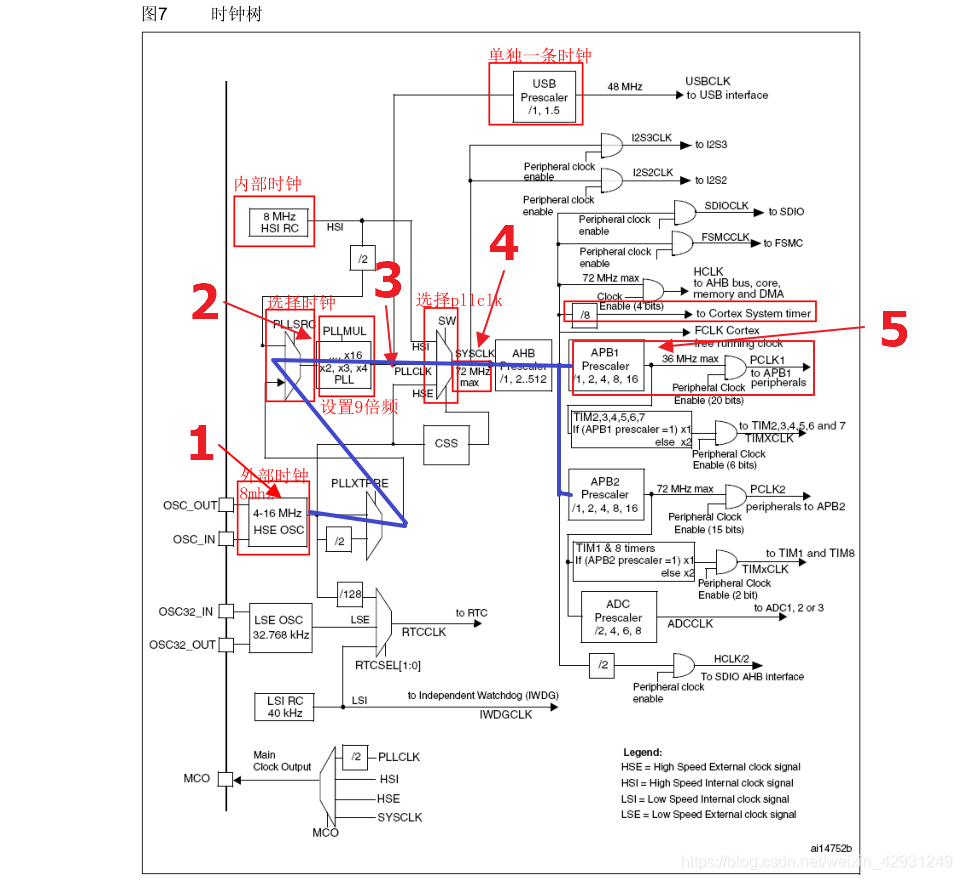

- 打开 HSE 外部时钟,设置默认不分频

- 选择 HSE 作为 PLLCLK 后,设置9倍频(因为 HSE 为 8MHz,9倍频后 8*9 = 72MHz,因为 SYSCLK 最大值为72MHz),然后使能PLL电路

- 选择 PLLCLK 作为 SYSCLK (系统时钟),切换 SYSCLK 时需要重新设置 FLASH 时延,以保证能正确读取内存

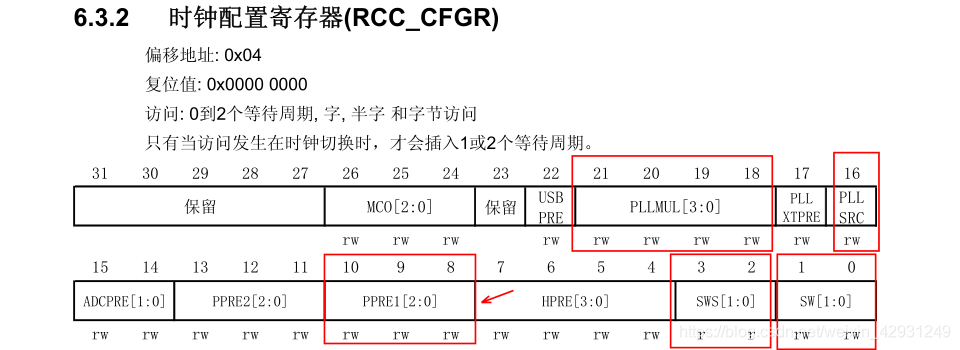

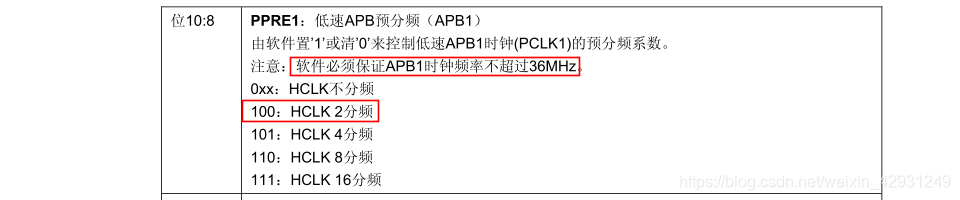

- 设置 APB1 为 2 分频(72/2 = 36MHz ,因为 APB1 的最大速度为 36MHz

二、 system_init()代码

void system_init(){

//1.开启外部时钟 HSE

RCC->CR |= 1 << 16;

//等待外部时钟HSE就绪

while ((RCC->CR & (1 << 17)) == 0) {}

//2. PLLCLK设置

//设置 PLL 倍频系数 9倍频

RCC->CFGR |= 7 << 18;

//设置 HSE 作为 PLLCLK 输入源

RCC->CFGR |= 1 << 16;

//3. 打开 PLL 电路

RCC->CR |= 1 << 24;

//等待 PLL 电路就绪

while ((RCC->CR & (1 << 25)) == 0) {};

//4. 设置 FLASH 时延 让HSE能正常工作

FLASH->ACR |= 1<<1;

//5. SYSCLK设置

//设置 PLL 作为 SYSCLK 输入源

RCC->CFGR |= 1 << 1;

//等待 SYSCLK 就绪

while ((RCC->CFGR & (1 << 3)) == 0) {};

//6. 设置 AHP1 预分频系数为2

RCC->CFGR |= 1 << 10;

}

三、 分步讲解

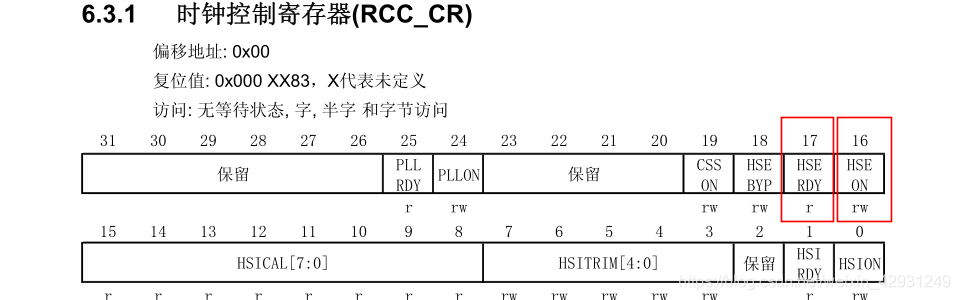

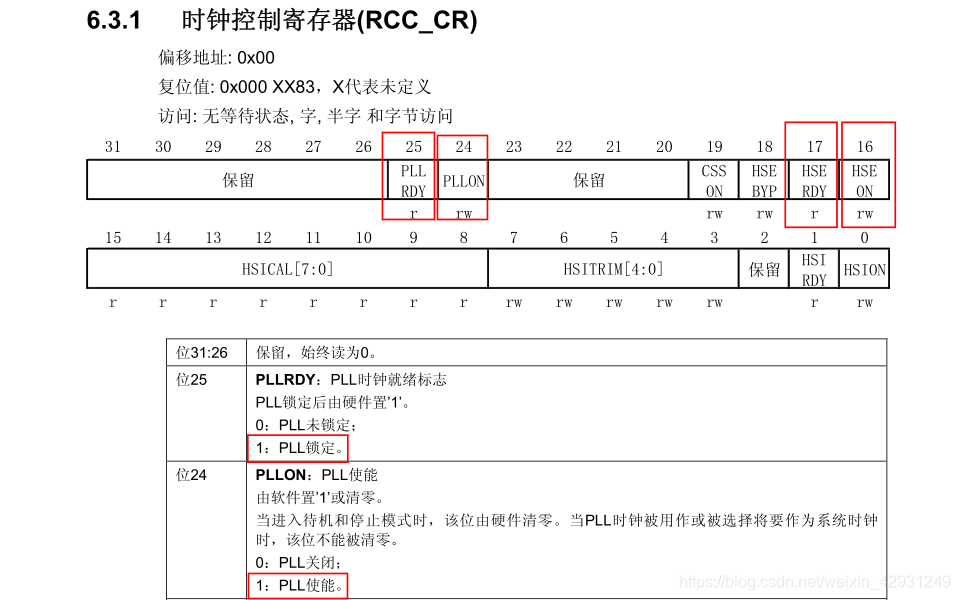

1. 开启外部时钟 HSE

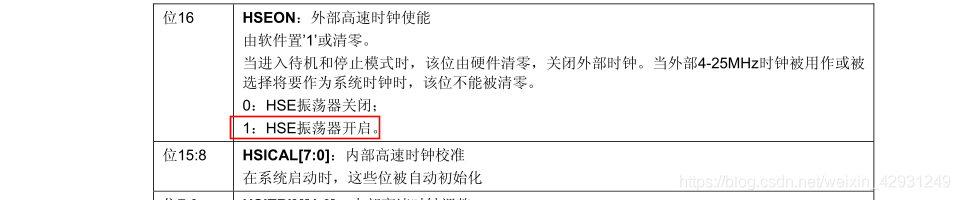

//开启外部时钟 即 RCC->CR 第16位置为1

RCC->CR |=1<<16;

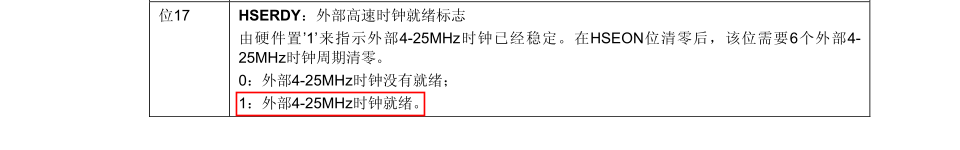

//当16位为1是 第17位会马上自动置为1 只有当16、17都为1时才代表外部时钟开启 所以需要等待17位置为1

while (RCC->CR&(1<<17)==0){}

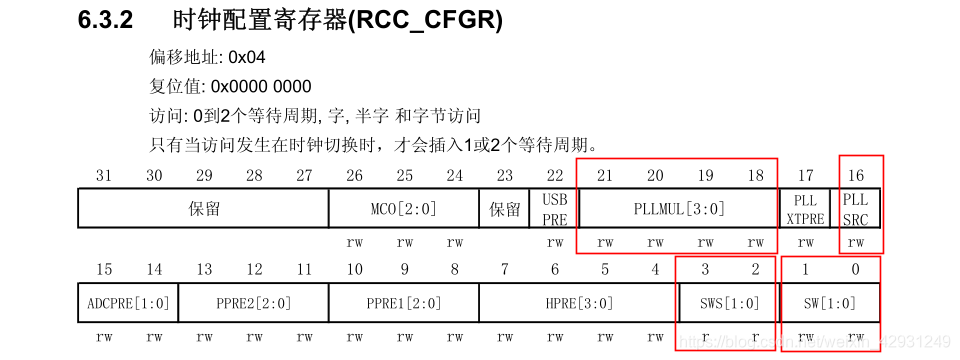

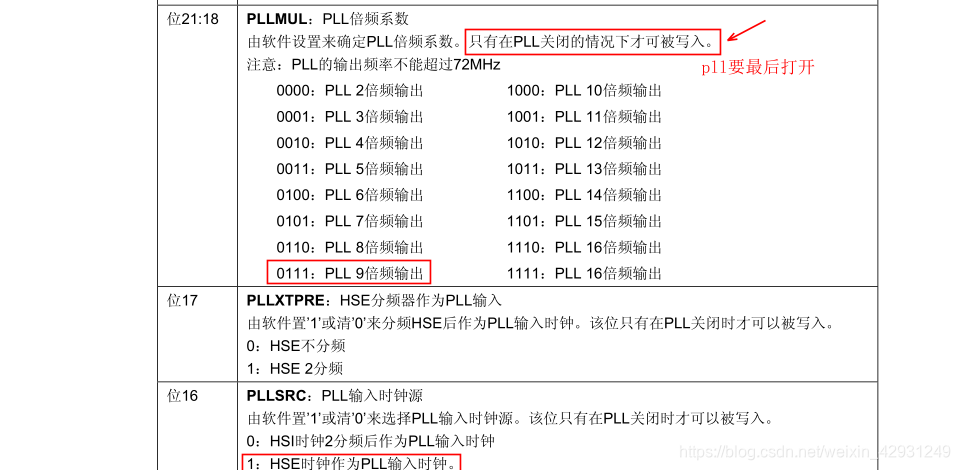

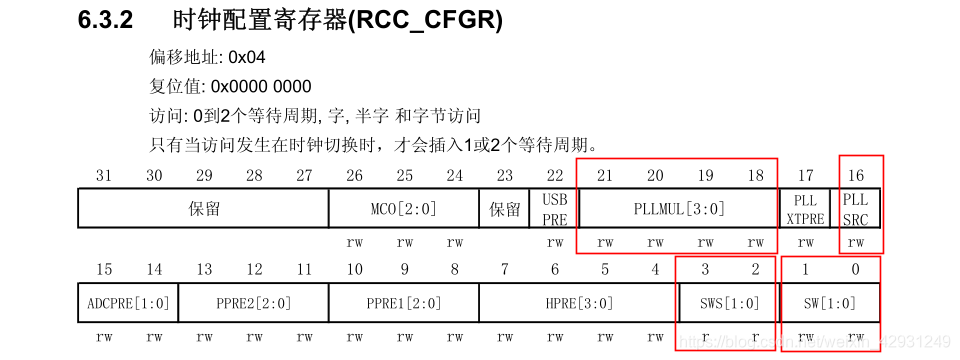

2. PLLCLK设置

//设置 PLL 倍频系数 9倍频

RCC->CFGR |= 7 << 18;

//设置 HSE 作为 PLLCLK 输入源

RCC->CFGR |= 1 << 16;

3. 打开 PLL 电路

//打开 PLL 电路

RCC->CR |= 1 << 24;

//等待 PLL 电路就绪

while ((RCC->CR & (1 << 25)) == 0) {};

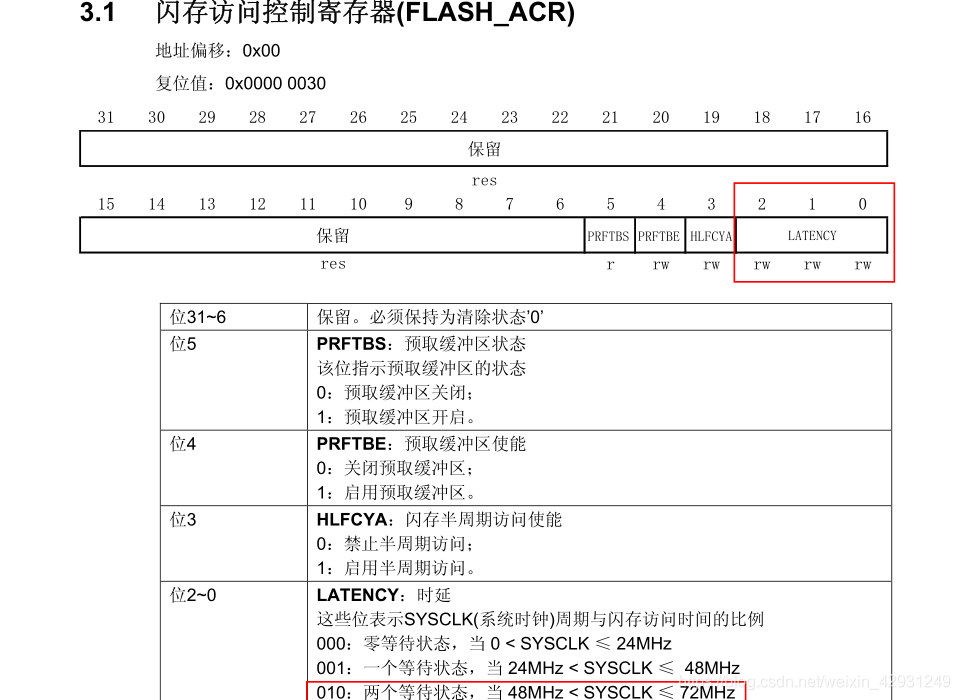

4. 设置 FLASH 时延

//设置 FLASH 时延 保证能正确读取内存中的内容

FLASH->ACR |= 1<<1;

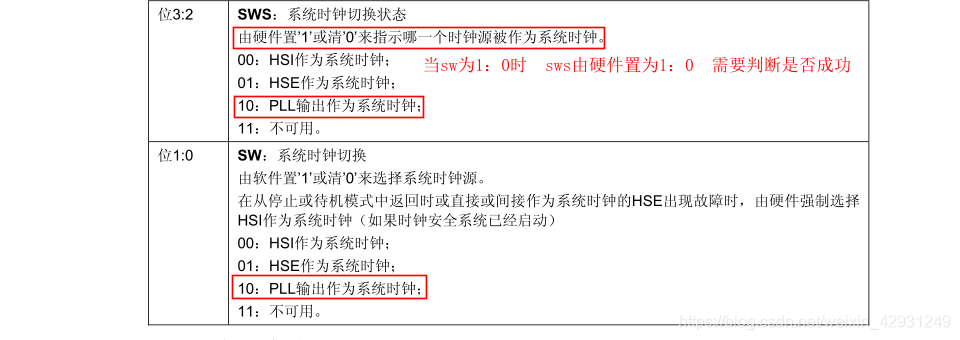

5. SYSCLK设置

//设置 PLL 作为 SYSCLK 输入源

RCC->CFGR |= 1 << 1;

//等待 SYSCLK 就绪

while ((RCC->CFGR & (1 << 3)) == 0) {};

6. 设置 AHP1 预分频系数为2

//6. 设置 AHP1 预分频系数为2

RCC->CFGR |= 1 << 10;

本文详细介绍了STM32F103系统时钟初始化过程,包括打开HSE外部时钟,设置PLLCLK为72MHz,切换SYSCLK并设置FLASH时延,最后设置APB1为36MHz。

本文详细介绍了STM32F103系统时钟初始化过程,包括打开HSE外部时钟,设置PLLCLK为72MHz,切换SYSCLK并设置FLASH时延,最后设置APB1为36MHz。

2819

2819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?