功率 MOS 管是高 di/dt 的元件,并且流过大电流,这就意味着它是主要的干扰源,如果 对功率 MOS 管布局布线不正确,你设计的电源将遇到诸多难题。遵守以下准则可以事半功倍。

(1)最小化高边 MOSFET,低边 MOSFET 以及输入电容封闭形成的环路面积。

(2)把低边 MOSFET 的源极与输入电容接地点相连,然后连接到接地平面。

(3)用铺铜实现漏极和栅极到电源 FET 的连接。

(4)使用大量过孔连接到内层。

(5)最小化电源通道上的杂散电感!

如同前面的讨论,输入电容器、高边(high side)FET 以及低边(low side)FET 之间 的环路需要最小化。在降压设计中,这可能是最关键的通道。应当遵循前面提到的关于在输 入电容器接地点对低边 FET 源极进行接地的规则,以及确保连接主电源与 MOSFET 的走线足 够粗。这对供电和散热都有好处。

同样的原则也适用于过孔。过孔越多越好。想想并联连接的全部电感(并联使过孔的电 感减小)。它们还作为电路板背面和内层的热量通道。尽可能利用焊料填充过孔。尽管在供 电与散热方面不如铜箔,但焊料还是优于空气,而且它也是填充过孔的材料。顺便说一下, 要确保电源通道中的寄生电感最小。

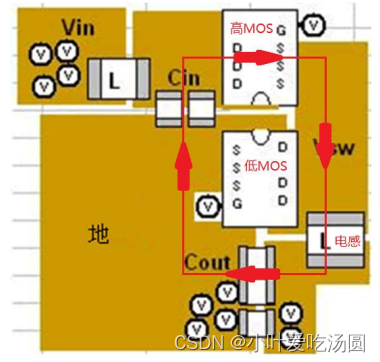

下图是功率 MOS 管和去耦电容的一个布局例子。

从这个布局图中可以看到:功率元件布局紧凑,组成的高 di/dt 环路面积最小。低边 MOS 管的源极(S)跟 Cin 的 GND 就近连接。用覆铜取代走线连接各功率元件,可以使通道上 的寄生电感减小,有利于消除毛刺干扰。

文章介绍了如何通过最小化高边和低边MOSFET的环路面积,优化连接,使用覆铜和大量过孔来降低电源设计中的干扰和提高效率。关键点包括低边MOSFET源极的接地处理,以及重视过孔的数量和填充以改善散热和电感。

文章介绍了如何通过最小化高边和低边MOSFET的环路面积,优化连接,使用覆铜和大量过孔来降低电源设计中的干扰和提高效率。关键点包括低边MOSFET源极的接地处理,以及重视过孔的数量和填充以改善散热和电感。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?