一.总体概括

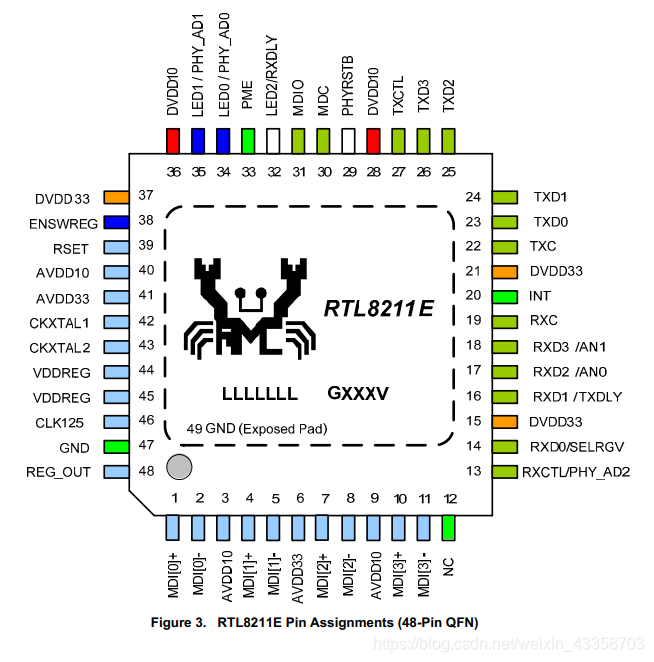

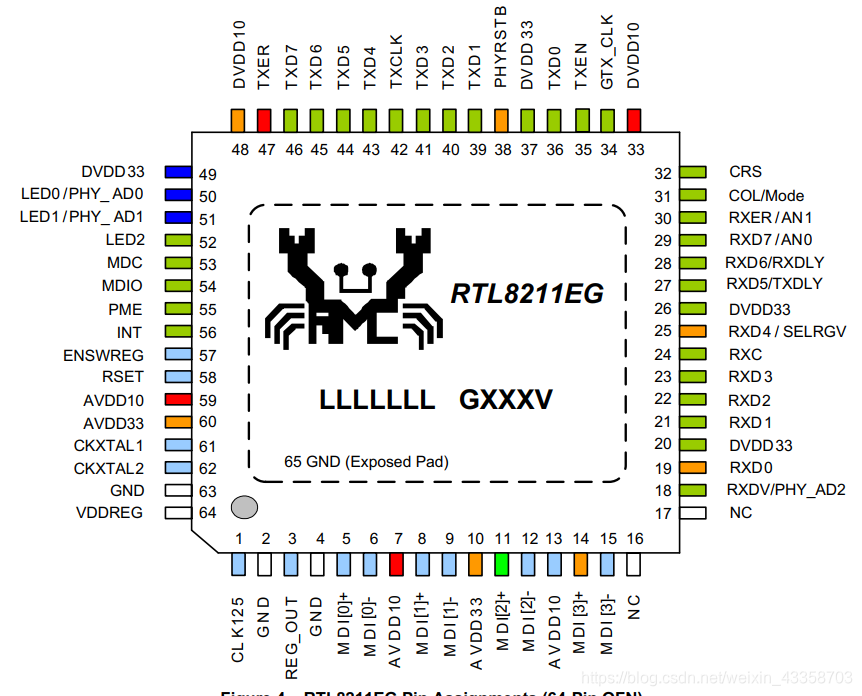

千兆以太网的理论网速为1000Mbit/s,实际网速接近该值,但几乎不可能达到,但相对于百兆网,网速快了很多。目前千兆以太网常用物理层接口有GMII和RGMII,两种接口有同有异,应用情况也有所差别。GMII占用的引脚较多,RGMII可以很大程序地减少引脚的使用。因此本设计采用RGMII接口进行设计,物理层芯片采用RTL8211E,根据以太网数据帧的要求并遵循相关时序要求,编写FPGA的Verilog代码,实现了千兆以太网UDP的通讯。

二.RGMII接口介绍

2.1 RGMII接口简介

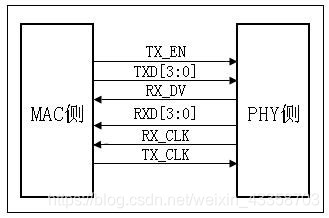

RGMII采用11根信号线即可实现以太网通讯,大大减少了信号的数量,节约了硬件电路板的面积,RGMII 接口如图1所示。

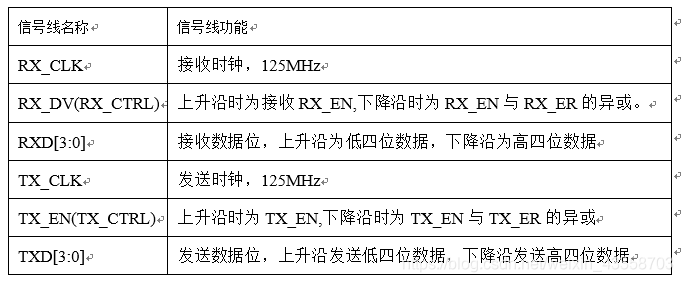

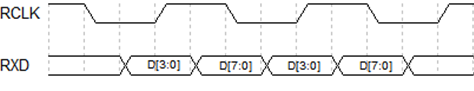

TX_EN、TX_ER、RX_EN、RX为高电平时有效,即为高电平时表示使能或者有错误,因此,有效数据(数据线有数据且数据无误)接收期间,RX_CTRL为高电平;当数据发送期间,需要将置为TX_CTRL为高电平,表示数据发送使能且数据无误。RGMII数据接收(发送与接收一致)时序如图2所示。

三.以太网数据帧

在使用FPGA进行千兆以太网实现时,需要对物理层的数据流进行处理,因此需要对以太网数据帧、IP数据包格式、UDP数据包等数据包进行学习。

3.1 802.3以太网数据帧

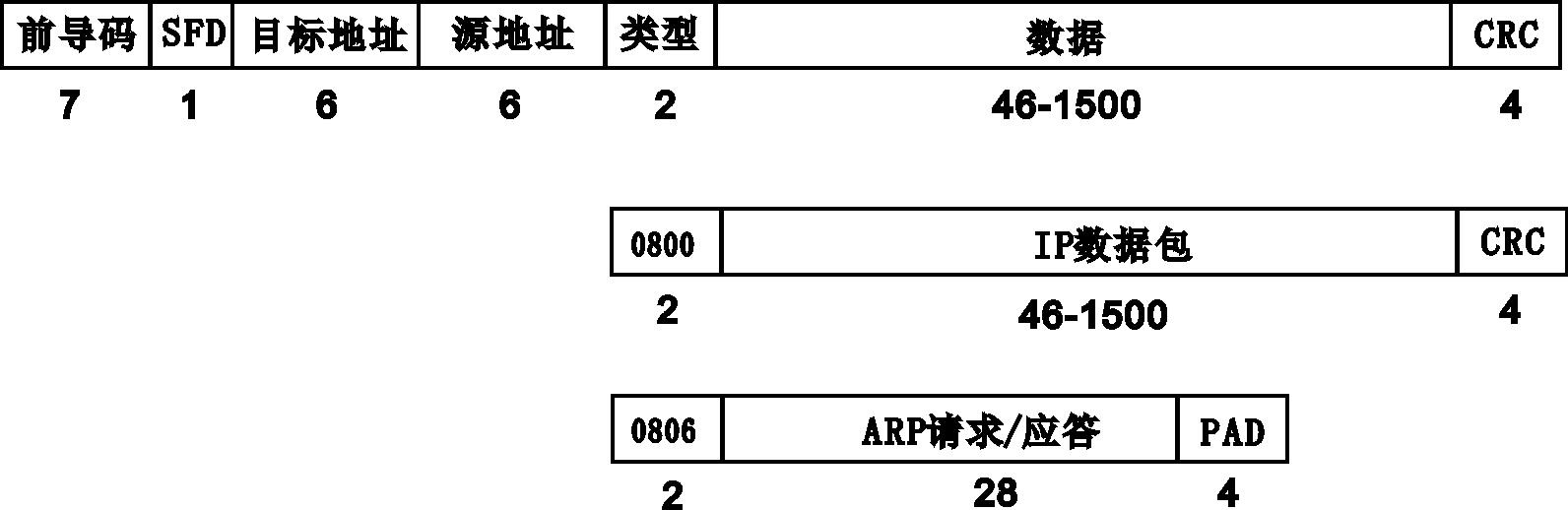

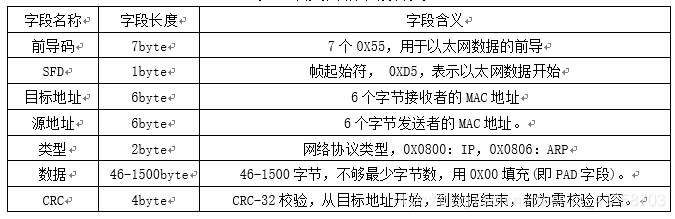

以太网数据帧如图5所示,每个字段含义如表2所示。

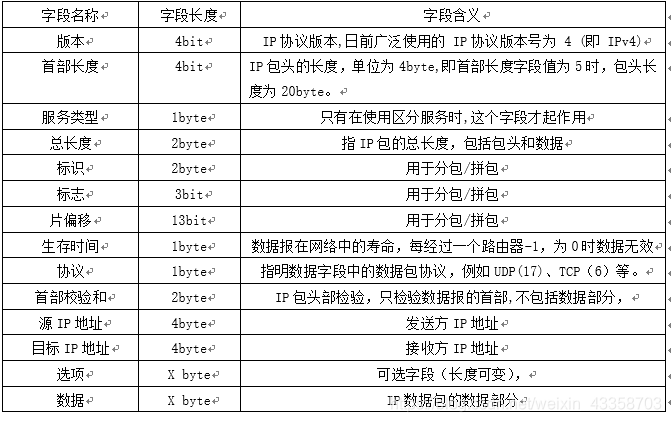

3.2 IP数据包格式

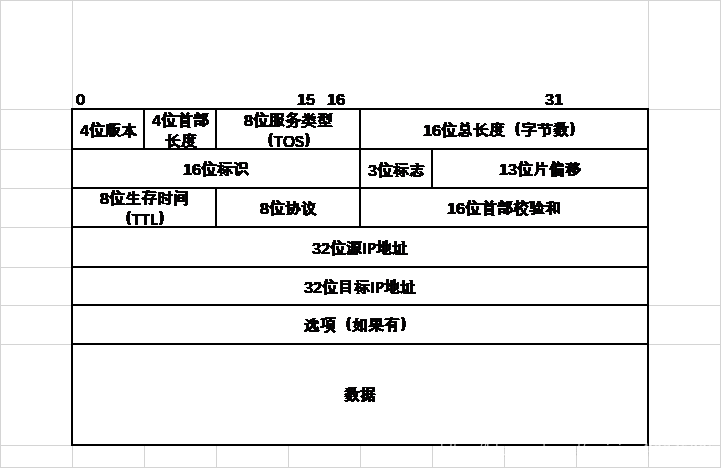

IP数据以数据的形式包含在以太网数据帧中,其格式如图所示,各字段含义如表所示。

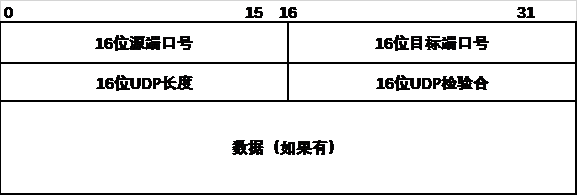

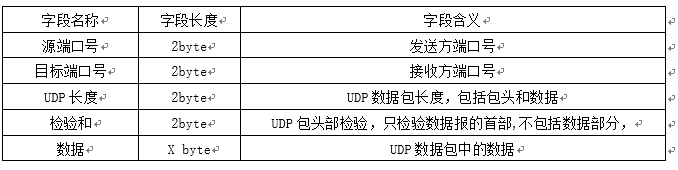

3.3.UDP数据包格式

UDP数据包以数据的形式包含在IP数据包中,其格式如图7所示,各字段含义如表4所示。

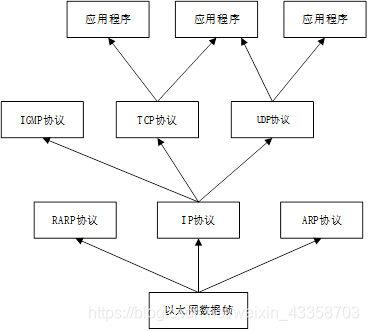

3.4 以太网协议架构

在以太网各种协议中,以太网数据帧、IP、UDP等协议之间的关系如图8所示。以太网数据帧位于最底层,第二层是IP协议、ARP协议、RARP协议等协议,第三层的TCP、UDP、IGMP等协议基于IP协议进行实现,多数网络应用程序可基于TCP或者UDP协议进实现。从上面的几种数据包介绍中,也可以推导出类似图中的关系。

3.5 UDP广播包

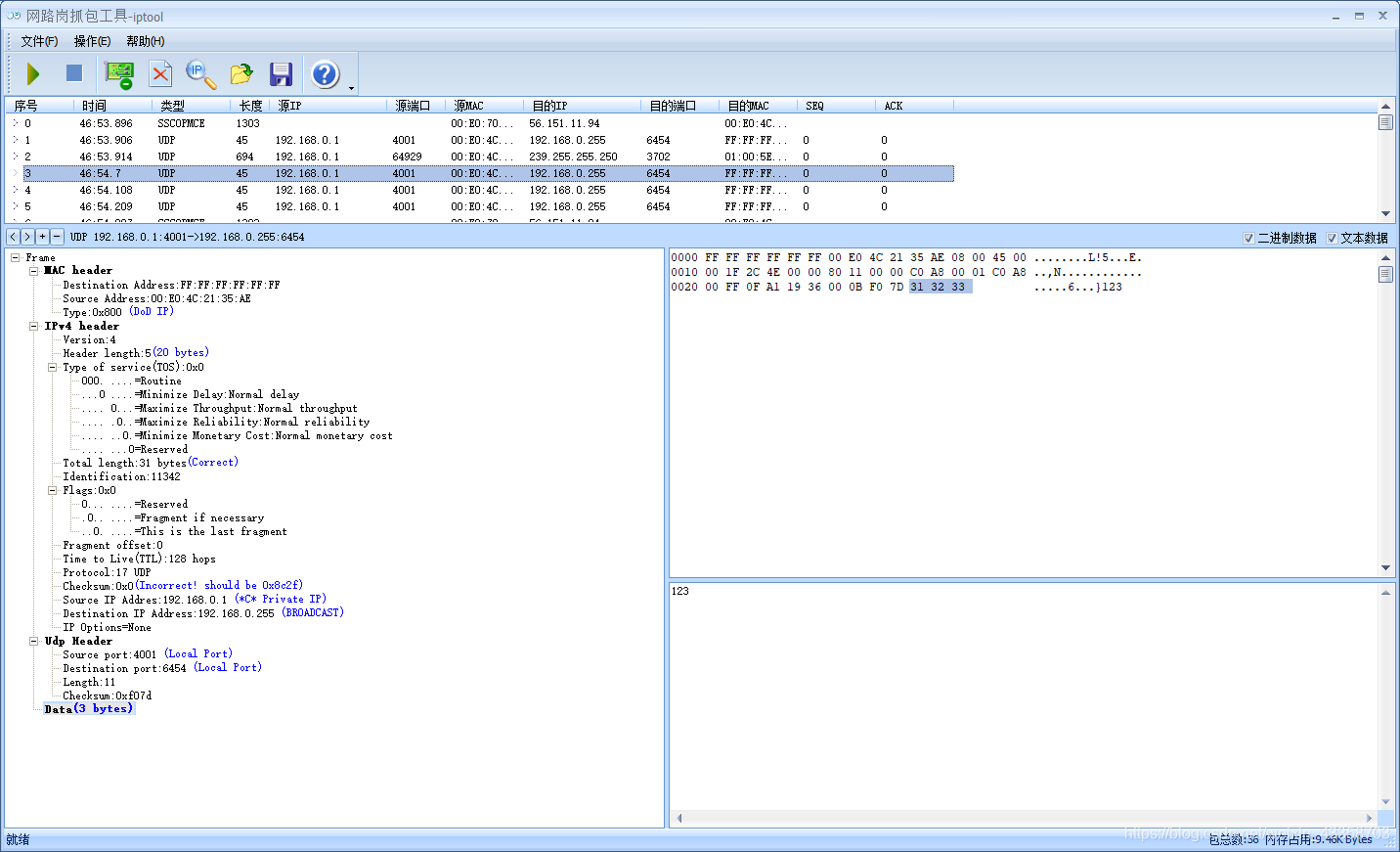

使用抓包工具捕获了一个UDP广播的数据包,如图9所示。

四.FPGA程序流程

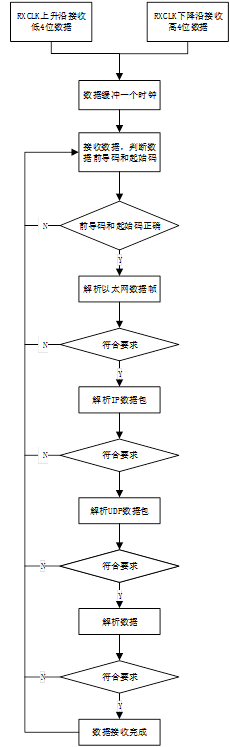

4.1 数据接收流程

数据接收时,按照RGMII数据接收时序,进行物理层数据的接收,然后按照以太网数据帧、IP数据包、UDP数据包的格式,对数据进行解析,即可实现对UDP数据的接收。数据接收流程如图10所示。

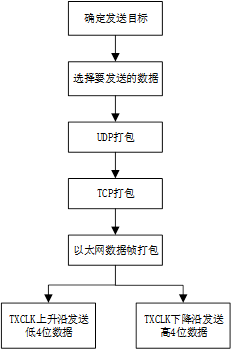

本文介绍了千兆以太网的理论与实践,重点讲解了RGMII接口的特性与优势,以及如何利用RTL8211E芯片与FPGA实现UDP数据的收发。文中详细阐述了以太网数据帧、IP与UDP数据包的格式,并提供了FPGA程序设计流程。

本文介绍了千兆以太网的理论与实践,重点讲解了RGMII接口的特性与优势,以及如何利用RTL8211E芯片与FPGA实现UDP数据的收发。文中详细阐述了以太网数据帧、IP与UDP数据包的格式,并提供了FPGA程序设计流程。

2586

2586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?