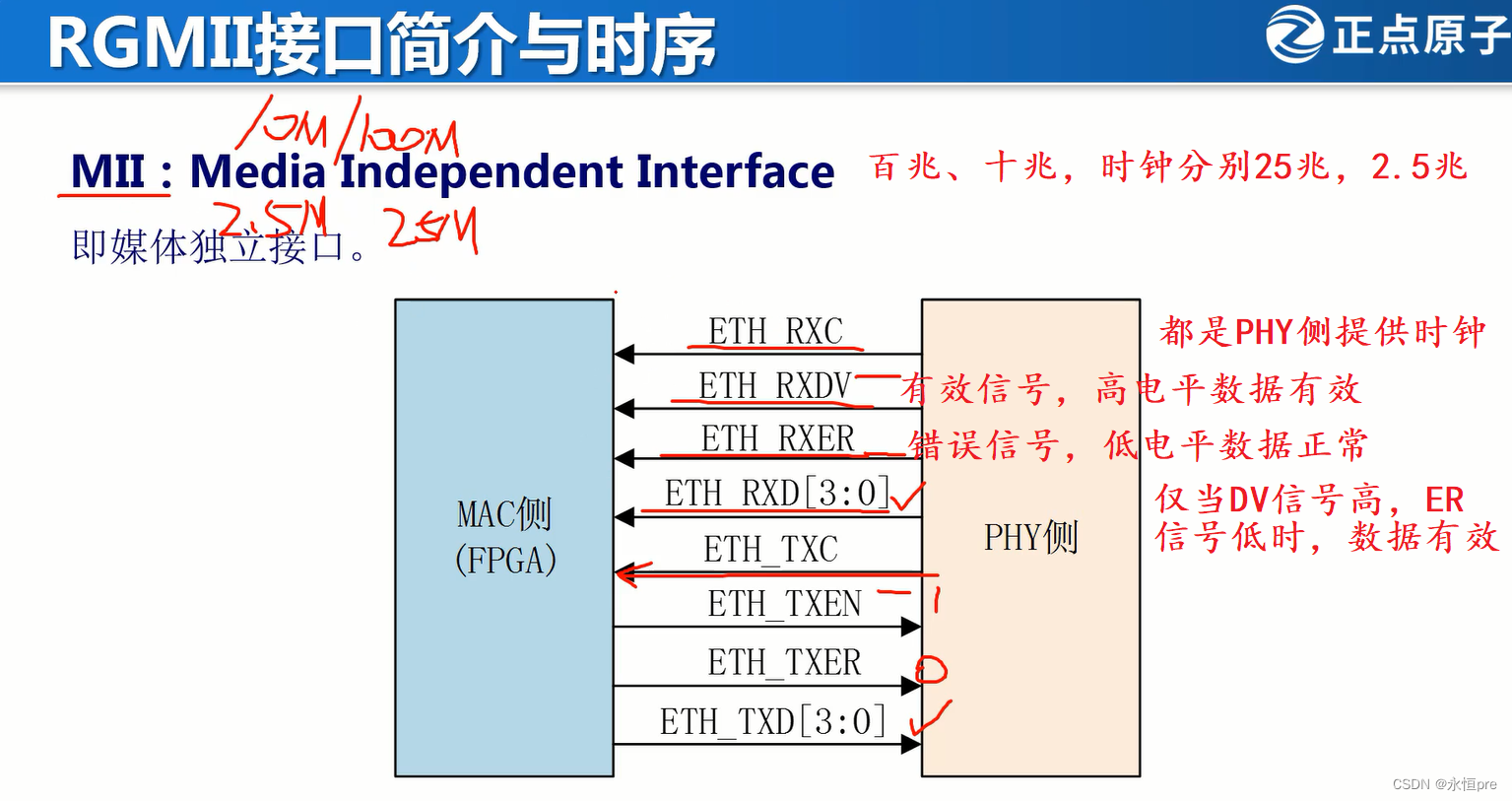

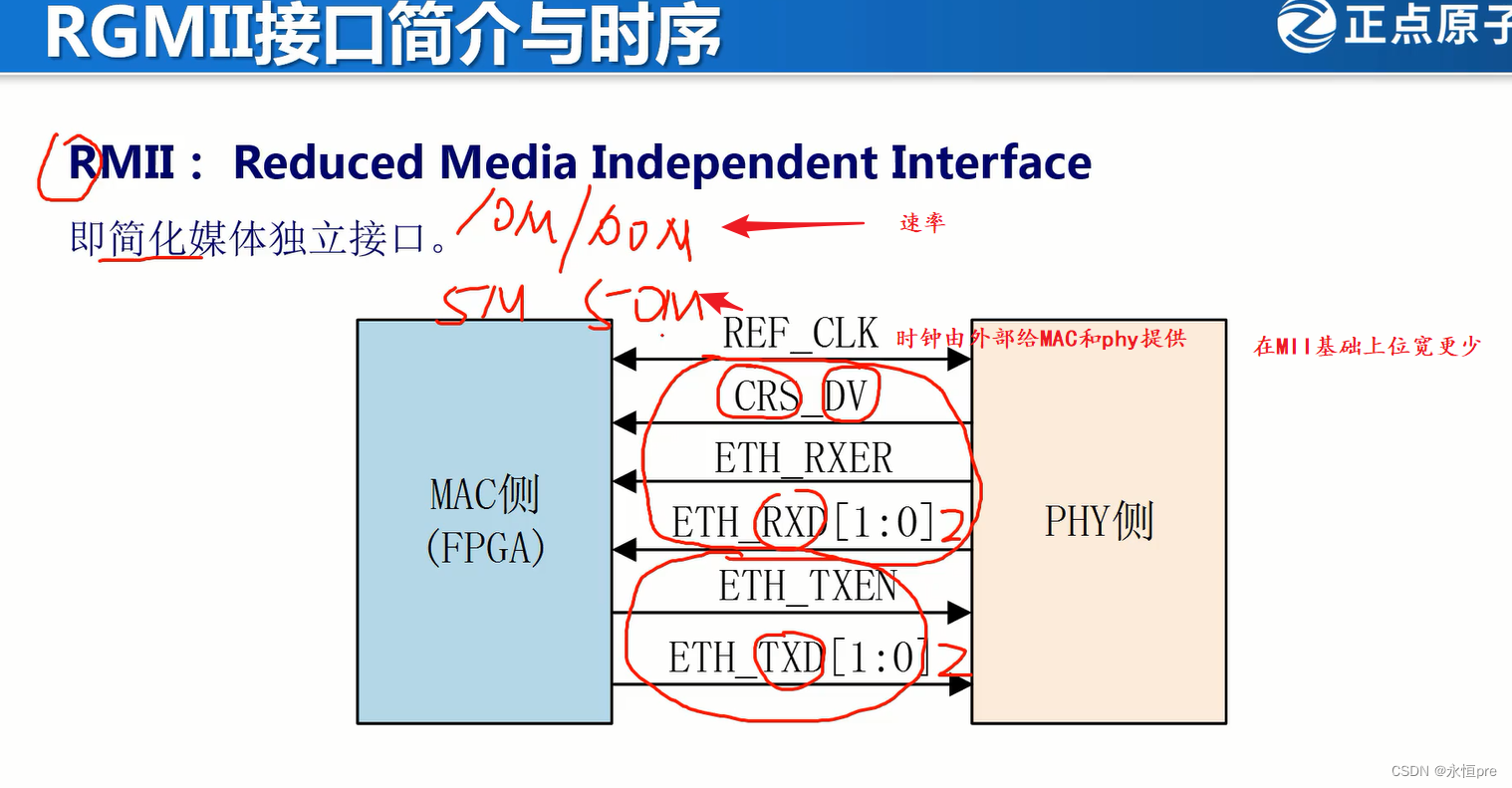

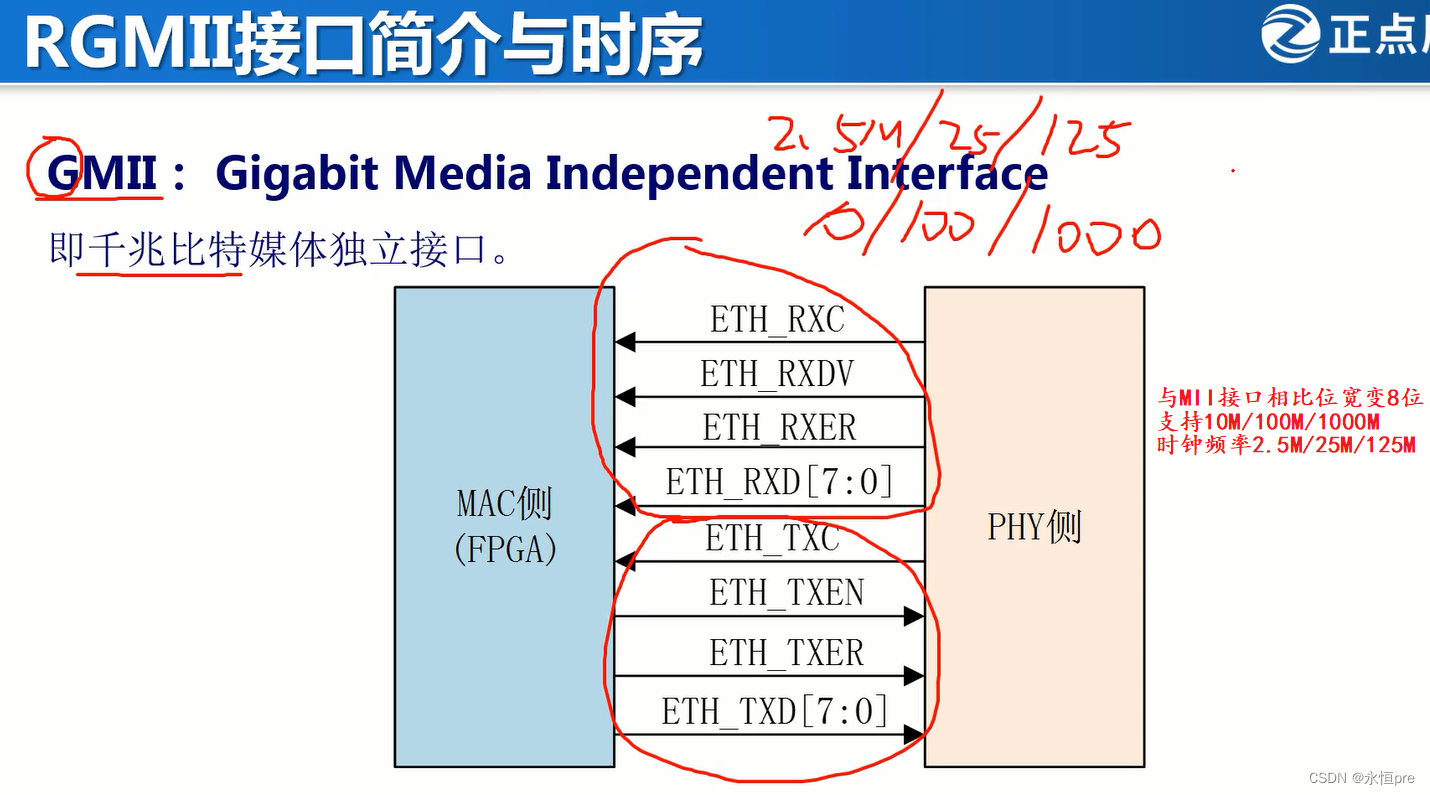

除此之外,还有MII RMII SMII GMII接口

百兆网:MII和RMII

更节省接口的串行接口:SMII

GMII接口为10M和100M时,数据位宽只用到4位,所以时钟频率为2.5M和25M

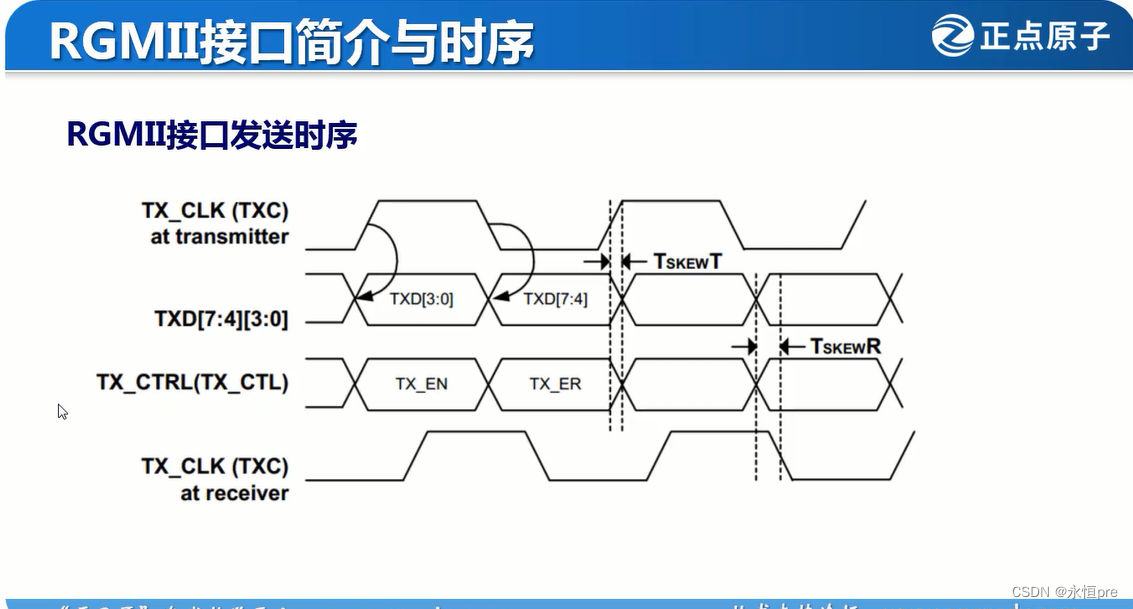

下面TXC时钟线方向反了

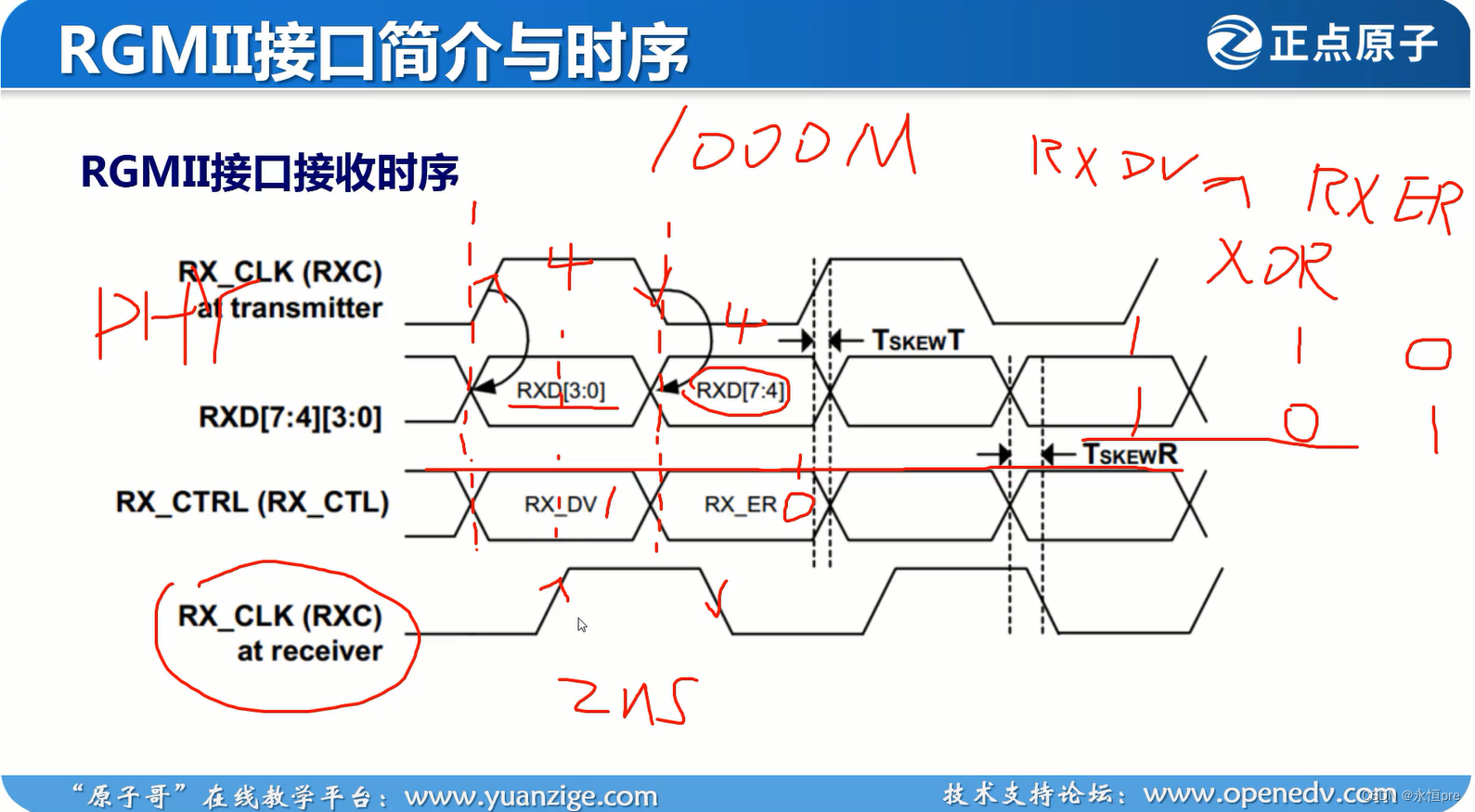

RGMII只有1000M时是上下沿均采样

上图中与GMII接口相比,RXDV和RXER信号合并为RXCTL TX同

下面,RGMII接口RXCTL和TXCTL也是上升沿和下降沿采样,上升沿采的是类似GMII的DV,下降沿采的是类似GMII的DV和ER异或值,因为GMII接口DV和ER分别为1和0时,数据正常,所以RGMII的上升沿和下降沿采的都为1时数据正常,也就是RGMII正常数据传输时,RXCTL一直为高电平正常,TXCTL同。

注意1个字节8bit,接口只有4位,先发送低位后发送高位

当1000M时,RXCLK和TXCLK周期为8ns,半个周期为4ns

上下两图中最后一个信号为接收端延时后的时钟信号,上下两图中最上面信号为发送端时钟信号

可以看出,无论是哪个方向的数据传输,发送端是时钟沿数据变化,接收端是发送端的时钟延时2ns后于数据中间进行采样,2ns刚好为半个时钟周期的一半

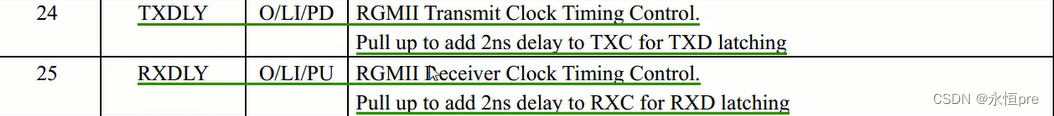

2ns时钟延时可以通过对PHY芯片进行引脚上下拉实现,对于有些的别的PHY芯片可以通过配置寄存器实现。下图为通过上下拉实现时钟2ns延时。

此外也可以通过布线故意时钟线长点实现延时,但一般不采用。一般采用等长线后通过PHY芯片配置上下拉电阻或者寄存器实现。

1461

1461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?