关于6678芯片时钟初始化可以利用gel文件来加载,也可以利用多核加载函数multicoreboot来进行初始化。

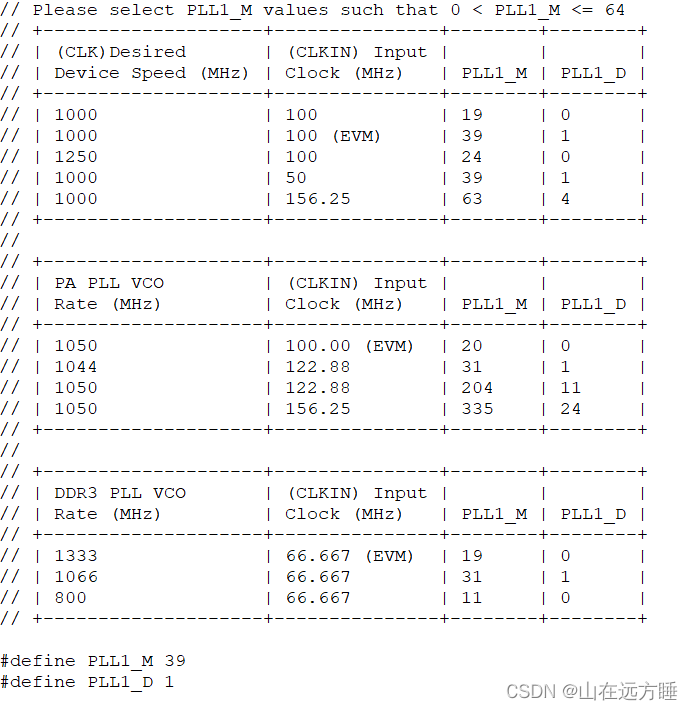

主频的配置与PLLM和PLLD有关。通过查阅手册,PLL控制器是用户软件可编程的。其中主要的概念有:分频(PLLD)、倍频(PLLM)和无效(DISABLE)。

- 分频:就是将PLLOUT的频率分别除以(1到256可编程)得到频率

- 倍频:与分频相反,是乘以可编程系数。

- 无效:就是停止时钟输出。

在C6678手册2.5.3 PLL Boot Configuration Settings一节中,Table2-13给出了部分参考PLLM、PLLD取值,如下图所示。

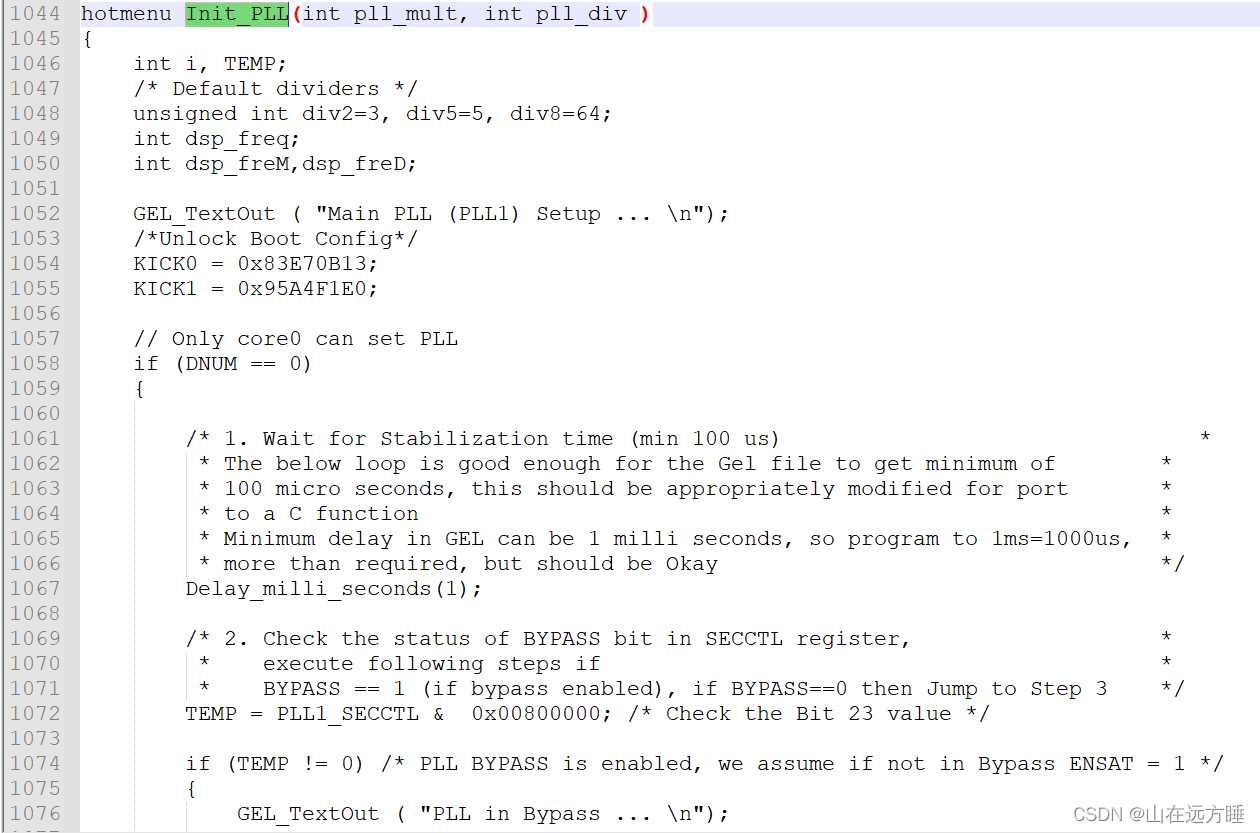

- GEL文件中配置主频的位置:

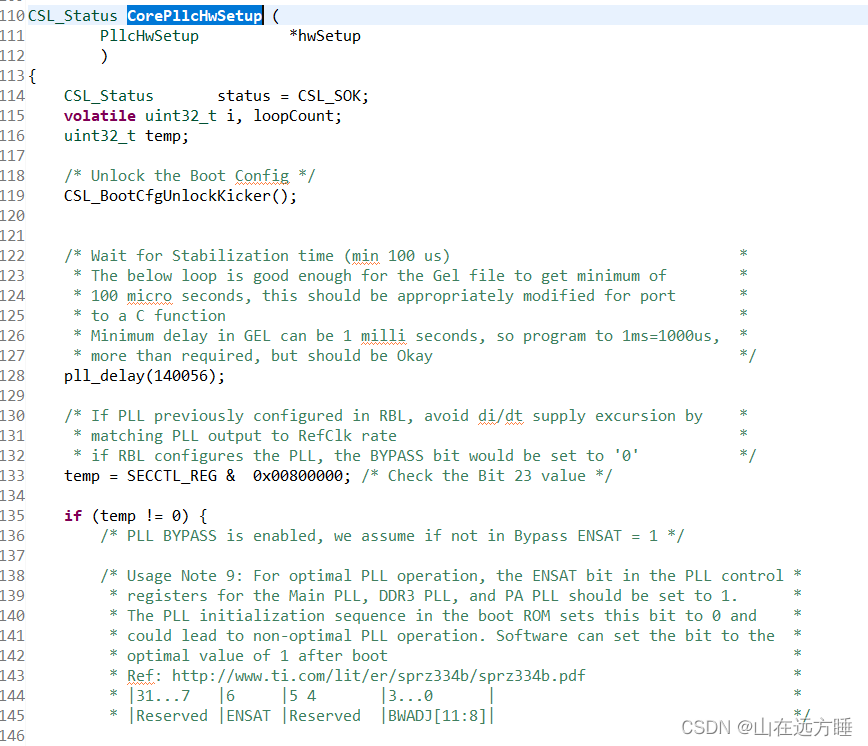

- DSP利用multicoreboot自己配置主频的位置:

MulticoreBoot-> platform_init->CorePllcHwSetup

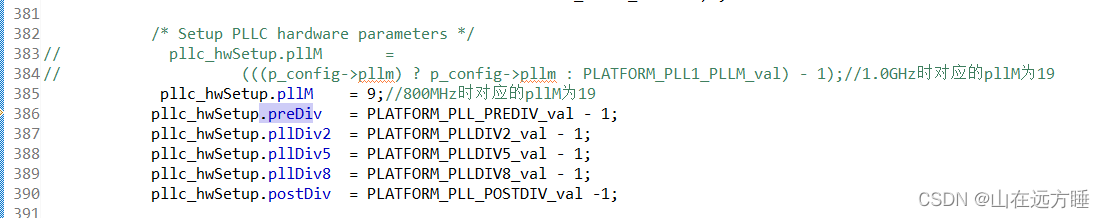

该函数中要用到的preDiv和pllM是在platform_init中配置的。

PllD=0,pllM=19时,对应1GHz主频;PllD=0,pllM=15时,对应800MHz主频;由此可以类推出PllD=0,pllM=9时,对应500MHz主频;

从而,如果想将DSP的主频降到500MHz,则应该将PllD设为0,pllM设为9。

问题二:

通过示波器对DSP输出时钟进行测量,可以发现经配置后的时钟每次上电的波形有时不同。通过看程序,里面的PLL被进行了一个十次循环配置。

尝试将loop_count循环改为loop_count<1,即做一次循环,发现每次开电后PLL配置稳定。

本文介绍了C6678芯片时钟初始化的方法,包括使用GEL文件和multicoreboot函数。主频配置涉及PLLM和PLLD的调整,如PllD=0, pllM=9对应500MHz主频。观察到时钟上电波形不一致问题,发现原因为PLL配置循环导致,减少循环次数至一次可解决此问题。

本文介绍了C6678芯片时钟初始化的方法,包括使用GEL文件和multicoreboot函数。主频配置涉及PLLM和PLLD的调整,如PllD=0, pllM=9对应500MHz主频。观察到时钟上电波形不一致问题,发现原因为PLL配置循环导致,减少循环次数至一次可解决此问题。

2958

2958

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?