一、实验目的:

设计一个有60进制和24进制计数功能,能校正时间并通过译码器及七段数码管显示的时钟电路。

功能要求:在连续脉冲的触发下,秒、分为60进制计数,时为24进制计数,并且要求有译码、显示、校时。

二、设计步骤

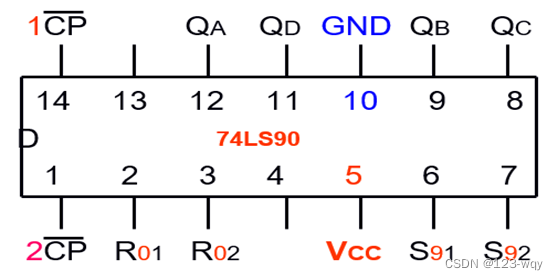

1)使用的芯片2-5-10进制计数器(74LS90),画出引脚图、功能表。

74LS90功能表

| 输入 | 输出 | 功能 | ||||||||

| 清0 | 置9 | 时钟 | QD | QC | QB | QA | ||||

| R01 | R02 | S91 | S92 | 1CP | 2CP | |||||

| 1 | 1 | 0 | X | X | X | 0 | 0 | 0 | 0 | 清0 |

| X | 0 | |||||||||

| 0 | X | 1 | 1 | X | X | 1 | 0 | 0 | 1 | 置9 |

| X | 0 | |||||||||

| 0 X X 0 | 0 X X 0 | ↓ | 1 | QA 输出 | 二进制计数 | |||||

| 1 | ↓ | QDQCQB 输出 | 五进制计数 | |||||||

| ↓ | QA | QDQCQBQA 输出8421BCD码 | 十进制计数 | |||||||

2)设计出有24进制、60进制的计数、译码、显示的电路图(24进制、60进制的电路图)

3)阐述设计电路的工作原理。(分电路是如何实现计数、进制,个位如何向十位进位的?)

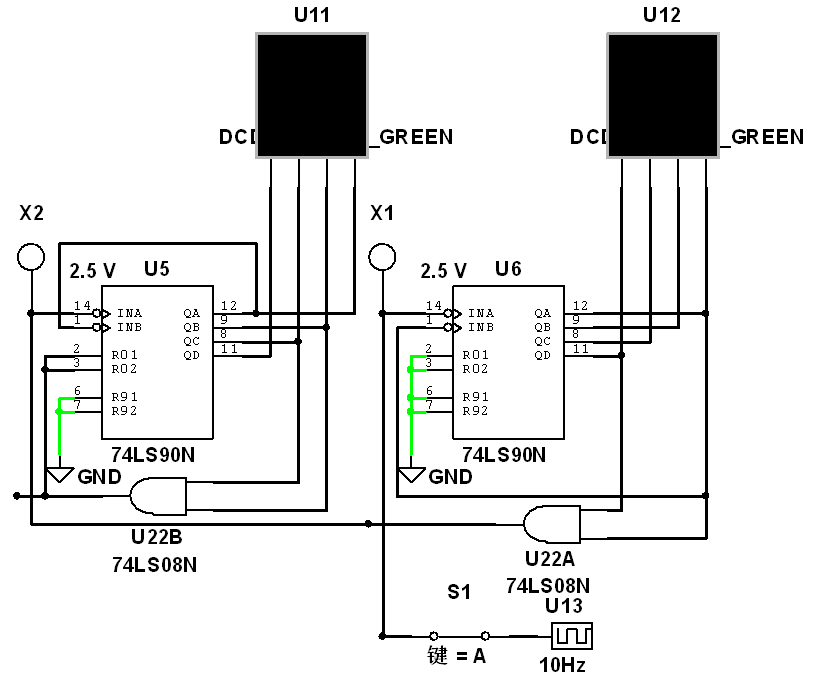

1、60进制电路的工作原理

该电路为数字钟的秒计数电路,其使用两个74LS90N计数芯片,接受时钟脉冲的输入,个位和十位的计数器都被设置为10进制计数器,个位的进位信号作为十位计数器的时钟输入信号。

当个位计数达到9时,与门输出高电平,下一周期个位将清零,与门产生一个下降沿,此时十位计数器加一,完成个位到十位的一次进位。

当十位计数达到6时,将通过门电路反馈清零十位计数器,并同时产生一个进位信号提供给下一位,以此达到60进制的计数。

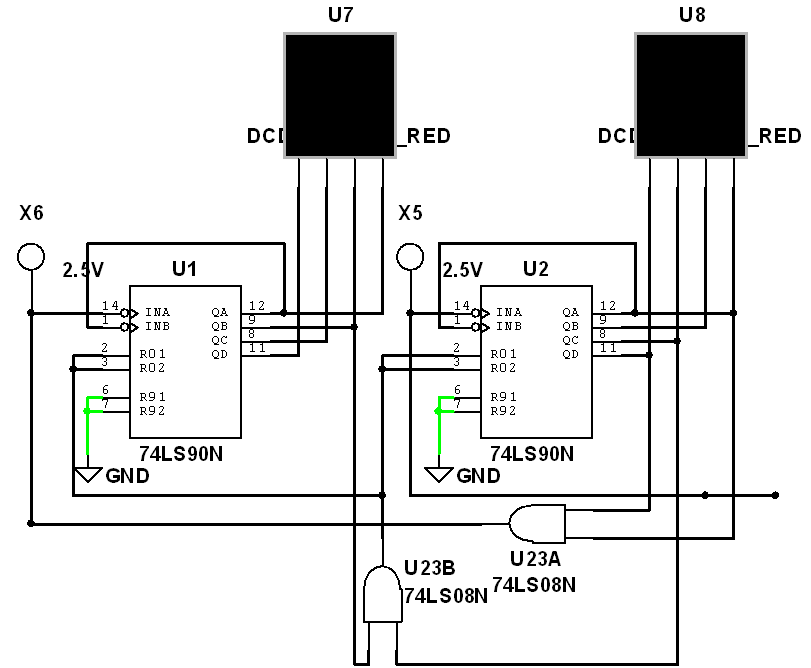

2、24进制电路的工作原理

该电路为数字钟的小时计数电路,其使用两个74LS90N计数芯片,接受分钟计数电路的进位脉冲输入,个位和十位都被设置为10进制计数器,个位的进位信号作为十位计数器的时钟输入信号。

当个位计数达到9时,与门输出高电平,下一周期个位将清零,与门产生一个下降沿,此时十位计数器加一,完成个位到十位的一次进位。

当十位计数达到2且个位计数达到3时(即23时),将通过门电路反馈同时清零个位和十位计数器,以此达到24进制计数。

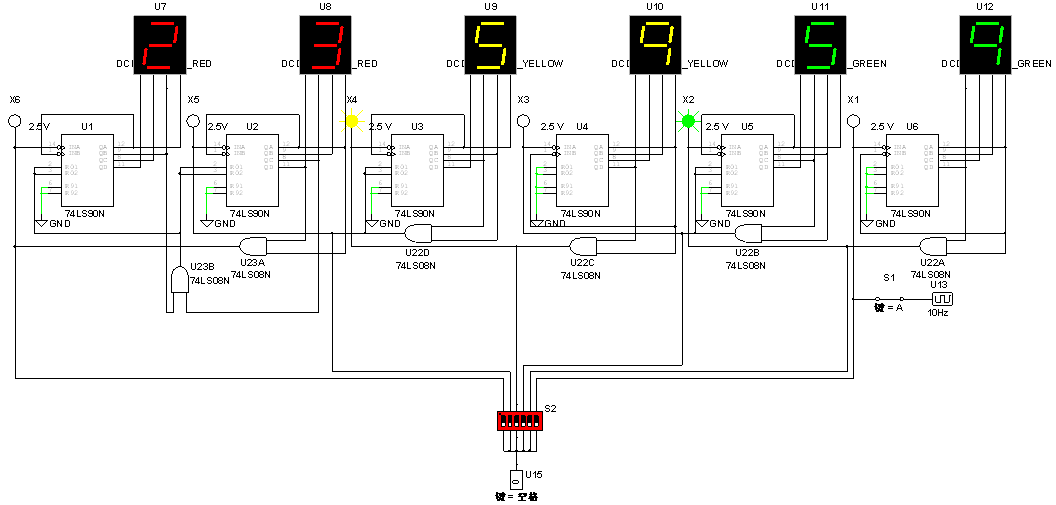

画出6位计数、译码、显示电路的总图全图。---24小时计时

1、阐述全图的工作原理。

a、秒计数电路、分计数电路均为60进制设计,十位为6进制,个位为10进制,当十位达到5时,通过门电路产生一个进位信号与清零信号,在下一个时钟的下降沿,十位清零并向后进位,完成一次进位过程。

b、电路通过6个拨码开关连接至6个计数器的时钟信号输入端,使用一个按钮手动产生时钟信号,可以实现每一位的单独控制,必要时还可以断开秒信号的时钟输入端,对电路包括秒在内的时间进行精确校时。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?