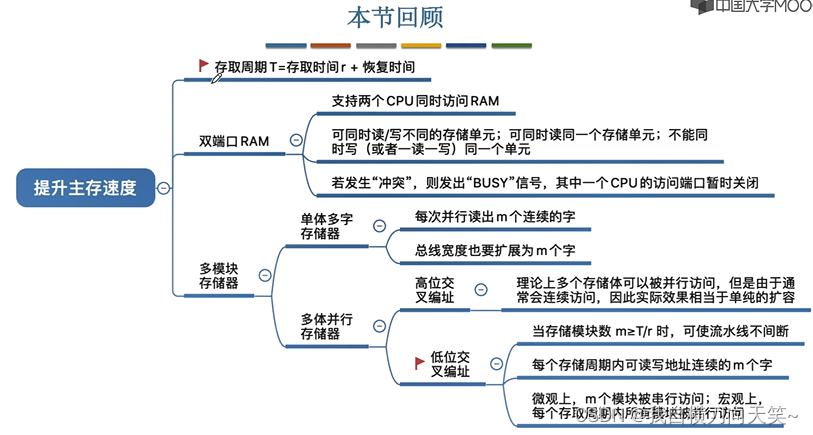

前言

在这一小节中,我们要学习的是双端口RAM 和多模块存储器这两种主存的优化技术。

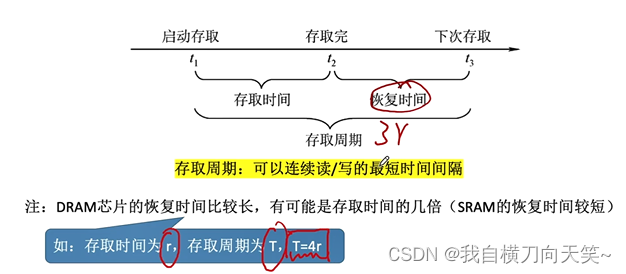

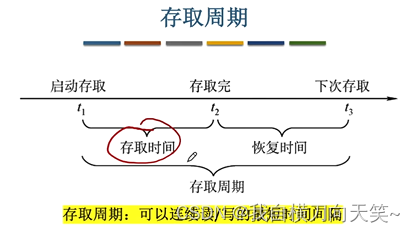

一、存取周期

我们首先要回顾一个概念,叫做存取周期。存取周期就是我们可以连续地读写所需要的最短的时间间隔。

之前我们说过,对于DRAM 芯片来说,由于DRAM芯片它采用了电容这种存储元,因此对于DRAM芯片的读操作是破坏性的读出。所以这种芯片我们进行一次读写操作之后,它所需要的恢复时间一般是比较长的,有可能恢复时间是存取时间的好几倍。

比如存取时间我们记作 r,存取周期我们记作T,有可能会达到T等于 4 倍的 r,也就是需要 3 倍的 r 这么多的时间来恢复,相比之下, SRAM 的恢复时间就会短很多。

存取时间意味着 CPU 从内存里读出一个字的数据需要的时间,实际上也只需要这么多的时间。然而,虽然存取的时间很快,但是 CPU 又必须等一段恢复时间,即恢复时间,才可以读取下一个存储字。

二、引出问题

所以这就引出了一系列的问题。我们现在的计算机,甚至是手机,动辄什么双核四核甚至是八核的CPU,这种多核的 CPU 想要访问一个内存,是不是意味着第一个 CPU 访问了一次之后,第二个 CPU 也需要等这么长的恢复时间,才可以 接着进行访问,这个问题如何解决?

第二个问题,即便是单核的CPU, CPU 的读写速度依然要比主存快很多,主存恢复的这段时间如果太长,我们应该怎么处理?有没有什么思路对这个问题进行优化。

所以这个小节我们要解决这两个问题。

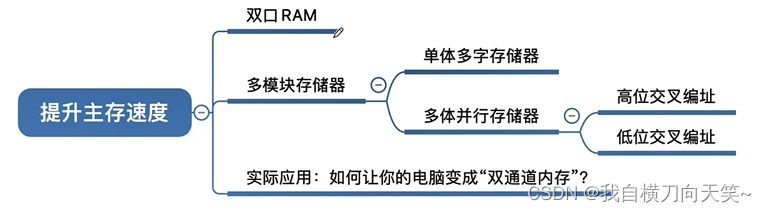

第一个问题就是多核CPU,我们可以用双端口 RAM 这种方式来解决。而第二个问题我们可以用多模块存储器这样的方式来解决。

多模块存储器又可以进一步地分为单体多字存储器、多体并行存储器,多字高位交叉编制,低位交叉编制这样的一些策略。

很多爱打游戏的男生应该听说过双通道内存这个名词。如果你把你的电脑改造成双通道内存,你的电脑性能其实是可以得到很大提升的,你打游戏可以更爽。

所以小节的知识还是可以应用到我们现实生活当中的。

三、双端口RAM

首先我们来看第一个技术叫做双端口RAM。

这个技术可以用于优化多核 CPU 来访问一根内存条的速度。比如我们的电脑是双核的CPU, 只有一根内存条,我们的内存条它采用了双端口 RAM 这种技术,这样我们的两个 CPU 的核心就可以通过它的两个端口来对内存进行并行的访问。 如果要支持双端口RAM,我们就必须拥有两组完全独立的数据线,也就是数据总线,地址总线和控制总线。所以我们的总线设计会变得更复杂。如果用大家熟悉的东西来说,就是 我们的电脑主板设计得要更复杂一些,需要有两组完全独立的各种各样的线。另外 CPU 里边的内存控制单元,还有我们内存里边的读写控制电路,也需要有更复杂的设计。

现在我们来分析一下这两个 CPU 对双端口RAM的访问有可能出现的一些情况。

第一种情况:两个 CPU 有可能通过两个端口同时对 RAM 里的不同地址单元进行存取数据。这种操作是可以支持的,只要他们想要访问的地址不发生冲突,它们俩就可以同时进行读,或者同时进行写。

第二种情况:两个 CPU 也可以通过两个端口同时对同一个地址单元进行读数据这样的操作。因为读这个操作并不会改变存储单元里边存储的数据,所以两个同时读是可以被支持的。

第三种情况:如果两个 CPU 通过两个端口,同一时刻对同一个地址进行写入数据,此时就会发生写入的错误**。左边 CPU 先往存储单元里写了数据a,右边 CPU 同时往里边写了数据b。它们俩写的数据有可能**相互覆盖。所以,同时对同一个地址进行写操作应该是被禁止的,这是一个非法的操作。

第四种情况:如果同时对同一个地址单元,其中一个进行写数据,另一个进行读数据,此时读出数据的 CPU 就有可能会出现读出错误。比如存储单元里本来存的是a,右边CPU本来想把 a 读出去,但是由于左边CPU正在同时往里边写 b 数据,这就会导致右边 CPU有可能实际取得的是b。因此对同一个地址单元一读一写,**这种操作也是应该被禁止的。

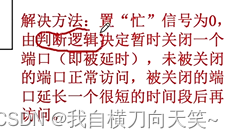

所以当发生 3 和 4 这两种情况的时候, RAM 里的控制电路应该向两个 CPU 发送一个忙的信号,同时会有一些逻辑电路来决定暂时关闭其中某一个端口。比如先把右边端口给关闭,让 CPU2 等一下,等左边 CPU完成操作之后,右边CPU 再继续访问。 这就是双端口 RAM 技术。

学过操作系统的同学可以把部分的内容和我们的读者写者问题进行一个对比。可以同时读,但是不能同时写。这个其实和读者写者问题一模一样。 好,有了双端口 RAM 技术,就可以优化多核 CPU 访问一根内存条的速度。

四、多体并行存储器

接下来我们进入第二个话题。

之前我们说过,即便是对于一个单核的CPU,CPU的读写速度也比内存要快得多。而内存每一次读写之后又需要一段的恢复时间,当CPU 想要连续读取一些数据的时候,就必须等待内存的恢复时间。

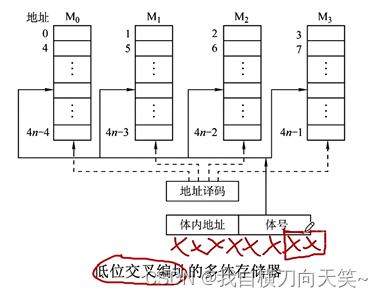

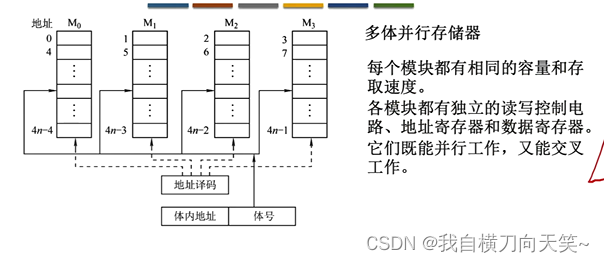

这个问题的解决就可以使用到多体并行存储器,如下:

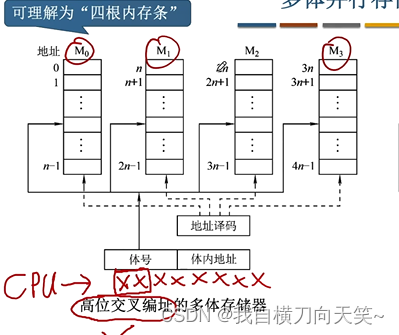

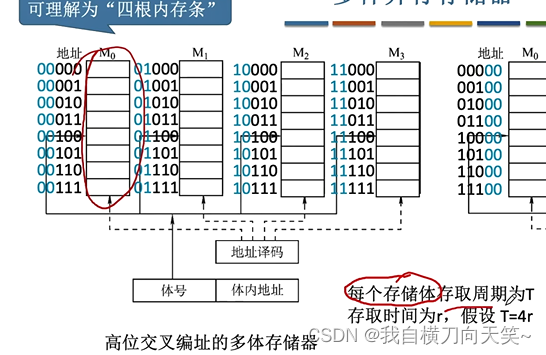

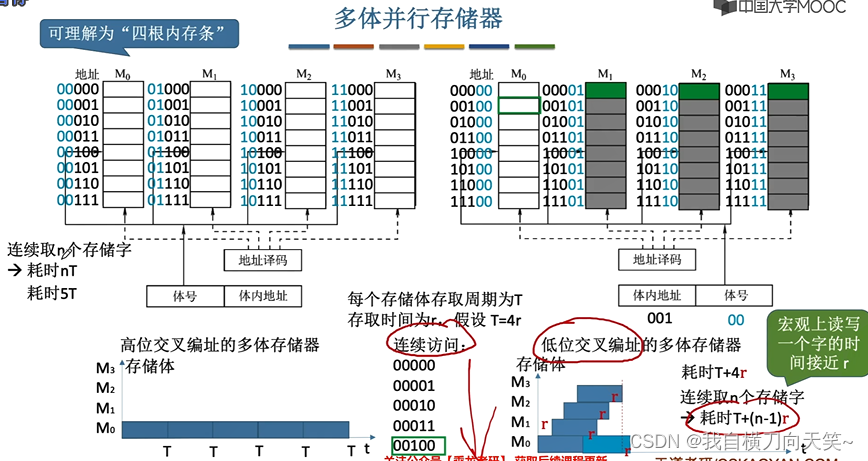

大家可以把这理解成是你在你的电脑上插了 4 根内存条,并且每个内存条它的大小都是一致的。

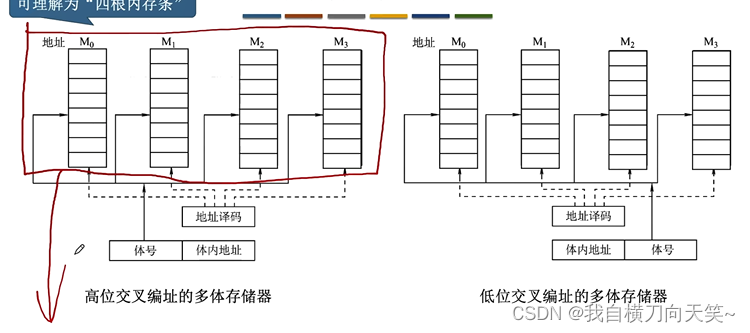

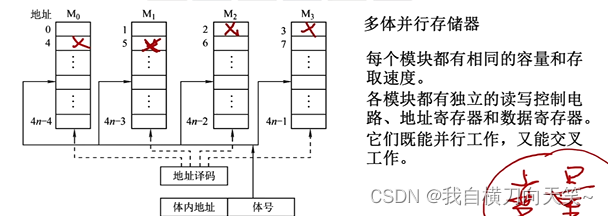

我们可以有这样的两种编址的方案,第一种叫做高位交叉编址,第二种叫做低位交叉编址。

什么意思呢?我们的 CPU 在对内存进行访问的时候,一定需要提供一个内存的地址(用来表示数据存储到哪)?内存的地址肯定就是几个比特位的信息。

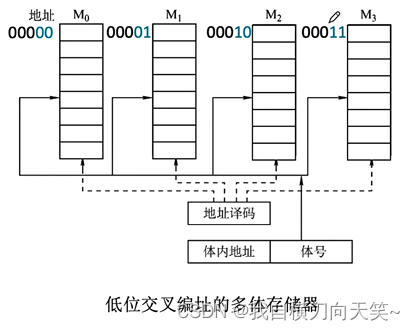

(1)高位交叉编址方式

采用高位交叉编址的意思就是我们会采用内存地址的更高的几个比特位,来区分我们想要访问的是哪一个存储体。

比如在这个图里边,我们总共有 4 个存储体,有 4 个内存条,我们就可以用最高的两个比特位来分别区分我们要访问的是哪个内存条。因为2比特总共会有四种状态,刚好可以对应上 M0 到M3。

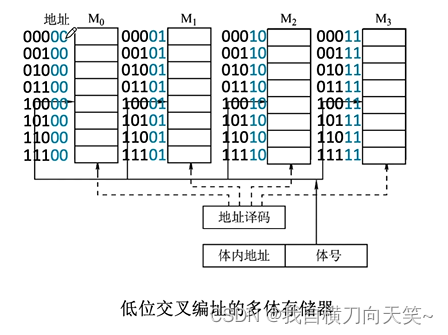

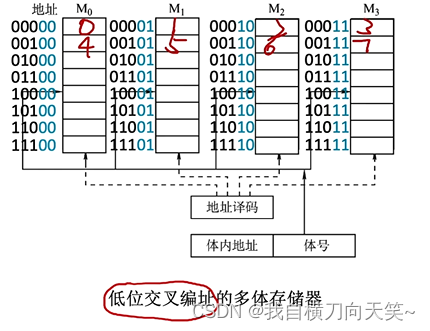

(2)低位交叉编址方式

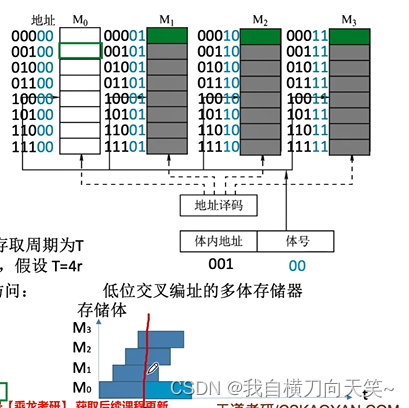

类似的,如果采用低位交叉编址的意思就是,对于我们给定的内存地址来说,我们会采用更低的两个比特位来区分 M0 到M3。如下图:

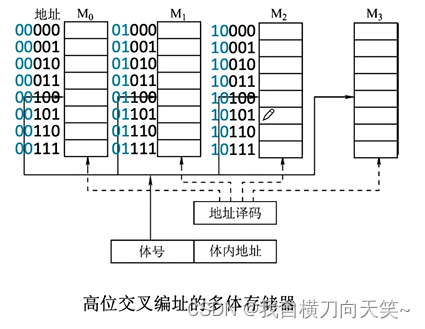

(3)编址

我们现在假设每个存储体总共只有 8 个存储单元,由这 4 个存储体构成的一整个主存,它的地址空间大小应该是 4 个存储体,每一个存储体有 8 个存储单元,也就是4*8=32等于 2 的 5 次方。所以我们可以用 5 个比特来作为主存的地址。

如果采用高位交叉编址,就意味着第一个存储体,它的第一个存储单元,给它的地址应该是00,称为体号,后面的三位称为体内地址。高位的两个00表示这是 M0 存储体,后面的三个 0 表示的是在存储体内部的第几个单元。 所以,第一个存储单元应该是000,下一个存储单元应该是001,再往后都是类似的。

然后是第二个存储体,它开头的两个体号应该是01,而后三位的体内地址同样应该是从 3 个零一直到 3 个1。接下来M2、 M3 这两个存储体,它们的编址也是类似的,只不过是最高两位的体号不一样。如下:

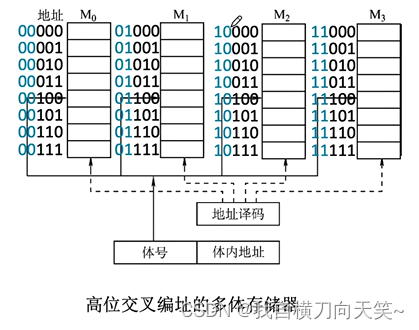

接下来看低位交叉编址。 由于这个位置应该是 M0 的 0 号单元,所以体号应该是0,体内地址也是0。(和刚才的高位交叉编址反过来了,体号是后面两位,前面三位是体内地址)如下:

对于同一行的存储单元来说,体内地址都是一样的,只不过体号会不一样。 后续的这些地址也都是类似的。如下:

(4)特性

现在我们尝试着把刚才这些地址信息翻译为十进制。 对于高位交叉编址来说,地址翻译成十进制应该是0123竖着的,以此类推。

而对于低位交叉编址,我们的地址编号应该是这样的01234567横着编的。如下:

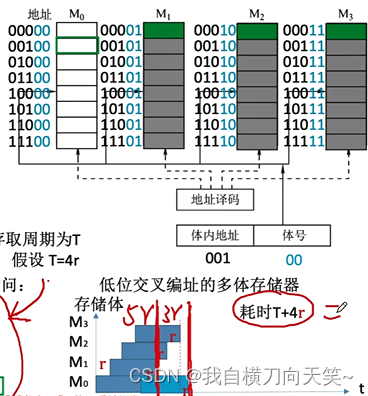

这两种特性会导致什么区别? 我们来看这样的一个例子。 现在我们假设每个存储体,也就是这样的一坨。假设它的存储周期为T,存取时间为r,并且设T=4r。 也就是 CPU 从一个存储体里边取走一个字的数据,总共需要 r 这么长的时间。但是 CPU 想要再次访问存储体,就需要再等 3r 这么多的时间。这个3r就是我们之前提到的恢复时间。

<1> 高位交叉编址

对于高位交叉编址,如果我们要连续访问这样的一些地址。

第一个地址 5 个0,根据体号和体内地址可以知道,它应该是对应 M0 的存储单元。

我们画一个甘特图, CPU 对 M0 存储体进行了一次读操作,每一次读它的存取周期是T。实际上 CPU 只花了 r 这么长的时间就完成了读这个操作,但是后面还有 3r 这么多的时间,必须等待存储体恢复之后才可以继续访问接下来的地址,因为接下来的这个地址同样是属于 M0 存储体。所以必须等T这么长的时间才可以访问1 号地址。

接下来再过一个周期再访问 2 号存储单元,然后是3 号、 4 号。 如下:

总之,由于我们连续访问的这些地址都属于 M0 存储体,所以每一次访问完之后都必须等待它恢复。也就是总共过了T这么长的时间之后,才可以进行下一次的读写。 整个过程我们读了 5 个存储字,耗时是5T。这是高位交叉编制。

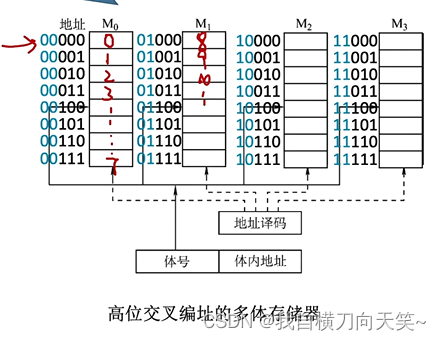

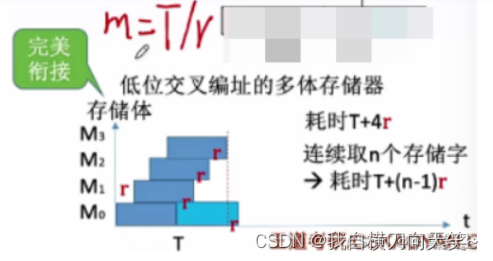

<2> 低位交叉编址

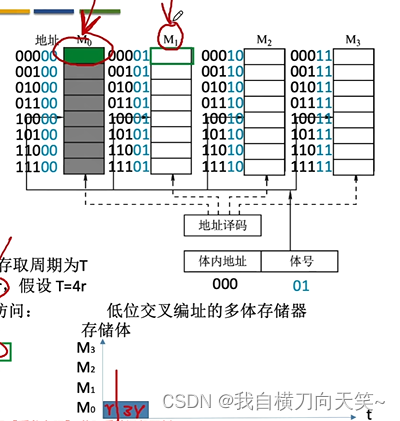

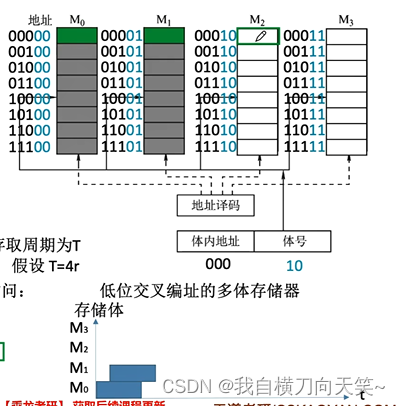

接下来再来看低位交叉编址。 根据这个地址的末两位,我们可以知道这个地址它应该是从属于 M0 存储体。 所以 CPU 会从 M0 这儿读出一个字。如下:

刚才我们说过,其实 CPU 从存储器里边读或者写一个字,实际只需要 r 这么长的时间。因此过了 r 这么长的时间之后,相当于对 M0 的存储单元的读取工作就已经完成了。 后面的 3r 这么长的时间, CPU 不用管它,只需要让存储体它自己恢复就可以。所以过了 r 这么长的时间之后,由于我们第二个要访问的存储单元,它所属的存储体此时是已经准备好读写的M1,因此 CPU 可以直接从 M1 这儿读取数据。

之后就是类似的,再往后要访问的存储单元 2 号单元,它属于M2,而 M2 此时已经准备好被读或者被写了,所以读M1操作经过 r 这么长的时间之后,CPU就可以紧接着读 M2 单元。

再往后一个地址,它的体号是11,就是M3。同样的,此时 M3 是已经准备好读写的。所以再经过r, CPU又可以再紧接着读M3。

接下来读取 M3 是不是也需要花 r 这么长的时间?所以读完 M3 之后,其实从刚开始算起,我们总共已经过了 4r 这么长的时间了,也就刚好过了一个存取周期T。

因此 M3 这个地址读取完了之后,是不是 M0 存储体又可以准备好被读取了? 而刚好我们接下来要读取的地址,又回到了M0,因此到T这个时刻,CPU又可以紧接着从 M0 读出下一个字的数据。如下:

所以对于这个例子,我们读出地址连续的 4 个存储单元总共的时间开销应该是T+4r,也就刚好等于 2T 。

如果要说 CPU 取得这五个字所需要的时间,其实在 5r 这个时刻就已经完成了。 只不过这地方我们计算的总耗时其实是考虑上了最后的这三个 r 的恢复时间。

因此访问这 5 个地址总体的耗时,我们把记作2T。 如果我们把刚才计算的结论进行一个推广,不难得出这样的结论。当我们连续存取 n 个存储字的时候,采用低位交叉编址,总耗时应该是**T+(n-1)r。**因为我们对各个存储字的读取刚好是可以无缝衔接的,所以读取 n 个存储字总共需要花 n 倍的 r 这么长的时间。 而最后一个存储字读取完了之后,还需要给它留 3r 这么多的时间来进行恢复。所以整体来看的耗时应该是T+(n-1)r(T=4r)。 这是有可能遇到的一类考题,考察你对微观层面的时间开销的计算。

宏观上看,我们使用这种策略读写一个字的平均时间只需要 r 这么多。所谓的宏观就是指如果你连续读取的字数 n, n 趋近于无穷大的时候,每个字的平均存取时间是非常接近 r 的。

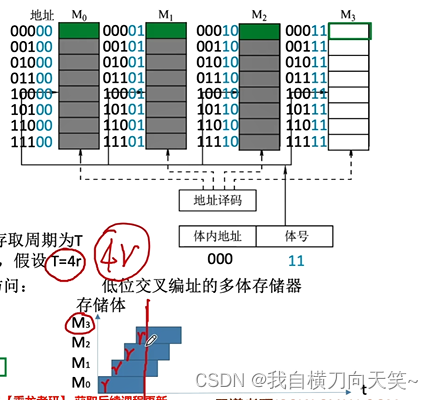

所以在访问一系列地址连续的存储单元的时候,这种低位交叉编址的方案,它的效率要比这种高位交叉编址要高得多,性能几乎提升了 4 倍。 这就是多体并行存储器。

整体的运行逻辑对比如下:

(5)思考

现在我们思考这样的一个问题,为什么我们探讨的是连续访问的情况。 原因是这样的,在我们实际应用当中,有很多数据其实就是存放在地址连续的空间,比如数组的存储放在地址连续的一些内存单元里边。 另外,我们平时写的程序代码或者程序的指令,它也是连续的存放在主存当中。除非遇到if、 else 之类的需要发生跳转的地方,否则程序指令的执行肯定是顺着地址一条一条往下读的。 所以这个地方我们着重探讨连续访问的情况,是很有现实意义的。

(6)体的问题

接下来我们来思考这样的一个问题。 既然这种低位交叉编制的方案可以让我们的存取效率变得更高,那我们应该取多少个体才合适呢? 刚才这个例子当中,我们实现了存取的流水线。这个地方流水线的概念其实和工厂的流水线是很类似的。 比如一个工厂,它的一条生产线,有 4 个工人。这4个工人,他们加工好的零件会放到传送带里,在传送带的另一端,会有一个机器人来处理这四个工人给的这些零件。

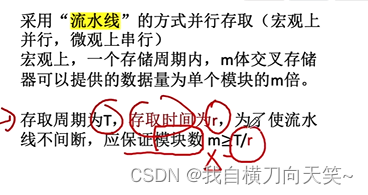

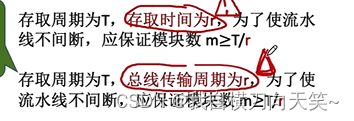

这是工厂的流水线,是不是和我们这个地方一样,四个存储体他们提供数据的速度是比较慢的,这四个存储体就类似于这四个工人,而机器人就相当于我们电脑里的CPU,他可以快速地处理这些工人给他提供的零件。 正是因为这两种场景的相似性,所以我们才把这种存取方式称为流水线式的存取。 为了保证我们的流水线工作不间断,当存储周期为T,存取时间为 r 的时候,我们应该保证存储模块的数量 m 是大于等于 T 除以 r 的。

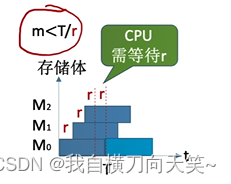

像刚才这个例子,我们刚好就取了 m 等于 T 除以r。 之前我们说过,这例子里面 T 等于4r。接下来分析一下为什么要有这样的规定。 假设我们此时取的存储体的数量m小于 T 除以r,还是以刚才的 T 等于4r作为一个前提条件,我们取 m 等于3,只有三个存储体。 现在经过三个 r 之后, CPU 分别从M0、M1、 M2 里边取走了三个字。再往后, CPU 又应该访问 M0 存储体,然而在 3r 这个时刻可以看到 M0 还没有恢复,所以 CPU 必须等待 r 这么长的时间才可以进行下一次的存取。所以当 m 小于 T 除以 r 的时候,我们不能完全发挥流水线的作用。

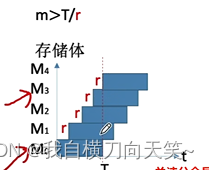

再来看,如果 m 大于 T 除以r。 比如 m 取5,当 CPU 从 M 0 到 M3 分别取走一个字的数据之后,此时刚好过了 4r 这么多的时间,也就是在这个时刻,其实 M0 存储体它已经准备好被下一次访问了。 然而由于我们此时有 5 个存储体,所以接下来 CPU 访问的应该是M4。对 M4 的访问也需要 r 这么长的时间。访问完 M4 之后, CPU 才会再回头访问M0。所以这就导致 M0 存储体它中间其实闲置了 r 这么长的时间,它本来可以继续干活的,但是这偷懒了一段时间。这就意味着当 m 大于 T 除以 r 的时候,我们劳动力是过剩的。这种方案会导致各个存储体没办法发挥到他们各自的极限。

我们知道每增加一个存储体要多花一些钱对吧?所以最好的方案还是之前我们提出的,

刚好让 m 等于T除以 r 这种方案

这种方案可以让我们存取流水线的效率达到一个顶峰,同时存储体的数量最少,也就成本最低。 这也是一个考点,我们根据存取周期和存取时间来判断我们应该取多少个模块。 还有的题目会这样描述,告诉你存取周期为T,总线传输周期为r。这种描述的计算方法也是一样的。 之前我们说的存取时间r,指的是存储体的一个性能的瓶颈,存取一次至少也需要 r 这么长的时间。 而总线的传输周期为r这种说法,指的是我们通过数据总线把一个数据传给CPU,至少需要 r 这么长的时间。所以虽然这两种表述方式它背后的含义是不一样的。然而无论是哪种描述方式,都意味着我们的 CPU 存取一次时间不可能低于r。

因此,无论题目给的是哪种条件,我们都按同样的算法来处理就可以。

另外还需要补充一点,如果给你一个指定的地址x,你如何确定它属于第几个存储体?

首先,我们假设总共有 m 个存储体。

第一种方法就是根据末尾的体号来判断它属于第几个存储体,直接用二进制来判断。

第二种方法就是你可以用它给的十进制地址 x 来对 m 进行一个取余,用这样的方式也可以确定 x 这个地址它应该属于哪个存储体。

五、单体多字存储器

目前为止,我们介绍了多体并行存储器。这种存储方案的特点就是每个存储模块都有相同的容量和存取的速度,并且各个模块都有独立的读写,控制电路、地址寄存器还有数据寄存器。它们既能并行的工作,也可以交叉地工作。

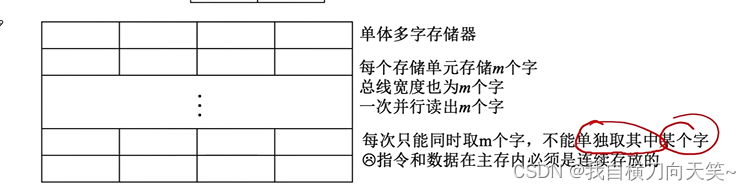

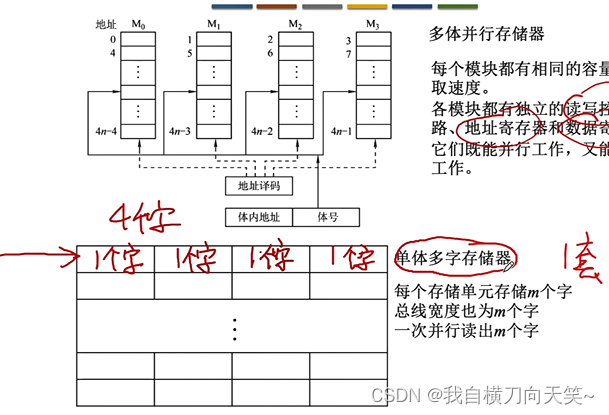

注意这儿想强调的点是,每一个体,每一个模块,它们之间是相互独立的。与这种方案相对应的另一种方案叫做单体多字存储器。

多体并行存储器这种实现方式可以让每一个存储体独立的工作, CPU 可以自由地选择每一次要从哪一个存储体读出哪一个字,它们之间都是相互独立的。 而采用第二种方案,相当于把这几个存储体进行了一个合并。整个存储器我们只有一套读写电路,还有地址寄存器,数据寄存器。

有点类似于我们之前学习的位扩展,本来每一次我们只能读写一个存储字,但是经过这样的合体之后,我们每一次读取的一整行也就是四个字(m个字)。

为了配合这种单体多字存储器,我们也需要把数据总线的宽度把它改为 m 个字,每一次可以并行的读出 m 个字。 显然,这种单体多字的多模块存储器,它的灵活性要比多体并行的存储器要更差一些。 我们并不能单独的选择要读取其中的某个字,只能一次读一整行,也就直接读 4 个字的内容。所以,如果我们要读取的一系列指令或者数据,它刚好在主存当中连续的占了一整行,这种情况是比较理想的。 但是假如现在我们要读取一个总大小为四个字的变量,这个变量占的是2、3、4、5这几个存储单元,采用第二种单体多字方式,是不是意味着我们要先把第一行给读入,然后再读入第二行。我们就会读入一些无用的、无意义的信息。

而如果采用第一种方式,它的灵活性就会高一些。 CPU 只需要精准地命中这 4 个存储单元就可以,不会读入多余的冗余信息。

所以第二种方案的灵活性要差一些。 不过如果要从整体的读取速度的提升来看,其实第一种和第二种方案都差不多,当 T 等于 4r 的时候,第一种方案它的读取时间,每读写一个字的时间可以接近于r。 第二种方案也是一样的,每一个存取周期T,我们可以直接读入 4 个字的内容,因此平均来看,每读入一个字所需要的时间,也就是T除以4,平均下来每读一个字只需要 r 这么长的时间,和第一种方案是一样的。 所以无论是哪种方案,都可以很大程度上提升主存的读写速度。

六、总结

(1)回顾

这个小结当中,我们主要介绍的是几种提升主存速度的方法。 首先要注意的是存取周期还有存取时间这两个很类似,但是又完全不一样的概念。

我们学习了双端口 RAM 这种技术,这个技术可以在多个 CPU 同时访问一个 RAM 的情况下,提升 RAM 的读写速度。需要特别注意是否可以同时读同时写的问题。

这小节的后半部分,我们又介绍了多模块存储器。在多体并行存储器当中,

如果我们采用高位交叉编址,对于访问连续的地址空间这样的一个使用场景,其实性能的提升并不明显。所以高位交叉编址这种方案,实际效果就相当于单纯的给存储器进行了一个扩容。

而如果采用低位交叉编址,我们就可以实现存取的一个流水线。这种方案是我们的高频考点,曾经在我们 408 真题里边出现过多次。

好的,这就是小结理论部分的内容,接下来我们尝试着把理论用到我们现实生活当中。

(2)Tips

咱都是学计算机的。经常会有人问诶,同学,你学计算机的,你会修电脑吗?这个时候我们好像只能绝望地摇头。但是学了小结的内容之后,以后,至少内存部分的知识大家可以有一点底气。

不知道大家有没有听说过双通道内存这样的说法,喜欢打游戏的男生应该都听过。如果你让你的电脑变成双通道内存,那它的整体性能可以提升很多。 事实上,所谓的双通道内存就是低位交叉的二体存储器。

你给自己的电脑插了两根内存条之后,你的 CPU 给这两个内存条的编址是采用了低位交叉编址的方案。也就是,虽然你的内存它的读写速度跟不上CPU,然而,当你插入了两个内存之后,你的 CPU 可以交替着访问这两个内存,这样可以让你的内存整体的吞吐量几乎翻倍。

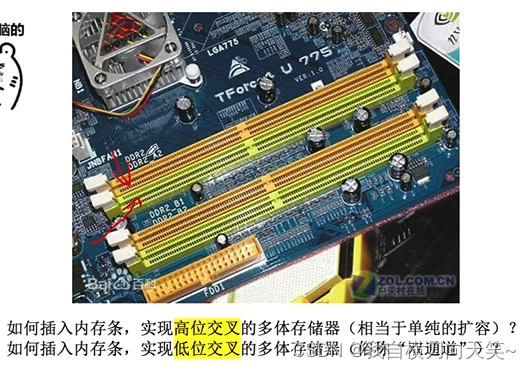

当然,这所谓的翻倍,指的是连续访问的情况。经过之前的讲解,应该不难理解。 以后大家在自己组装电脑,或者你想给自己的电脑加装一根内存条的时候,可以拆开自己的主板,看一下很多主板,他给的内存条的卡槽颜色是不一样的。 这是我在网上随便找的一个图片主板,它所支持的内存是DDR2,已经过时了。但是现在的这些主板其实也都差不多。

以后如果你有两个内存条,这两个内存条应该插到颜色相同的两个卡槽里边,只有插到颜色相同的两个卡槽里边,它才是低位交叉编址。而如果你其中一条插到了黄色,另一条插到了绿色,如果采用这种插法,相当于给这两个内存条进行了一个高位交叉编址。也就是你只是单纯的扩充了内存的容量,并没有提升它的访存速度。

所以以后给大家的建议。当你买内存条的时候,经费有限的情况下,可以选择相同主频相同容量的两根内存条来组成双通道。当然也可以选择直接买一根 16GB 的内存,直接插到你的主板上。但是更好的方式其实是你选择两根 8GB 的内存,分别把它插到两个黄色的卡槽上,这样你的内存性能是更高的。 所以这也是为什么大家去搜内存条的时候,你会发现很多商家他卖内存条,整个商品页面它是 16G 乘2,是这么来卖的。因为两根一起卖,就意味着你可以组成一个双通道。

不知道刚才大家有没有思考过,为什么推荐买内存条的时候要相同主频,相同容量?

<1> 首先来解决第一个问题,为什么要使用相同主频?

你看这个内存条,它的主频就是 3200 ,单位是兆赫兹(MHZ),这是它的内存主频。这个主频其实反映的是它的读写周期到底是多快,主频越高,它的读写周期 T 也就越短,相应的读写时间 r 也会越短。

如果你买的是两根主频不一样的内存条,主频更高的内存条就会进行一个降频的处理,也发挥不出它所有的功效。 因为经过之前的分析,我们知道,多体存储器,它的各个体CPU在处理的时候,只有 T 和 r 这些都相等,处理起来才会比较方便。所以这是为什么要选相同主频的原因。 当然,你在加内存的时候,买一个主频更高的内存,和你的老内存配合也可以,只不过高出去那部分主频其实是被浪费的。性能你利用的不充分,也就是你有一部分钱没必要花。因为一般来说,主频越低的内存,它的价格也会更便宜一些。

<2> 另一个问题,为什么要选择相同容量的两个内存?

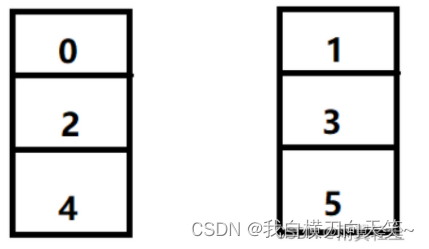

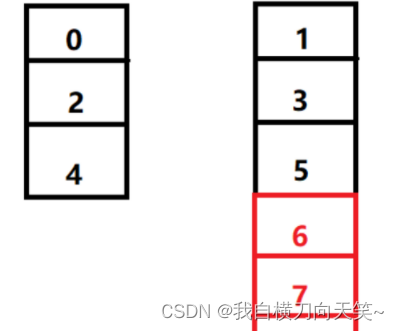

这点通过之前的讲解应该也不难理解。我们想要给两个内存条组成双通道,编址假如是 0、1、2、3、4、5 。

如果你新加的内存,它的容量比以前那根大很多,再往后的地址是不是就变成了6、7、8、9、10?也就是低地址部分,这两个内存可以组成双通道,而高地址部分其实依然是一个单通道的性能。

所以如果你插的两个内存条,它的容量不一样,有可能你会发现你的电脑性能会不太稳定。 如果你打游戏的时候,你的游戏刚好被装到了低地址部分,这个时候你的游戏可能会运行得更流畅一些,画面、帧速什么都会更好。但是如果你的游戏被放到了高地址部分,你的游戏运行起来就会更卡。所以,如果组成双通道的两根内存,它的容量不一样,你的电脑性能有可能更不稳定。

我在网上找了有一个人,他的笔记本电脑的一个配置的截图,他刚好截了这样的两张图。左边这张图说明的是整个电脑的概况。它的内存是 16GB 的一个 MacBook Pro。

但是如果查看内存的详细页面,你会看到他的这台电脑里边其实也是插了两根 8GB 的内存条。第一根内存条插在了 0 号卡槽里,第二根内存条插在了 2 号卡槽里。如果我没有猜错,他的这台电脑主板应该也是有四个卡槽,编号分别是0123。和之前那张图一样,插到 0 号和 2 号的时候,就可以组成一个双通道。所以这台苹果电脑,它在出厂的时候,其实已经考虑到双通道这个问题了。

5023

5023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?