总结:

看一个公司或者团队是不是真正做到了数据驱动,就要看它的决策流程中有没有 A/B 测试这一环节。

为什么用AB测试?

A/B 测试,就是保证关键环节不出现问题的最佳方案。因为它不仅可以让我们清楚地知道产品 / 迭代方案到底有没有效果,能产生多大效果,还可以在结果不如预期时,快刀斩乱麻,有理有据地放弃这个想法。这样既能大大节省公司的成本,又能加快想法迭代的速度。如果在花费了大量时间和资源实施想法后,还收不到预期的效果,那就得不偿失了。

只有在决策流程中加入 A/B 测试这个环节,根据值得信赖的测试结果,而不是所谓的经验来做业务和产品决策时,才是真正的数据驱动决策

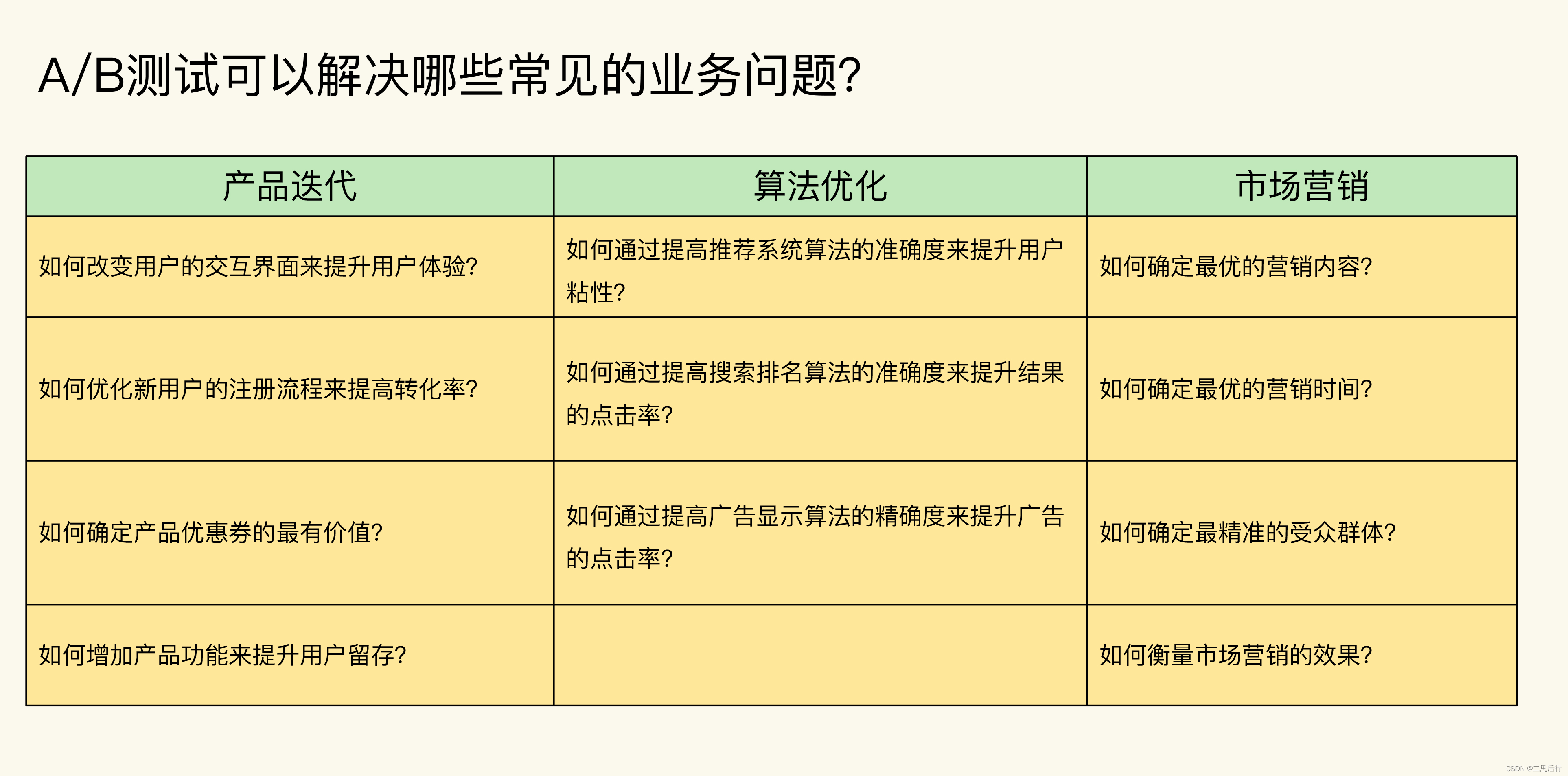

Ab测试能解决什么问题?

A/B 测试的理论基础是假设检验(Hypothesis Testing)

指标的统计属性,指的是什么?

在实际业务中,我们常用的指标其实就是两类:均值类的指标,比如用户的平均使用时长、平均购买金额、平均购买频率,等等。概率类的指标,比如用户点击的概率(点击率)、转化的概率(转化率)、购买的概率(购买率),等等。

我们可以用概率分布(Probability Distribution),来表征随机变量取不同值的概率和范围。所以,A/B 测试指标的统计属性,其实就是要看这些指标到底服从什么概率分布。

在数量足够大时,均值类指标服从正态分布;概率类指标本质上服从二项分布,但当数量足够大时,也服从正态分布。

中心极限定理(Central Limit Theorem)

这其实是均值类变量的特性:当样本量足够大时,均值类变量会趋近于正态分布。这背后的理论基础,就是中心极限定理。中心极限定理的数学证明和推理过程十分复杂,但不用害怕,我们只要能理解它的大致原理就可以了:不管随机变量的概率分布是什么,只要取样时的样本量足够大,那么这些样本的平均值的分布就会趋近于正态分布。那么,这个足够大的样本量到底是多大呢?统计上约定俗成的是,样本量大于 30 就属于足够大了。在现在的大数据时代,我们的样本量一般都能轻松超过 30 这个阈值,所以均值类指标可以近似为正态分布。到这里,“数量足够大”具体是需要多大的数量,以及什么是正态分布,这两个问题我们就都明白了。接下来,我们再学习下什么是二项分布,之后我们就可以理解为什么概率类指标可以既服从二项分布又服从正态分布了。

二项分布(Binomial Distribution)

业务中的概率类指标,具体到用户行为时,结果只有两种:要么发生,要么不发生。比如点击率,就是用来表征用户在线上点击特定内容的概率,一个用户要么点击,要么不点击,不会有第三种结果发生。这种只有两种结果的事件叫做二元事件(Binary Event)。二元事件在生活中很常见,比如掷硬币时只会出现正面或者反面这两种结果,所以统计学中有专门有一个描述二元事件概率分布的术语,也就是二项分布(Binomial Distribution)。

在二项分布中,有一个从实践中总结出的经验公式:min(np,n(1-p)) >= 5。其中,n 为样本大小,p 为概率的平均值。

这个公式的意思是说,np 或者 n(1-p) 中相对较小的一方大于等于 5,只有二项分布符合这个公式时,才可以近似于正态分布。这是中心极限定理在二项分布中的变体

708

708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?