实验目的

- 认识Nexys3教学开发板的硬件,熟悉其各个硬件接口。

- 熟悉Xilinx ISE 集成开发环境,掌握创建工程、调试、仿真、下载、硬件测试的方法,熟悉各个实验环节和完整开发流程。

- 学习使用与、或、非等基本逻辑们进行电路设计,掌握Verilog HDL语言的结构建模方法。

实验要求

- 使用门级描述来实现五输入表决器。

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,生成*.bit文件,完成板级验证。

- 撰写实验报告。

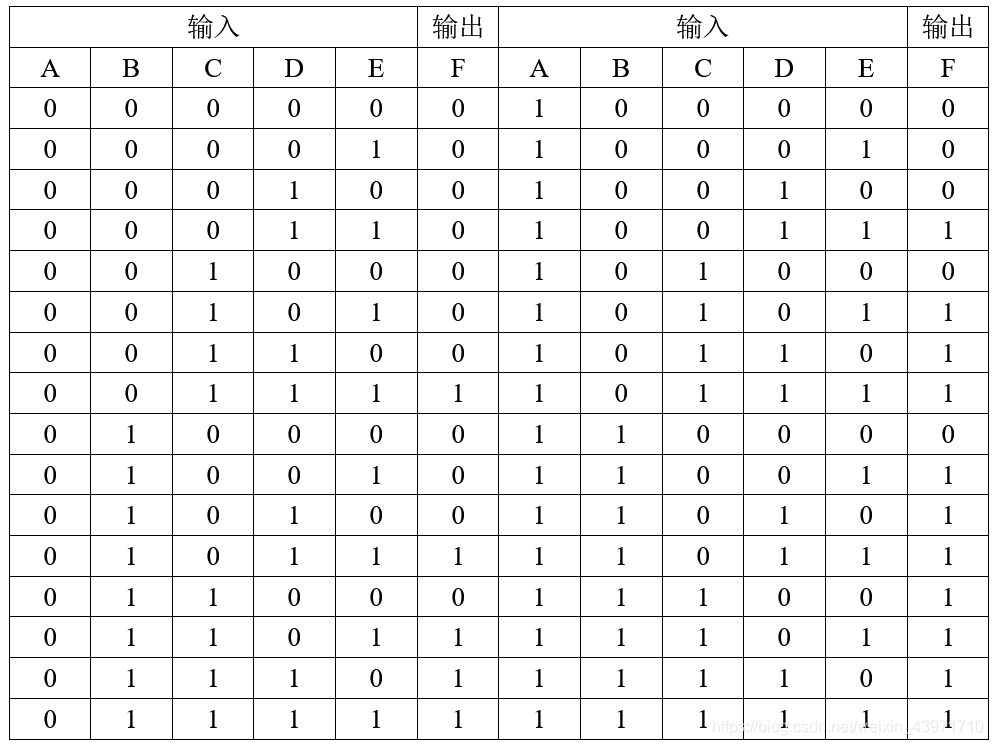

实验原理

程序代码

module WuWei(A,B,C,D,E,F);

input A,B,C,D,E;

output F;

wire A,B,C,D,E,F;

assign F=((A&B&C)||(A&B&D)||(A&B&E)||(A&C&D)||(A&C&E)||(A&D&E)||(B&C&D)||(B&C&E)||(B&D&E)||(C&D&E));

endmodule

测试用例

initial begin

A = 0;B = 0;C = 0;D = 0;E = 0;

#100;

A = 1;B = 0;C = 0;D = 0;E = 0;

#100;

A = 1;B = 1;C = 0;D = 0;E = 0;

#100;

A = 1;B = 1;C = 1;D = 0;E = 0;

#100;

A = 1;B = 0;C = 1;D = 0;E = 1;

#100;

A = 1;B = 0;C = 1;D = 0;E = 0;

#100;

A = 1;B = 0;C = 1;D = 1;E = 1;

#100;

A = 1;B = 1;C = 1;D = 1;E = 1;

end

endmodule

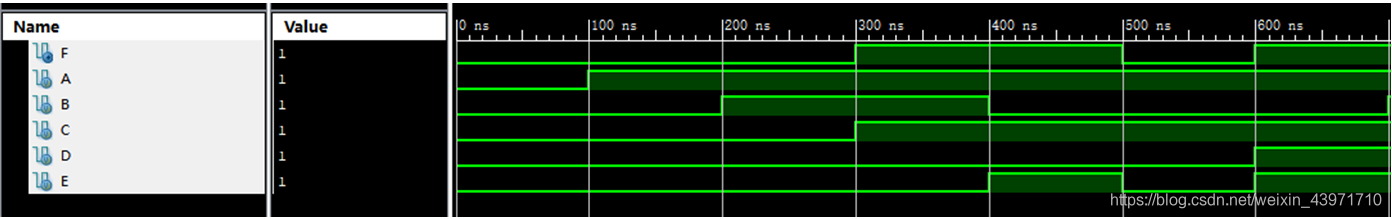

仿真波形图

从波形图可以看出:

输入为0,0,0,0,0,输出为0

输入为0,1,0,0,0,输出为0

输入为1,1,0,0,0,输出为0

输入为1,1,1,0,0,输出为1

输入为1,0,1,0,1,输出为1

因此该模块实现了五输入表决器的功能。

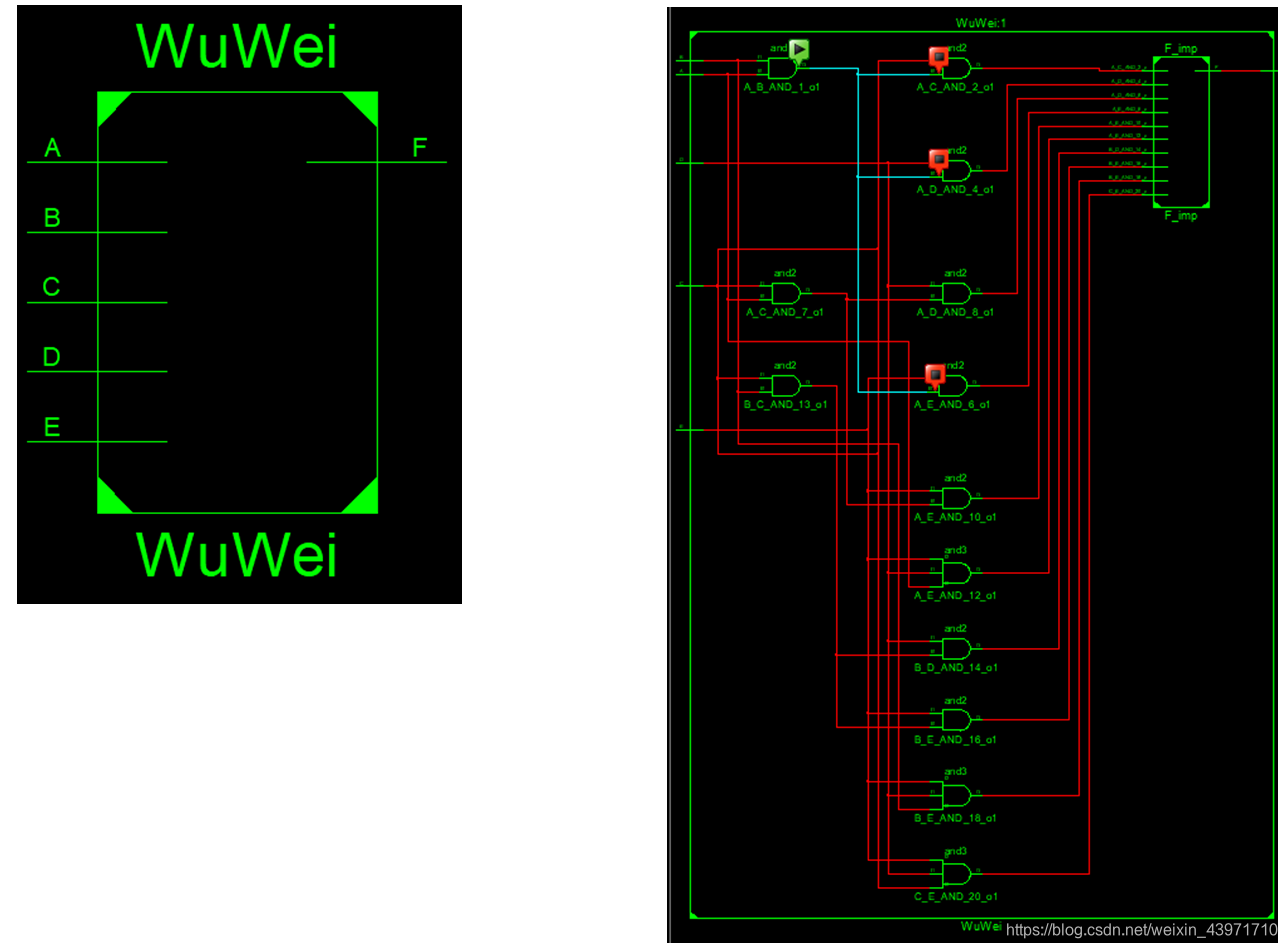

电路管脚图

引脚配置文件

NET "A" IOSTANDARD = LVCMOS18 | LOC = T3; //SW1

NET "B" IOSTANDARD = LVCMOS18 | LOC = U3; //SW1

NET "C" IOSTANDARD = LVCMOS18 | LOC = T4; //SW3

NET "D" IOSTANDARD = LVCMOS18 | LOC = V3; //SW4

NET "E" IOSTANDARD = LVCMOS18 | LOC = V4; //SW5

NET "F" IOSTANDARD = LVCMOS18 | LOC = R1; //LED01

NET "A" PULLDOWN;

NET "B" PULLDOWN;

NET "C" PULLDOWN;

NET "D" PULLDOWN;

NET "E" PULLDOWN;

工程文件

工程文件: 五输入表决器设计实验.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?