实验目的

- 学习数码管的显示原理,掌握数码管的动态扫描方法。

- 掌握灵活运用Verilog HDL 语言进行各种描述与建模的技巧和方法。

实验要求

- 使用合适的描述方式编程实现规定功能的数码管扫描显示模块。

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,生成*.bit文件,完成板级验证。

- 撰写实验报告。

实验原理

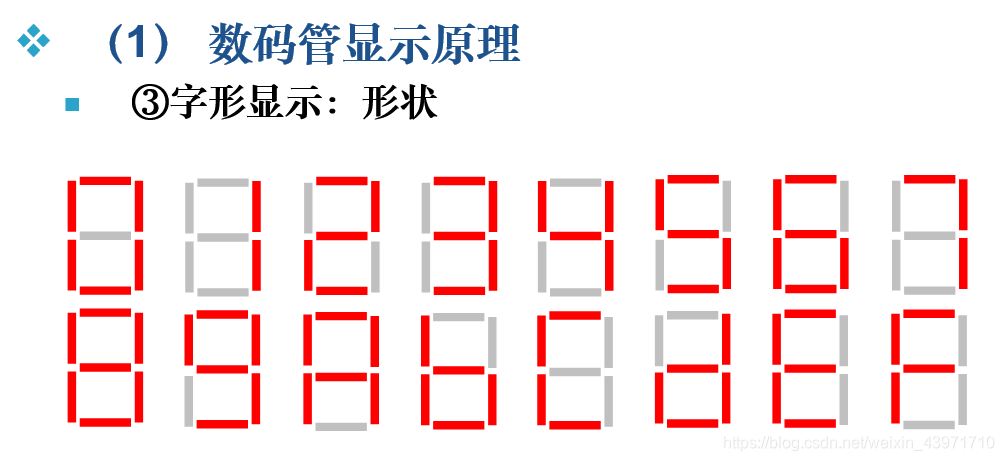

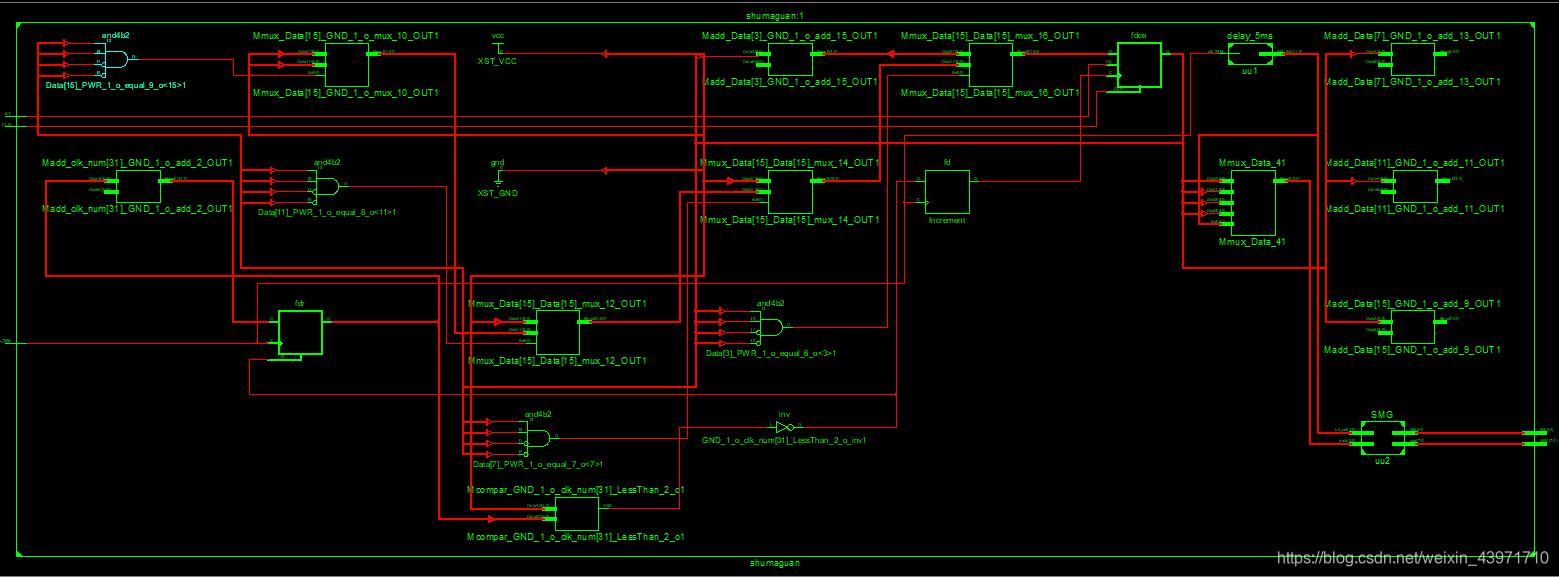

数码管扫描显示的实现方法:

要点亮某数码管,只需改变位选信号AN[3:0]以选择对应的数码管。要使该数码管显示特定的数值,需要对段选信号CA~CG进行特定的赋值,根据想要显示的数值向不同的段选信号输入有效信号。要使数码管上稳定地显示4个数字,只需分时选通各个数码管显示其对应的数字,并且设置一个较高的刷新频率即可。

为实现数码管内部的轮流选通显示,设置了一个会随时钟脉冲改变的内部变量BIT_SEL[1:0]来选择数码管以及要显示的数值。设置了一个16位寄存器来存放累加数据,每4位对应一个10进制位,并设置了一种特殊的进位方法实现16进制进位到10进制进位的转换。第一个数码管显示[15:12],依次类推。

程序代码

module shumaguan(

input ST,

input CLR,

input clk_25M,

output [3:0] AN,

output [7:0] SEG

);

reg[15:0] Data;

reg[3:0] Data_4;

wire[1:0] BIT_SEL;

reg Increment; //脉冲

integer clk_num=0; //计数器

delay_5ms uu1(clk_25M,BIT_SEL);

initial begin Data <= 16'b0; Increment = 1'b0;end

always@(posedge clk_25M)

begin

if(clk_num<5000000)

begin

clk_num=clk_num+1;

Increment = 1'b0;

end

else

begin

clk_num=0;

Increment = 1'b1;

end

end

always@(posedge CLR or posedge Increment)

if(CLR)

begin

Data <= 16'b0000000000000000;

end

else if(ST)

begin

if(Data[3:0]==4'b1001)begin

Data[3:0]<=4'b0000;

if(Data[7:4]==4'b1001)begin

Data[7:4]<=4'b0000;

if(Data[11:8]==4'b1001)begin

Data[11:8]<=4'b0000;

if(Data[15:12]==4'b1001)

Data[15:12]<=4'b0000;

else

Data[15:12]<=Data[15:12]+4'b0001;

end

else

Data[11:8]<=Data[11:8]+4'b0001;

end

else

Data[7:4]<=Data[7:4]+4'b0001;

end

else

Data[3:0]<=Data[3:0]+4'b0001;

end

always @(*) // case(BIT_SEL)控制每个数码管显示对应位的数字

//根据BIT_SEL,将要显示的4位十六进制数赋给Data_4

begin

case(BIT_SEL)

0:Data_4[3:0]<=Data[15:12];

1:Data_4[3:0]<=Data[11:8];

2:Data_4[3:0]<=Data[7:4];

3:Data_4[3:0]<=Data[3:0];

default:Data_4[3:0]<=Data[3:0];

endcase

end

SMG uu2(Data_4,BIT_SEL,SEG,AN);

endmodule

module delay_5ms(clk_25M,BIT_SEL);

input clk_25M;

output reg[1:0] BIT_SEL;

integer cnt=0;

initial begin BIT_SEL <= 2'b00;end

always@(posedge clk_25M)

begin

cnt<=cnt+1;

if(cnt>50000)

begin

BIT_SEL<=BIT_SEL+2'b01;

cnt<=0;

end

end

endmodule

module SMG(

input wire[3:0] data, //要显示的数字

input wire[1:0] bit_sel, //数码管选择,00~11 最左到最右

output reg[7:0] seg, //段选

output reg[3:0] AN //位选

);

always @(*)

begin

case(bit_sel)

2'b00:AN<=4'b1000;

2'b01:AN<=4'b1001;

2'b10:AN<=4'b1010;

2'b11:AN<=4'b1011;

default:AN<=4'b1111;

endcase

end

always @(*)

begin

case(data[3:0])

0:seg[7:0]<=8'b00000011;

1:seg[7:0]<=8'b10011111;

2:seg[7:0]<=8'b00100101;

3:seg[7:0]<=8'b00001101;

4:seg[7:0]<=8'b10011001;

5:seg[7:0]<=8'b01001001;

6:seg[7:0]<=8'b01000001;

7:seg[7:0]<=8'b00011111;

8:seg[7:0]<=8'b00000001;

9:seg[7:0]<=8'b00001001;

default:seg[7:0]<=8'b11111111;

endcase

end

endmodule

测试用例

initial begin

CLR = 0;

ST= 0;

clk_25M = 0;

#100;

CLR = 0;

ST= 1;

end

always #20 clk_25M=~clk_25M;

endmodule

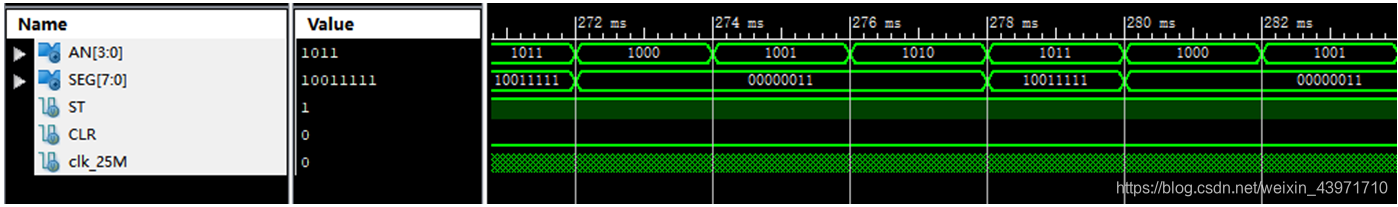

仿真波形图

从波形图可以看出,当时钟脉冲到达一定数量时,位选信号AN[3:0]和段选信号SEG[7:0]发生改变,以实现数码管的切换以及显示数据的切换。因为切换的频率极高,肉眼看上去则为四个数码管同时显示。

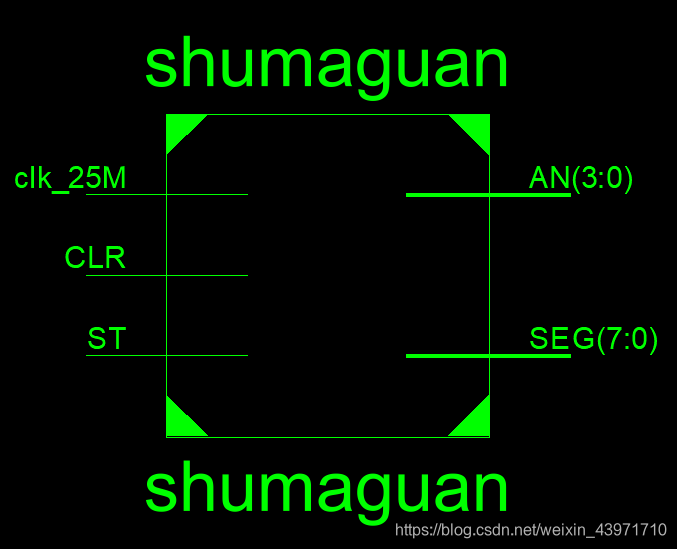

电路管脚图

引脚配置文件

NET "ST" LOC = T3;

NET "ST" IOSTANDARD = LVCMOS18;

NET "CLR" LOC = U3;

NET "CLR" IOSTANDARD = LVCMOS18;

NET "AN[3]" LOC = L21;

NET "AN[3]" IOSTANDARD = LVCMOS18;

NET "AN[2]" LOC = M22;

NET "AN[2]" IOSTANDARD = LVCMOS18;

NET "AN[1]" LOC = M21;

NET "AN[1]" IOSTANDARD = LVCMOS18;

NET "AN[0]" LOC = N22;

NET "AN[0]" IOSTANDARD = LVCMOS18;

NET "SEG[7]" LOC = H19;

NET "SEG[7]" IOSTANDARD = LVCMOS18;

NET "SEG[6]" LOC = G20;

NET "SEG[6]" IOSTANDARD = LVCMOS18;

NET "SEG[5]" LOC = J22;

NET "SEG[5]" IOSTANDARD = LVCMOS18;

NET "SEG[4]" LOC = K22;

NET "SEG[4]" IOSTANDARD = LVCMOS18;

NET "SEG[3]" LOC = K21;

NET "SEG[3]" IOSTANDARD = LVCMOS18;

NET "SEG[2]" LOC = H20;

NET "SEG[2]" IOSTANDARD = LVCMOS18;

NET "SEG[1]" LOC = H22;

NET "SEG[1]" IOSTANDARD = LVCMOS18;

NET "SEG[0]" LOC = J21;

NET "SEG[0]" IOSTANDARD = LVCMOS18;

NET "ST" PULLDOWN;

NET "CLR" PULLDOWN;

NET "clk_25M" IOSTANDARD = LVCMOS18;

NET "clk_25M" LOC = H4;

数码管说明

在实验中,如果感觉数字闪烁,表示数码管选择的刷新率太低了,肉眼能够观察出来,因此应该提高刷新率,即接收更少的电平脉冲就改变一次数码管的位选和段选信号。

在实验中,我还遇到了数码管的位选信号无法确定的问题,因此我代入不同的位选信号参数进行验证,根据输入的位选信号观察亮起的是第几个数码管,最终总结出位选信号的规律如下:

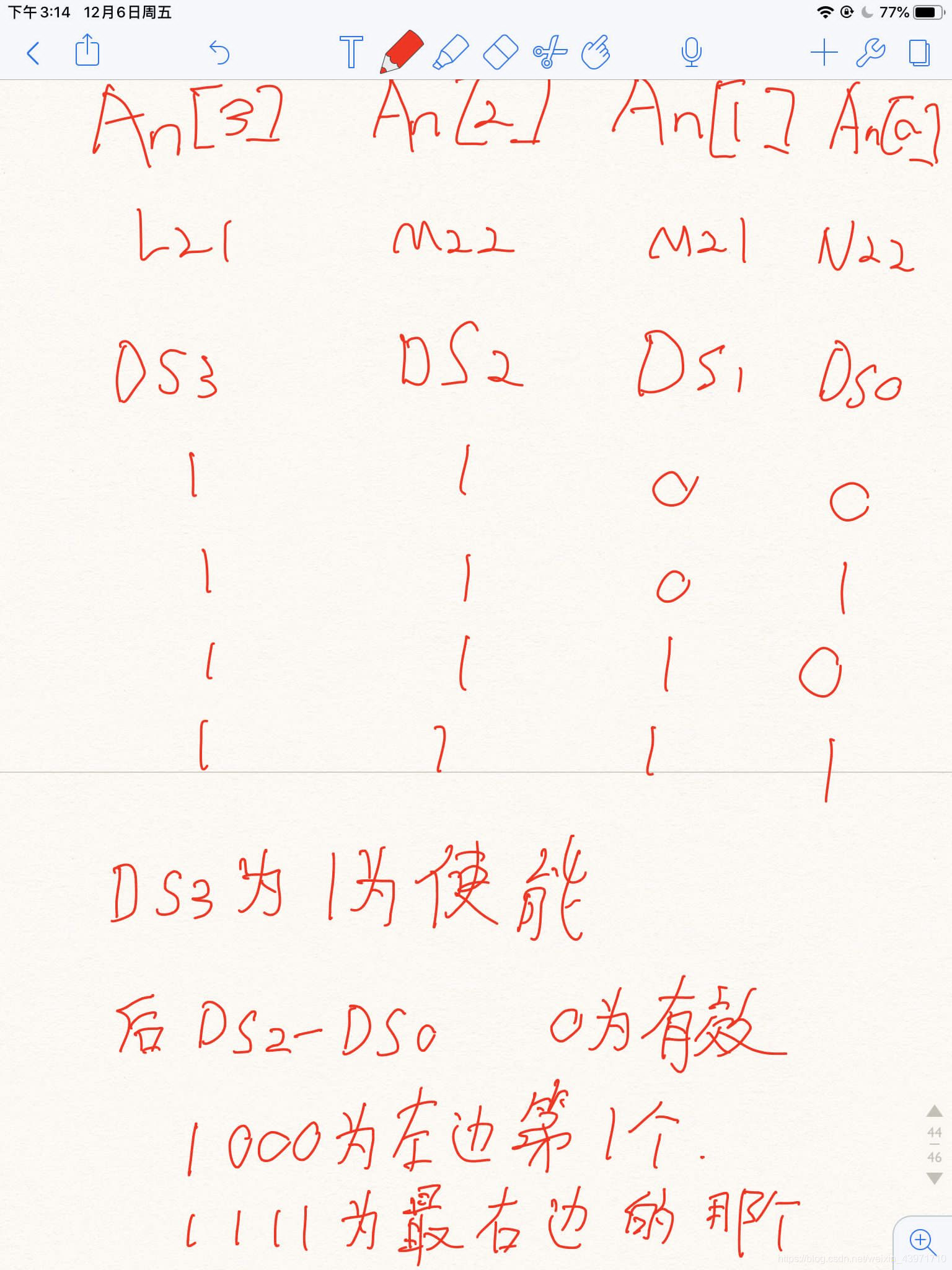

我的代码中AN[3:0]分别对应DS3~DS0

位选信号为1100 1101 1110 1111分别对应左数第5-8个数码管

因此我总结出规律 AN[3],即DS3为使能信号,1为使能。

后三位分别为选择信号,0表示有效,DS2为高位,因此

1100 1101 1110 1111 分别代表 3 2 1 0,则数码管从左往右对应7-0

左数第一个数码管位选信号为1000(7)右数第一个数码管位选信号为1111(0)

工程文件

工程文件: 数码管扫描显示实验.

关注我即可下载

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?