实验目的

- 掌握计算机中实现定时的基本方法,理解定时、频率和计数之间的关系

- 掌握分频器的原理和实现方法

- 掌握灵活运用VerilogHDL语言进行各种描述与建模的技巧和方法

实验要求

- 使用合适的描述方式实现定时与分频模块。

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,生成*.bit文件,完成板级验证。

- 撰写实验报告。

实验原理

分频器的实现方法:

想要对时钟脉冲进行分频,只需要对时钟的脉冲进行捕获,根据时钟脉冲的频率进行计算,捕获到一定量的时钟脉冲,再对输出信号进行翻转即可,捕捉时钟脉冲的量视分频情况而定。

定时器的实现方法

想要根据时钟脉冲进行定时,只需要对时钟的脉冲进行捕获,根据时钟脉冲的频率进行计算,捕获到一定量的时钟脉冲,再改变输出信号即可。

程序代码

module zhu(clk,reset,SW,led);//主模块

input clk,reset;

input [1:0] SW;

output reg led;

wire out1,out2,out3,out4;

Fdiv fd1(reset,clk,32'd25000000,out1);

Fdiv fd2(reset,clk,32'd12500000,out2);

Fdiv fd3(reset,clk,32'd6250000,out3);

Clock c1(clk,reset,out4);

always@(*) begin

case(SW)

2'b00:led=out1;

2'b01:led=out2;

2'b10:led=out3;

2'b11:led=out4;

endcase

end

endmodule

//分频模块

module Fdiv(input reset,input clk_ori,input [31:0] f,output reg clk_new);

reg [31:0] counter;

initial begin counter=32'd0;end

initial begin clk_new=0;end

always @(posedge reset or negedge clk_ori) begin

if(reset) begin

counter<=32'd0;clk_new<=1'b0;end

else if(counter==f-1) begin

clk_new<=~clk_new;

counter<=32'd0;end

else

counter<=counter+1'b1;

end

endmodule

//定时模块

module Clock(input clk,input reset,output reg led);

integer i=0;

initial begin led=0;end

always @(negedge clk,posedge reset) begin

if(reset) begin

i=0;led=0;end

else if(i==150000000)

led=1;

else if(i<150000000)

i=i+1;

else ;

end

endmodule

测试用例

always #20 clk=~clk;

initial begin

// Initialize Inputs

clk = 0;

reset = 0;

SW = 0;

// Wait 100 ns for global reset to finish

#2000000000;

// Add stimulus here

reset=0;

SW=2'b01;

#1000000000;

reset=0;

SW=2'b10;

#1000000000;

reset=0;

SW=2'b11;

end

endmodule

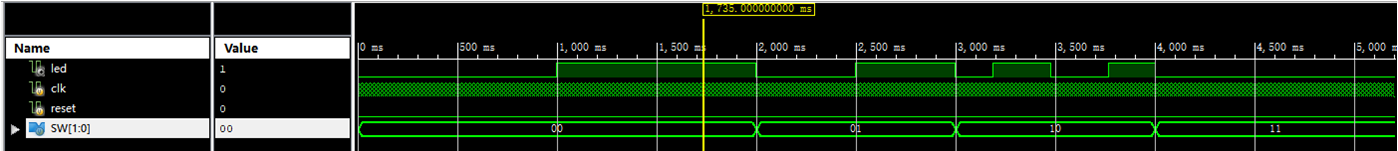

仿真波形图

从波形图可以看出:

分频模块的输出频率分别为0.5hz,1hz,2hz,

定时模块在6s定时后输出1

电路管脚图

引脚配置文件

NET "SW[0]" IOSTANDARD = LVCMOS18 | LOC = T3;

NET "SW[1]" IOSTANDARD = LVCMOS18 | LOC = U3;

NET "reset" IOSTANDARD = LVCMOS18 | LOC = R4;

NET "clk" IOSTANDARD = LVCMOS18 | LOC = H4;

NET "led" IOSTANDARD = LVCMOS18 | LOC = R1;

NET "SW[0]" PULLDOWN;

NET "SW[1]" PULLDOWN;

NET "reset" PULLDOWN;

工程文件

工程文件: 定时与分频实验.

关注我即可下载

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?