代码仅供参考:

链接:pan.baidu.com/s/1VekND1K50yclOKdkSI-otw

up1k

一、实验目的

- 熟悉计数器、寄存器和 RAM 的工作原理。

- 了解模型机中 SM 的作用。

- 学会使用 VHDL 语言设计时序电

二、实验内容

- 用 VHDL 语言设计 SM;

- 用 VHDL 语言设计一个 8 位的指令计数器 PC;

- 用 VHDL 语言设计 3 个 8 位寄存器组成的寄存器组,实现读写操作;

- 用 LPM_RAM_IO 定制一个 256*8 的 RAM,实现对 RAM 的读写操作。

三、实验方法

(一)实验方法

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是Quartus II。

(二)实验步骤

SM、PC、通用寄存器组文件创建过程(三个文件过程相似,以SM为例)

1、 新建工程,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name为SM)-【next】(设置文件名SM.vhd—在【add】)-【properties】(type=VHDL)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(VHDL File)-【OK】

2、 写好源代码,保存文件(SM.vhd)。

3、 编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译,编译成功。

4、 波形仿真及验证。新建一个vector waveform file。按照程序所述插入CLK,EN,z三个节点(CLK、EN为输入节点,z为输出节点)。(操作为:右击 -【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。任意设置C的输入波形…点击保存按钮保存。(操作为:点击name(如:CLK))-右击-【value】-【Random】(如设置Every grid interval),同理设置name EN(Every grid interval),保存)。然后【start simulation】,出name z的输出图。

5、 时序仿真或功能仿真。

6、 查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

RAM文件创建过程(顶层文件为BDF文件)

1、 新建一个工程,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name为RAM)-【next】(设置文件名RAM.bdf—在【add】)-【properties】(type=Block Diagram/Schematic)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】

(2).新建:【file】-【new】(Block Diagram/Schematic File)-【OK】

2、 用模板库中的LPM_RAM_IO与三态门Tri以及INPUT、OUTPUT原件画好原理图,保存文件(SM.bdf)。

3、 编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译,编译成功。

4、 波形仿真及验证。新建一个vector waveform file。按照程序所述插入addr、CLK、XL、DL、DATAIN、Fout节点(addr、CLK、XL、DL、DATAIN为输入节点,Fout为输出节点)。(操作为:右击 -【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。任意设置C的输入波形…点击保存按钮保存。(操作为:点击name(如:XL))-右击-【value】-【Random】(如设置Every grid interval),同理设置name DL(Every grid interval),保存)。然后【start simulation】,出name sum和name Fout的输出图。

5、 时序仿真或功能仿真。

6、 查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

四、实验过程

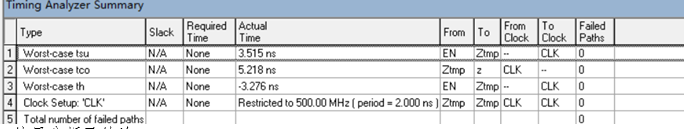

A. SM

1、 编译过程

a. 源代码如图(VHDL设计)

b. 编译、调试过程

无错误信息,编译通过。

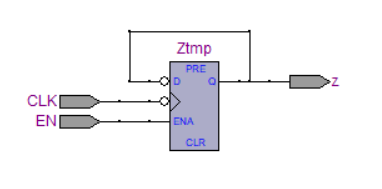

c. RTL视图

d. 结果分析及结论

根据以上SM功能表来看,SM部件实际上是时序电路,因为当EN为0时SM保持不变,所以其实现是实际上是一个带控制端的触发器,而VHDL语言中的process进程中的if语句恰好可以实现这个功能,因此满足条件。

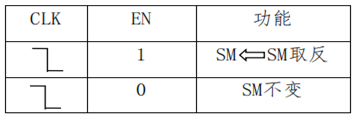

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

b. 波形仿真波形图

c. 结果分析及结论

10ns:CLK为下降沿,EN=1,SM取反,z=1,结果正确;

20、30、40ns:CLK为下降沿,EN=0,SM不变,z=0,结果正确;

50ns:CLK为下降沿,EN=1,SM取反,z=1,结果正确;

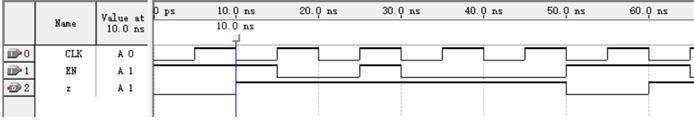

3、 时序仿真

a. 时序仿真过程

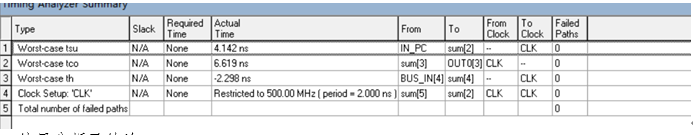

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【summary】

b. 时序仿真图

c. 结果分析及结论

tsu为3.515ns(From EN To Ztmp),tco为5.218ns(From Ztmp To z),th为-3.276ns(From EN To Ztmp)。

B. 指令计数器PC

1、 编译过程

a. 源代码如图(VHDL设计)

b. 编译、调试过程

无编译错误。

c. RTL视图

d. 结果分析及结论

指令计数器PC是时序电路,因此在VHDL程序中同样使用if语句来实现存储功能(存储PC),在RT视图中可以看到PC由触发器进行了存储,触发器的输出端经过一个加法器(加一),如果IN PC为1,则选择器将加一后的PC输入触发器的输入端,否则将总线上的输入数据BUS_IN输入到触发器输入端,满足条件。

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

b. 波形仿真波形图

c. 结果分析及结论

10ns:CLK为下降沿,IN_PC=1、LD_PC=0,PC+1,OUT0=1,结果正确;

20ns:CLK为下降沿,IN_PC=0、LD_PC=1,PC<=BUS_IN,BUS_IN=31,OUT0=31,结果正确;

30ns:CLK为下降沿,IN_PC=1、LD_PC=0,PC+1,OUT0=32,结果正确;

40ns:CLK为下降沿,IN_PC=0、LD_PC=1,PC<=BUS_IN,BUS_IN=11,OUT0=11,结果正确。

3、 时序仿真

a. 时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【Summary】

b. 时序仿真图

c. 结果分析及结论

全局时钟的建立时间tsu为4.142ns(From IN_PC To sum[2]),时钟上升沿与输出端数据稳定输出的时间差tco为6.619ns(Fromsum[3] To OUT0[3]),在时钟上跳沿后,信号必须保持的最小时间th为-2.298ns(From BUS_IN[4] To sum[4])。

C. 通用寄存器组

1、 编译过程

a. 源代码如图(VHDL设计)

b. 编译、调试过程

无错误信息。

c. RTL视图

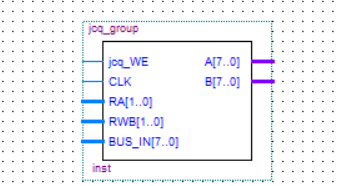

逻辑符号:

d. 结果分析及结论

通用寄存器组同样是一个时序电路,根据功能表,

当WE为1时,根据RAA[1…0]的值从A,B,C中选择一个寄存

器的值由AO口输出

如RAA[1…0]=00,AO<=A寄存器的值

RAA[1…0]=01,AO<=B寄存器的值

RAA[1…0]=10,AO<=C寄存器的值

根据RWBA[1…0]的值从选择A,B,C中选择一个

寄存器的值由BO口输出,

如RWBA[1…0]=00,BO<=A寄存器的值

RWBA[1…0]=01,BO<=B寄存器的值

RWBA[1…0]=10,BO<=C寄存器的值

当时钟处于下降沿且WE为0时,根据RWBA[1…0]的值,将外部输入写入A,B,C

三个寄存器中的一个寄存器内。

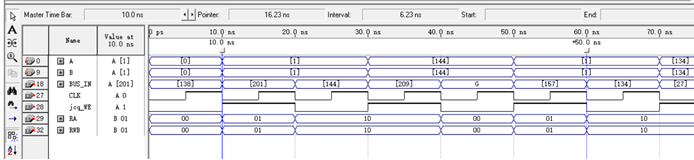

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

b. 波形仿真波形图

c. 结果分析及结论

10ns:CLK为下降沿,jcq_WE=1,RA=01,RWB=01,则A<=A寄存器,B<=A寄存器,

A=0,B=0(A寄存器初始值为0),结果正确;

20ns-30ns:jcq_WE=0,RWB=10,则C寄存器<=BUS_IN,BUS_IN=144;

30ns:CLK为下降沿,jcq_WE=1,RA=10,RWB=10,则A<=C寄存器,B<=C寄存器,

A=144,B=144(C寄存器此时为144),结果正确;

即对寄存器进行读写的操作都与功能表相应,其余寄存器不再赘述,结果正确。

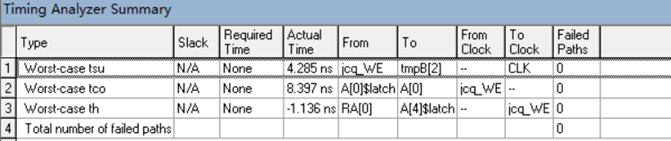

3、 时序仿真

a. 时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【Summary】

b. 时序仿真图

c. 结果分析及结论

全局时钟的建立时间tsu为4.285ns(Fromjcq_WE To tmpB[2]),时钟上升沿与输出端数据稳定输出的时间差tco为8.397ns(From A[0]

l

a

t

c

h

T

o

A

[

0

]

)

,

在

时

钟

上

跳

沿

后

,

信

号

必

须

保

持

的

最

小

时

间

t

h

为

−

1.136

n

s

(

F

r

o

m

R

A

[

0

]

T

o

A

[

4

]

latch To A[0]),在时钟上跳沿后,信号必须保持的最小时间th为-1.136ns(From RA[0] To A[4]

latchToA[0]),在时钟上跳沿后,信号必须保持的最小时间th为−1.136ns(FromRA[0]ToA[4]latch)。

D. RAM

1、 编译过程

a. 源代码如图(BDF设计)

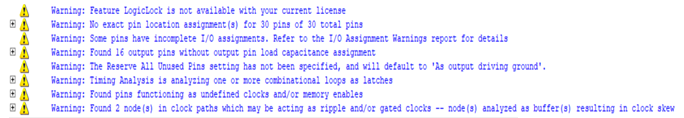

b. 编译、调试过程

无错误信息。

c. RTL视图

逻辑符号:

d. 结果分析及结论

采用Quartus中已有的参数化模块来定制RAM功能,在【Symbol】元件库的【megafunctions】|【storage】中选择LPM_RAM_IO,创建RAM时加载初始化数据文件,初始化文件的创建过程是:【File】|【New】|【Memory Initialization File】。

根据功能表可以知道对存储单元数据的读写是在时钟上升沿发生的。而输出Fout则是根据XL、DL来改变的,当XL为1、DL为0时Fout输出输入的数据;而当XL为0,DL为1时并且时钟处于上升沿时Fout输出的是存储单元的数据,而我开始时认为Fout输出的完全随时钟上升沿改变,这是错误的观点(Fout并不是Dio!)。因此我在后面波形仿真时进入了误区,很不应该。

2、 波形仿真

a. 波形仿真过程(详见实验步骤)

b. 波形仿真波形图

c. 结果分析及结论

(以上仅对第一个地址进行读写操作)

0-3.5ns:XL=1,DL=0,此时CLK不在上升沿因此不进行写操作,仅Fout<=DATAIN,DATAIN=Y,Fout=Y,结果正确;

5ns:XL=0,DL=1,CLK处于上升沿,进行读操作,地址中为1,Fout=1,读操作正确;

15ns:XL=1,DL=0,CLK处于上升沿,进行写操作,DATAIN=228,因此此时地址中的数据应为228,此外Fout=228;

15-25ns之间无时钟上升沿,因此不进行读写操作,Fout在XL变1且DATAIN改变时改变;

25ns:XL=0,DL=1,CLK处于上升沿,进行读操作,地址中数据为15ns时写入的228,Fout=228,说明写操作同样正确;

(之前在验收时我写的波形之Fout所以没有随CLK上升沿变化就是因为在CLK上升沿到来之前随XL变化了,以上波形图能正确解释CLK上升沿问题)。

3、 时序仿真

a. 时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

b. 时序仿真图

c. 结果分析及结论

XL引脚到Fout[4]引脚的实际p2p时间最长且为9.834ns,故整体为10.591ns。

tpd (引脚到引脚的延时)

全局时钟的建立时间tsu为6.513ns,时钟上升沿与输出端数据稳定输出的时间差tco为9.254ns,在时钟上跳沿后,信号必须保持的最小时间th为-2.214ns。

五、实验结论

这四个CPU时序部件都可以通过功能表做出来,相对于实验3中的串行加法器还要简单一些,最大的问题出在了RAM的波形仿真中,一开始时我设置的波形以及仿真出来的Fout输出不能看出CLK上升沿与读写操作的必要联系,我就觉得RAM中的CLK不对劲。后来回去仔细想了想发现了问题的关键——Fout输出不是dio,Fout的改变还受到了XL的影响,并且这种影响还不会受时钟的控制,当XL为1时无论是否是处于时钟上升沿,Fout都会先输出DATAIN,这就是为什么Fout的波形看上去与CLK关系不大的主要原因,而RAM中的CLK是完全可行的!

希望做CPU的时候能避免以前犯下的错误。

1058

1058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?