数字系统实验--第九-十周任务1. 认识USB通信芯片FT245BM和平台、CRC校验、

四个任务实现工程链接:https://pan.baidu.com/s/1-6HGOhA5Sb6GFx0yhtD9Fw

提取码:l3mj

硬件语言描述训练2任务书

- 简介

理解数字系统实验板(DDA-IIIA型)FT245BM串口数据收发工作原理、序列检测器原理与状态图输入法

分层次编写VHDL完成FPGA与外设交互的串行数据通信、 验证平台、CRC检验(可选)- 认识USB通信芯片FT245BM和平台

时间:

1至2周

步骤:

阅读教材P317-318的FT245芯片的介绍,理解其工作原理,数据接收与发送的流程。

阅读教材P192状态机概述部分。

课程平台上下载资料。

实操:D级任务(70%)

- P192序列检测器1110010的状态图输入法。

要求:仿真验证结果波形。 - P319,6.1.4-1,上位机向实验板传输数据。

要求:用VHDL状态图输入法实现接收控制信号交互部分,并通过顶层电路图BDF方式搭建验证电路完成仿真验证,并依据如下实验板通信图片分配好管脚并截图记录。注意:接收数据需要暂存。

实操:C级任务(80%)

- Proteus串口通信。

步骤:学习观看虚拟串口的仿真过程。

完成虚拟串口驱动安装。

配置虚拟串口并连接。

新建Proteus工程,并设计好COM9上下位机通信电路。添加相应仪器,分别实现电脑串口助手与Proteus内COM9的发送与接收的功能并记录。

- 通信电路电平转换。

步骤:阅读MAX232数据手册中输入与输出端高低电平的电压范围。

要求:新建Proteus工程,设计好MAX232电平转换电路,添加信号发生仪器、电压探针或电压表,观察输入端与输出端的高低电平或波形,完成记录并分析RS232电平与TTL电平。

实操:B级任务(90%)

1. C级电路的数据接收增强电路。

步骤:

阅读74HC595数据手册。

利用74HC595实现接收数据缓存和数码管显示电路。

2. C级电路的发送数据增强电路。

步骤:上去掉信号发生器,再利用2片74LS194、开关、LED-GREEN实现发送数据缓存和LED灯显示电路。

要求:上下位通信正常,并记录接收和发送显示数据。

- CRC校验

时间:

1周

步骤:

阅读教材P325认识数字通信中CRC检验相关知识

实操:A级任务(100%)

P326的6.2.4,设计实现FT245BM交互驱动电路和编码校验。

要求:用状态图输入法实现控制信号交互,接收到数据需要完成CRC循环冗余验证后,将计算结果回传。验证方法使用Quartus仿真验证。 - 提交

本次任务作业报告请于第十周周日5月3日晚23:59分提交(PDF文件),文档正文不超过3页,大小不超过5M(不提供报告模板),工程文件不超过5M,要求如下:

- 教材勘误

硬件描述训练2实验报告

实验日期:2020.4.20-2020.5.05

实验内容:分层次编写VHDL完成FPGA与外设交互的串行数据通信、 验证平台、CRC检验;

工程截图见后附录;

一、 D级任务

1、 序列检测器1110010的状态图输入法

序列检测器的当前状态与输入和下一状态都相关,为mealy型状态机;

基于1110010序列检测器的状态图通过状态图输入法实现检测器,详见工程文件与附录截图;

波形仿真验证:

时钟周期:10ns; reset信号:复位信号,高有效; din:输入序列; z:输出信号

分析:

0-10ns:第一个周期reset信号有效,初始状态,此时为st0状态;

10-40ns:din为1,每个时钟上升沿都会进入下一个状态,st0->st1->st2->st3;

40-60ns:din为0,时钟上升沿时同样进入下一个状态,st3->st4->st5;

60-68ns:din为1,时钟上升沿由st5进入st6;

68ns后:din为0,在st6状态中,输入为0,输出为1,直到75ns处的时钟上升沿进入st0;

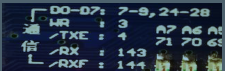

2、 上位机向实验板传输数

1) 状态图输入法实现接收控制信号交互

此时,接收数据需要暂存,因此,将输出信号存入寄存器;

根据实验指导书上的状态图,利用State Machine wizard实现该状态图:

除了状态图实现的控制信号组件外,右上图是利用寄存器74273b实现的可以暂存输入数据的组件,清零信号接高电平,利用与门控制寄存器在第三个状态且时钟上升沿变化;几个引脚按照图示进行连接;

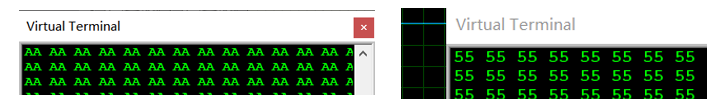

2) 仿真截图与分析

分析:

100-200ns:初始状态为wait_rxf_low,100ns处rxf设置为0,在第150ns处的上升沿处,进入第二个状态,rd变为0;

200-300ns:250ns处的上升沿进入第三个状态,此时令输出输入的值AA;

300-400ns:350ns上升沿处到第一个状态,rd变回1,此时看到输出值保持,满足暂存要求;

二、 C级任务(80%)

1、proteus串口通信

按照原理图设计好COM19上下位机通信电路(较为简单不再截图,见文件末尾);

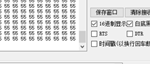

串口助手的COM19与proteus内COM20的发送与接受记录:(分别发送55、AA)

分析:在串口助手中COM19发送的AA和55都可以被正确的由protues中的COM20接收;

2、通信电路电平转换

建立Proteus工程,设计好MAX232电平转换电路;

MAX232的T1IN端是TTL/CMOS数据输入,经MAX232转换成RS-232数据从T1OUT送到电脑;T1IN端的电压接入波形观察器A端,T1OUT端接入B端,观察电压波形:

(示波器的A、B通道幅值调节相同;)

观察波形图发现,输入的TTL电平(输出高电平>2.4V,低电平<0.4V、输入高电平>=2.0V,低电平<=0.8V)经过MAX232的转换,变成PC机能接收的RS232电平标准(范围高电平-5-15V、低电平+5+15V);

三、 B级任务(90%)

1、C级电路的数据接收增强电路

利用74HC595实现接收数据缓存和数码管显示电路;

将下位机的55送至74HC595的串行输入端口,74HC595的MR复位端口置无效与OE输入端口置有效状态,数据输入时钟和数据输出时钟比较重要,要使其时钟在一个合适的值;结果如下:传输55进入,接收到55并且接在74HC595上的数码管显示55,需要RXD的时钟74HC595接受的时钟基本一致);AA、55都能很好的接受与保存;

2、C级电路的发送数据增强电路

在B的基础上去掉信号发生器,再利用2片74LS194、开关、LED-GREEN实现发送数据缓存和LED灯显示电路;

电路如下:

下位机接收数据如下:

这个问题卡了我很久,主要就是我将74LS164的MR和S0接到了同一个高电平当中,导致低四位向高四位传输时为不确定的(灰色);

仿真结果:

当输入55时,LED能正确显示,且开关闭合后向下位机传送55,下位机可以正确接受;

这里的实现方法是:当左下角的开关断开时,S1S0为11,并行输入,当开关闭合时,S1S0为01,向右移位;且将低4位Q3接到高四位SR,高四位Q3接到低四位SR形成闭环,也就是0101一直在循环移动,因此输入的数据每过8个周期都是0x55;

B级任务的关键在于整合COMPIM的TXD的时钟与74LS194的时钟以及RXD的时钟与74HC595的时钟;

四、 A级任务(100%)

1、将处理数据的模块与控制信号与状态转换模块放在一起生成usbconnection大模块;

csu_usb_control为使用状态图输入法生成的控制信号交互模块;

counter模块为CRC处理模块;

详细信息见工程文件;

counter中的latch、send信号分别在latch_data_from_host和send_data_host状态时为1(由control提供);latch为1时进行对输入数据的处理,而在send为1时输出处理后的数据;

总的BDF与指导书上的参考图几乎相同;详见工程文件;

2、仿真验证与分析

0-150ns:wait_nrxf_low状态

150-250ns:nrxf为0,进入set_nrd_low状态,nrd为0;

250-350ns:latch_data_from_host状态,此时latch输出1,下一上升沿才对输入的A5进行CRC处理;

350-450:wait_ntxe_low状态

450-550:ntxe为0,进入set_wr_high状态,wr为1;

550-650ns:send_data_host状态,此时send输出1;

650ns:此时遇到上升沿且send为1,因此输出计算结果05;处理数据和发送数据都在第二个上升沿;

结果:为输入A5时经过CRC循环冗余验证后输出的数据为05,输出正确;

附录:工程截图

D级任务

顶层图(状态图输入法实现的控制信号交互部分与存储74273b部分组成):

C级任务使用提供的参考图;

B级任务

接受发送增强在一个电路中;

A级任务

顶层图:

usbconnection部件(由状态图输入法实现的控制信号交互部分和VHDL实现的计算部分组成):

控制信号交互部分:

4397

4397

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?