verilog bug记录 -算数运算符与移位运算符的优先级

最近项目中遇到一个问题,涉及到移位运算符和算数运算符的优先级考量

具体测试代码如下:

module left_move_test(

input clk,

input rst,

output [15 : 0] o_data

);

reg [15 : 0] r_dat_in = 16'h0f54;

reg [15 : 0] r_temp1 = 16'hff40;

reg [15 : 0] r_temp1_left_3;

reg [15 : 0] r_o_data;

reg [15 : 0] r_o_dat1;

always @(posedge clk ) begin

r_temp1_left_3 <= r_temp1 << 3;

end

always @(posedge clk ) begin

if(rst)

r_o_data <= 0;

else

r_o_data <= r_dat_in - r_temp1 << 3;

end

always @(posedge clk ) begin

if(rst)

r_o_dat1 <= 0;

else

r_o_dat1 <= r_dat_in - r_temp1_left_3;

end

endmodule

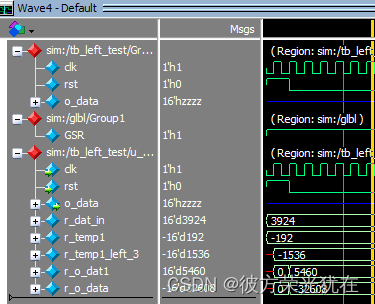

仿真结果如下图所示:

一开始写代码的时候我下意识以为是先进行的移位运算再进行的加减法,这个地方r_o_dat1和r_o_data的输出不一样感觉很奇怪,也是突然意识到运算优先级可能考虑错了

优先级如下:

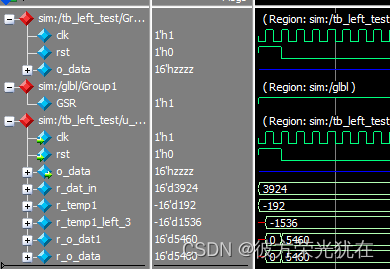

所以要先移位再加减的化还是得加个括号,代码和仿真结果如下:

module left_move_test(

input clk,

input rst,

output [15 : 0] o_data

);

reg [15 : 0] r_dat_in = 16'h0f54;

reg [15 : 0] r_temp1 = 16'hff40;

reg [15 : 0] r_temp1_left_3;

reg [15 : 0] r_o_data;

reg [15 : 0] r_o_dat1;

always @(posedge clk ) begin

r_temp1_left_3 <= r_temp1 << 3;

end

always @(posedge clk ) begin

if(rst)

r_o_data <= 0;

else

r_o_data <= r_dat_in - (r_temp1 << 3);

end

always @(posedge clk ) begin

if(rst)

r_o_dat1 <= 0;

else

r_o_dat1 <= r_dat_in - r_temp1_left_3;

end

endmodule

问题解决

6676

6676

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?