1、AHB总线简介

AHB总线是AMBA (Advanced Microcontroller Bus Architecture) 高级处理器总线架构协议簇中的一员。

AHB是针对高带宽、高性能系统所设计的总线,用于连接微处理器、高带宽片上RAM、高带宽外部存储器及各种带有AHB接口的控制器,还可以通过AHB-APB Bridge连接到APB总线系统。简单来说,AHB总线是构成传统MCU系统基本框架的核心。

2、AHB总线系统构成

AHB总线由4部分组成:

每个AHB都必须包含切仅有一个仲裁器和中央译码器。

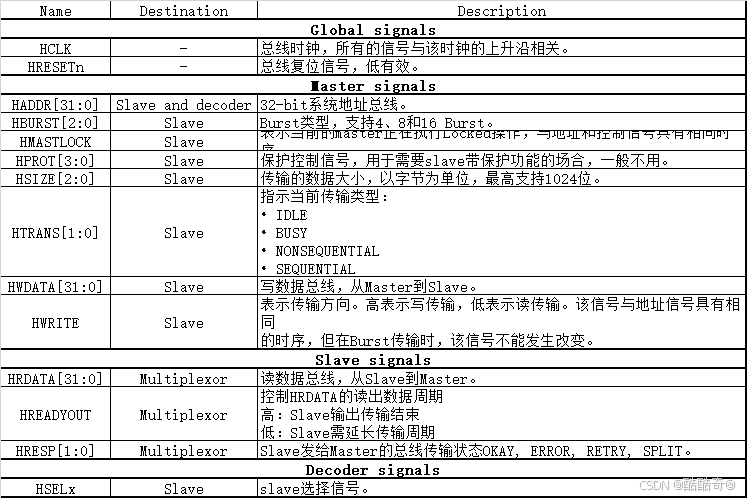

3、信号描述

4、AHB传输时序

AHB传输包含两个阶段,第一阶段为地址阶段,第二阶段为数据阶段。

地址阶段:一个HCLK周期。

数据阶段:一个或多个周期,由HREADY信号来控制完成传输所需时间。

HWRITE控制传输的数据方向:

HWRITE 为高时,表示是一个写传输, Maste r向写数据总线HWDATA[31:0]发送数据;

HWRITE 为低时,表示是一个读传输, Slave 向读数据总线HRDATA[31:0]发送数据。

零等待传输

零等待读传输

零等待写传输

具有一个等待的传输

具有一个等待的读传输

具有一个等待的写传输

多数据传输

传输状态HTRANS[1:0]

锁定传输

如果 Master 要求锁定访问,必须置位 HMASTLOCK 信号。该信号告知其它Slave 当前的传输序列不允许被打断。

典型的锁定传输应用是保持信号量的完整性,以确保处理器在 SWP 指令期间 Slave 不执行其它操作。

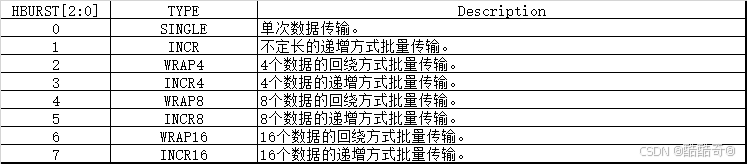

批量传输HBURST[2:0]

• 递增 Burst:访问连续位置,每个传输地址都是前一个地址的递增。

• 回绕 Burst:当地址到达边界时回绕,地址边界由个数和传输大小的乘积计算。

Burst 大小表示个数,而不是传输的字节数。要计算传输的数据量,需要将个数和每拍的数据量相乘(由 HSIZE[2:0]定义)。

Burst 突发不能超过1K的地址边界,所以主设备尽量不要发起要跨过地址边界的增量突发。

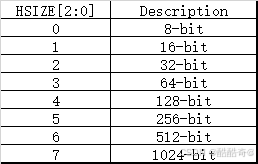

传输大小HSIZE[2:0]

保护控制HPROT[3:0]

提供总线访问的额外信息,主要用作某些级别的保护。除Slave有特殊需求,否则一般不使用。

传输响应

Master 开始一个传输, Slave 控制着传输过程, Master 无法取消已经开始的传输。Slave 必须提供一个响应来表示传输状态。该状态由 HRESP 信号提供。

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?