VL21 根据状态转移表实现时序电路

解法一:

用状态机做 但牛客网上只能用米利型状态机。我就随便写了

`timescale 1ns/1ns

module seq_circuit(

input A ,

input clk ,

input rst_n,

output wire Y

);

parameter IDLE = 2'd0;

parameter S0 = 2'd1;

parameter S1 = 2'd2;

parameter S2 = 2'd3;

reg [1:0] cur_state,nx_state;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cur_state <= IDLE;

else

cur_state <= nx_state;

end

always@(*)begin

case(cur_state)

IDLE:

if(A)

nx_state = S2;

else

nx_state = S0;

S0:

if(A)

nx_state = IDLE;

else

nx_state = S1;

endcase

S1:

if(A)

nx_state = S0;

else

nx_state = S2;

S2:

if(A)

nx_state = S1;

else

nx_state = IDLE;

default:

nx_state = IDLE;

end

assign Y = (cur_state == S2 && A == 1'b1) || (cur_state == S2 && A == 1'b0);

endmodule

(1)一段式:一个always块,既描述状态转移,又描述状态的输入输出,当前状态用寄存器输出;

(2)二段式:两个always块,时序逻辑与组合逻辑分开,一个always块采用同步时序描述状态转移;另一个

always块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出,当前状态用组合逻辑输出,可能出现

竞争冒险,产生毛刺,而且不利于约束,不利于综合器和布局布线器实现高性能的设计;

(当然,第二个always里的状态跳转和输出可以拆分用组合逻辑描述,也可能有三个always块,但是这并不

是三段式,和三段式的区别在于输出到底是组合逻辑还是时序逻辑)

(3)三段式:三个always块,一个always模块采用同步时序描述状态转移;一个always采用组合逻辑判断状

态转移条件,描述状态转移规律;第三个always块使用同步时序描述状态输出,寄存器输出。

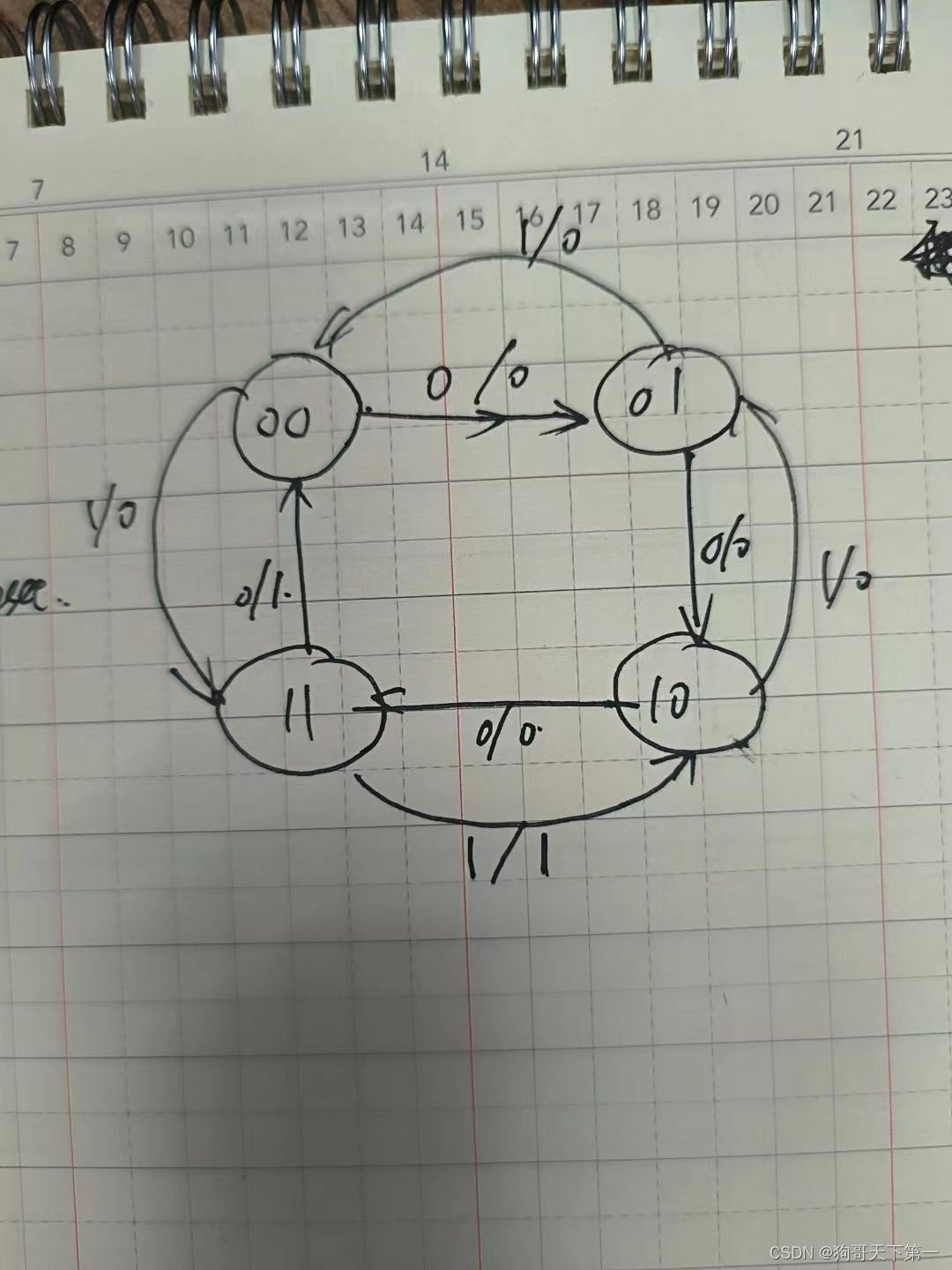

VL22 根据状态转移图实现时序电路

`timescale 1ns/1ns

module seq_circuit(

input C ,

input clk ,

input rst_n,

output wire Y

);

parameter IDLE = 2'd0;

parameter S0 = 2'd1;

parameter S1 = 2'd2;

parameter S2 = 2'd3;

reg [1:0] cur_state,nx_state;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cur_state <= IDLE;

else

cur_state <= nx_state;

end

always@(*)begin

case(cur_state)

IDLE:

if(C)

nx_state = S1;

else

nx_state = IDLE;

S0:

if(C)

nx_state = S0;

else

nx_state = S2;

S1:

if(C)

nx_state = S1;

else

nx_state = IDLE;

S2:

if(C)

nx_state = S1;

else

nx_state = S2;

default:

nx_state = IDLE;

endcase

end

assign Y = (cur_state == S2 ) || (cur_state == S1 && C == 1'b1) ;

endmodule

VL23 ROM的简单实现

这题好怪 不想做

VL24 边沿检测

也是毛病特别多的一个题

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output rise,

output down

);

reg [1:0] dff;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

dff <= 'd0;

else

dff <= {dff[0],a};

end

assign rise = ( !dff[1] ) && dff[0];

assign down = ( !dff[0] ) && dff[1];

endmodule

598

598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?