世界上主流的集成电路都是在硅片上制作的,而其中用的最多的技术就是CMOS

为了理解集成电路,我们必须先了解集成电路所用的原料的性质

1. 硅原子的结构

每个硅原子最外层有四个电子,我们称他们为价电子(Valence electrons)

高纯度的硅拥有近乎完美的晶体结构(crystalline structure),是用来制作微处理器的绝佳材料,这并不便宜,但已经是性价比最高的选择了

晶体结构,也可以称为晶体,意味着原子之间形成的化学键在空间中周期性排列

在晶体硅中,每个原子与其它四个原子形成共价键(covalent band)

根据原子力学,原子为围绕其原子核的电子提供了离散能级(discrete energy level)

电子会优先占据低能级,每个能级能够承载的电子是有限的,比如最低级1s最多就只能承受两个电子

对于单个硅原子,它的能级是离散的,一群孤立不互相影响的原子的能级也是离散的

那么问题来了,如果我们将众多硅原子连在一起,会发生什么事呢?

2. 能带的形成

在一个硅晶体中,大概有

1

0

23

10^{23}

1023个硅原子在他们之间形成了化学键,因此,他们的离散能级结合形成了能带(energy band)

注意,能级上承载的是电子,因此能带上也都是电子,整个能带带负电,能级越高代表携带的电子能量越大,但在最底层有一些空穴是带正电的

能量的参数包括其在半导体中的位置和电子的动量,平时我们不是太需要关注动量,除非发生光电效应

一个电子的动能为

p

=

h

k

/

(

2

π

)

p=hk/(2\pi)

p=hk/(2π),其中h是普朗克常数

在工程领域,我们常用能带及其所在的位置作为绘图时的横坐标

2.1 能带图

要理解半导体的电子性质,我们必须要理解能带图(energy band diagrams)

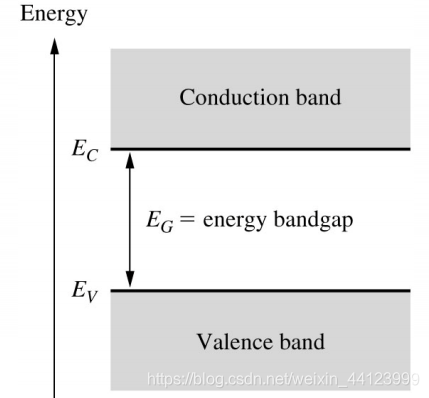

一个传统的能带图包含顶端的导带(conduction band)和底端的价带(valence band),在他们中间存在带隙(band gap),图示如下:

上图横坐标代表的是位置

导带中大多数位置都是空缺的,只有一部分被电子占据,如果温度高于0K,导带中的电子可以在空缺位置间自由移动

价带中大多数位置都是填充的,只有一部分是空缺的,这些空缺被称为空穴(holes),当电子在其中移动时,看起来就像是空穴在移动

我们一般不关心导带中的空穴和价带中的电子

导带和价带中间的带隙不含能级,我们一般称它为半导体的能带隙(energy band gap),通常带隙中也不含电子

室温下,硅的带隙大概为1.1eV

在温度为绝对零度0K时,所有的电子都将去到能级最低的地方,这就意味着价带中充满了电子,而导带中不含电子

当温度升高,T>0K时,价带中的一些电子会获得能量从而突破带隙进入导带

在温度为室温300K时,导带中会有一些电子,而价带中会有一些空穴

整个过程中电子的数量是守恒的

半导体的性质可以说就是由导体中空穴和电子的浓度决定的,我们称单位体积的电子为n,单位体积的空穴为p,控制p和n我们就控制了半导体的电学特性

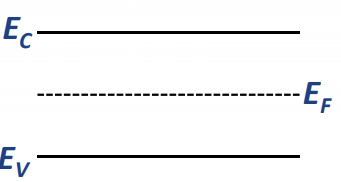

在画能带图时,我们可以将其简化为几条线,如图:

上方的水平线代表的是导带的最低端,下方的水平线代表的是价带的最顶端,中间代表的是费米能级(Fermi level)

2.2 费米能级

费米能级的位置与电子与空穴的数量有关,这句话从何而来呢?

首先,在能带图中,越低的能级就越有可能被电子占据,其中被电子占据的概率为二分之一的能级就被称为费米能级,至于为什么这个能级可以出现在不允许电子占据的带隙中,则要牵扯到量子态,此处不多赘述,只要知道费米能级并非是一个实际的能级,而是某种象征。

总之,知道费米能级处电子占据的概率为二分之一,那么一个地方的电子越多,能带被占据的概率就越大,费米能级就会越靠近导带,相对的,如果一个地方的电子越少,空穴越多,就代表能带被占据的概率越小,费米能级就会越靠近价带

3. 掺杂

通过外部引入一些电子或者空穴,也就是掺杂(doping),我们可以控制n和p

这些引入的原子通常为磷原子或硼原子,引入的杂质被称为掺杂物(dopant)

选用的原子建立的能级通常靠近

E

V

E_V

EV或

E

C

E_C

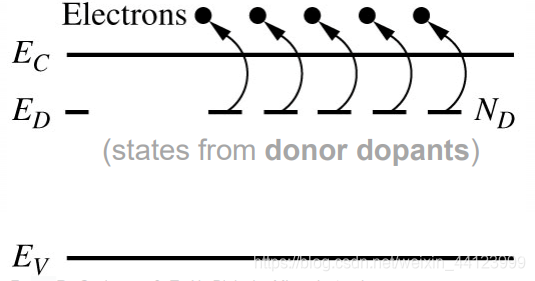

EC,在硅中,掺入磷会建立靠近

E

C

E_C

EC的能级,如图:

其中

E

D

E_D

ED就是磷引入的能级,

因为

E

D

E_D

ED里

E

C

E_C

EC很近,由磷的能级承载的电子可以得到热能并升入导带,这会使得导带中的电子增多,从而使n增大

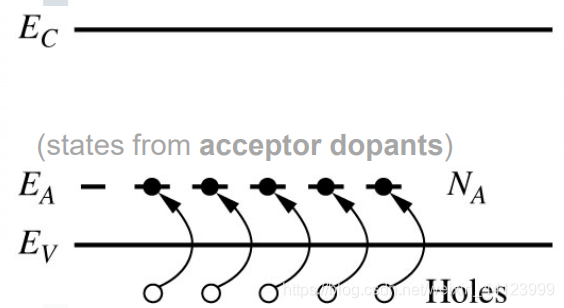

同样的,掺入硼可以引入靠近价带的能级,如图:

因此,价带中的电子会升到

E

A

E_A

EA中,从而增加价带中的空穴,增大p

没有掺杂的半导体称为本征半导体(intrisic semiconductor),其中导带中的电子和价带中的空穴数量相等:

n

=

p

=

n

i

n=p=n_i

n=p=ni

其中

n

i

n_i

ni是本征半导体的导带电子浓度

对于硅,室温的

n

i

=

1

0

10

c

m

−

3

n_i=10^{10}cm^{-3}

ni=1010cm−3

如果掺入浓度为

N

D

N_D

ND的donor dopant,则硅中的

n

≈

N

D

n\approx N_D

n≈ND

如果掺入浓度为

N

A

N_A

NA的acceptor dopant,则硅中的

p

≈

N

A

p\approx N_A

p≈NA

一般

N

D

,

N

A

N_D, N_A

ND,NA的值远大于

n

i

n_i

ni

3.1 费米能级的位置

前面提到过,费米能级的位置与电子和空穴的数量有关

当掺入 donor dopant 的时候,导带中拥有较多的电子,

E

F

E_F

EF靠近

E

C

E_C

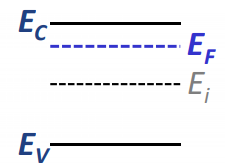

EC,如图:

此时的硅被称为n型半导体(n-type semiconductor)

当掺入 acceptor dopant 的时候,价带中拥有较多的空穴,

E

F

E_F

EF靠近

E

V

E_V

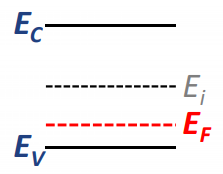

EV,如图:

此时的硅被称为p型半导体(p-type semiconductor)

但无论什么时候,半导体中电子浓度和空穴浓度的乘积都为本征半导体导带电子浓度的平方:

n

p

=

n

i

2

np={n_i}^2

np=ni2

这也意味着n和p的乘积是一个常数,这个常数是由半导体材料的性质和温度决定的,如果n或p其中一个增加,另一个必定减小

4. 漂移电流与扩散电流

在半导体中有两种情况可能造成电子和空穴在半导体中移动,他们分别是漂移(drift)与扩散(diffusion)

4.1 漂移电流

在电场的作用下,电子和空穴会向相反的方向移动,并形成方向相同的漂移电流(drift current)

接着我们可以得到下面两个公式:

V

d

n

=

−

μ

n

E

V

d

p

=

μ

p

E

V_{dn}=-\mu_nE\ \ \ \ \ \ \ \ V_{dp}=\mu_pE

Vdn=−μnE Vdp=μpE

其中:

V

d

n

V_{dn}

Vdn是电子的漂移速度(drift velocity)

V

d

p

V_{dp}

Vdp是空穴的漂移速度

μ

n

\mu_n

μn是电子的漂移率

μ

p

\mu_p

μp是空穴的漂移率

E

E

E是电场强度

然后我们可以得到电导率

σ

\sigma

σ为:

σ

=

e

n

μ

n

+

e

p

μ

p

\sigma=en\mu_n+ep\mu_p

σ=enμn+epμp

其中e是电荷电量(

1.60

×

1

0

−

19

C

1.60 \times 10^{-19}C

1.60×10−19C)

n是自由电子的数量

p是自由空穴的数量

最后,我们可以得到漂移电流为:

J

=

σ

E

J=\sigma E

J=σE

4.2 扩散电流

根据动能定理,粒子会从高浓度的地方向低浓度的地方扩散,这种现象被称为扩散

当浓度梯度不为0时,扩散就会发生,产生的扩散电流(diffusion current)为:

J

n

=

e

D

n

d

n

d

x

J_n=eD_n\frac{dn}{dx}

Jn=eDndxdn

J

p

=

−

e

D

p

d

p

d

x

J_p=-eD_p\frac{dp}{dx}

Jp=−eDpdxdp

其中

d

n

/

d

x

,

d

p

/

d

x

dn/dx, dp/dx

dn/dx,dp/dx 就是浓度梯度

D

n

,

D

p

D_n, D_p

Dn,Dp被称为扩散系数(diffusion coefficients),他们与各自的载流子偏移率

μ

n

,

μ

p

\mu_n, \mu_p

μn,μp 有关

5547

5547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?