可以说,所有的CMOS集成电路的基础都是MOS晶体管,而MOS晶体管则是由两个基本的半导体结构组成的,即p-n结(p-n junction)和MOS电容(MOS capacitor),本篇文章将主要总结pn结,并不会涉及太多MOS电容的知识

1. 物理结构

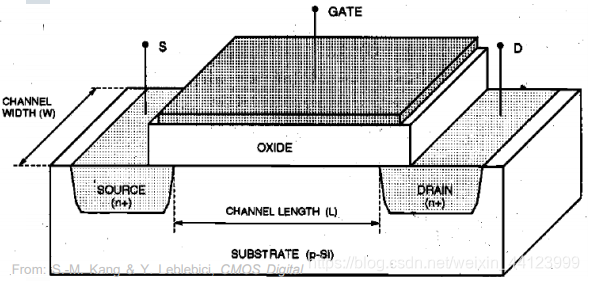

在nMOS中,pn结的分布如图所示:

可以看到source 和 drain 充当的是pn结中的n,中间的基底充当p

正常情况下,这里的pn结都是反向偏置的,并不会导电,但pn结却可以直接影响晶体管的表现,比如pn结的寄生电容(parasitic capacitance)可以影响MOS电路的开关速度

为了方便表达,我们通常把pn结表现为两个区域:

其中p中掺有浓度为

N

a

N_a

Na受主杂质(硼等)

n中掺有浓度为

N

d

N_d

Nd的施主杂质(磷或砷等)

根据上一篇文章中的内容,我们明白p和n是两个被不同杂质掺入的半导体,其中p端的载流子,也就是空穴浓度在室温下为

p

p

≈

N

a

p_p\approx N_a

pp≈Na

n端的载流子,电子浓度在室温下为

n

n

≈

N

d

n_n\approx N_d

nn≈Nd

同样的,每一端的本征载流子浓度

n

i

n_i

ni 都是常数,所以我们可以得出:

2. 扩散

我们知道如果半导体内存在浓度梯度差,就会出现扩散

pn结的两端掺入了相反功能的杂质,一个提供电子,一个提供空穴,那么理所当然p和n之间就会有浓度差

之后,这个浓度差会让空穴从p向n移动,让电子从n向p移动

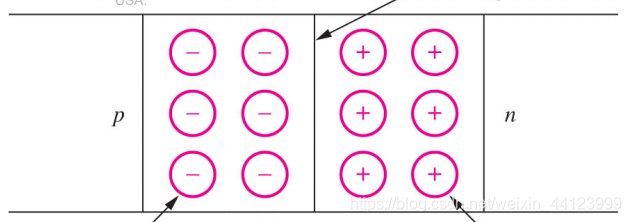

少部分移动的空穴停留在了n端的表面,电子停留在了p端的表面,而大部分的电子和空穴仍待在原处,如图所示:

这些离子形成了一个从n端指向p端的电场,从而造成电子和空穴的漂移

3. 漂移

我们知道,电场会催生出漂移电流,pn结中由扩散的离子形成的电场也一样会在pn结中催生漂移电流,他们的漂移速度如下:

V

d

n

=

−

μ

n

E

V_{dn}=-\mu_nE

Vdn=−μnE

V

d

p

=

μ

p

E

V_{dp}=\mu_pE

Vdp=μpE

可以看到电子漂移的方向与电场相反

由于漂移的方向和扩散的方向相反,电子和空穴的运动达到了平衡

我们称中间这一团由p中的电子和n中的空穴组成的区域为耗尽区(depletion region)或空间电荷区(space-charge region)

4. 静电分析

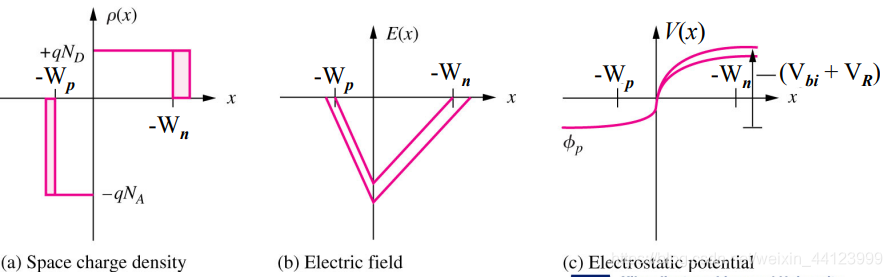

pn结每个位置对应的电荷密度,电场强度,电势如图所示:

其中最后一幅图中的电势也可以理解为势垒

当我们给pn结施加一个反向偏置的电压

V

R

V_R

VR,我们可以得到变化的图形为:

可以看到空间电荷密度拓宽了,反向偏置的电压将更多

电场下移了,电场强度增加

静电势的末端上移了,静电势增加???

在施加反向电压时,p端接电源负极,n端接电源正极

此时电源会试图从p端获取空穴,从n端获取电子,因此,p中的空穴会被向左拉,n中的电子会被向右拉,从而使p和n的区域缩减,相应的,耗尽区就会变大

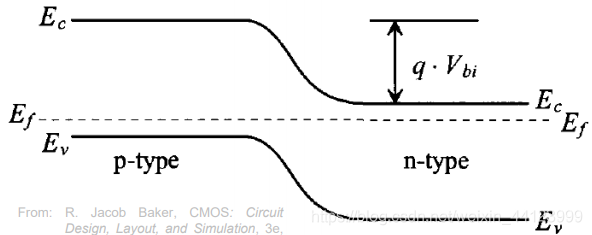

通过绘制pn结的能带图,我们可以看到均衡后两边的费米能级统一在一条水平线上,如图:

相连区域的费米能级统一,是因为我们使用费米能级作为参考系

5. 关键参数

接下来我们看pn结中的一些关键参数,这都是我们在分析pn结时需要考虑的:

- 内部电势 ϕ b i \phi_{bi} ϕbi,也叫内部电压 V b i V_{bi} Vbi

- 耗尽区宽度 W 0 W_0 W0,包含p端耗尽区宽度 W p W_p Wp和n端耗尽区宽度 W n W_n Wn

- 耗尽区电容 C d C_d Cd,也叫junction capacitance C j C_j Cj

其中 V b i V_{bi} Vbi 可以用来计算 W 0 W_0 W0,而 W 0 W_0 W0则可以决定 C d C_d Cd

5.1 内部电压计算

V

b

i

V_{bi}

Vbi 的计算方式如下:

V

b

i

=

V

T

l

n

(

N

A

N

D

n

i

2

)

V_{bi}=V_Tln(\frac{N_AN_D}{{n_i}^2})

Vbi=VTln(ni2NAND)

其中

V

T

V_T

VT是热电压

一般来说,掺杂浓度

N

D

N_D

ND和

N

A

N_A

NA大概在

1

0

16

c

m

−

3

10^{16}cm^{-3}

1016cm−3

室温下

V

b

i

V_{bi}

Vbi此时约为

0.7

V

0.7V

0.7V

5.2 耗尽区宽度计算

零偏置下的耗尽区宽度为:

W

0

=

W

p

+

W

n

=

2

ϵ

S

i

(

N

A

+

N

D

)

V

b

i

e

N

A

N

D

W_0=W_p+W_n=\sqrt{\frac{2\epsilon_{Si}(N_A+N_D)V_{bi}}{eN_AN_D}}

W0=Wp+Wn=eNAND2ϵSi(NA+ND)Vbi

W

p

=

N

D

N

A

+

N

D

W

0

W_p=\frac{N_D}{N_A+N_D}W_0

Wp=NA+NDNDW0

W

n

=

N

A

N

A

+

N

D

W

0

W_n=\frac{N_A}{N_A+N_D}W_0

Wn=NA+NDNAW0

其中

ϵ

S

i

\epsilon_{Si}

ϵSi是硅的介电常数

在反向偏置下,耗尽区的宽度随反向偏置电压

V

R

V_R

VR增大而增大,此时的耗尽区宽度为:

W

0

=

W

p

+

W

n

=

2

ϵ

S

i

(

N

A

+

N

D

)

(

V

b

i

+

V

R

)

e

N

A

N

D

W_0=W_p+W_n=\sqrt{\frac{2\epsilon_{Si}(N_A+N_D)(V_{bi}+V_R)}{eN_AN_D}}

W0=Wp+Wn=eNAND2ϵSi(NA+ND)(Vbi+VR)

正向偏置时,耗尽区的宽度随正向偏置电压

V

F

V_F

VF增大而减小,耗尽区宽度为:

W

0

=

W

p

+

W

n

=

2

ϵ

S

i

(

N

A

+

N

D

)

(

V

b

i

−

V

F

)

e

N

A

N

D

W_0=W_p+W_n=\sqrt{\frac{2\epsilon_{Si}(N_A+N_D)(V_{bi}-V_F)}{eN_AN_D}}

W0=Wp+Wn=eNAND2ϵSi(NA+ND)(Vbi−VF)

6. pn结电容

之前我们谈论过,在扩散作用后,pn结内会形成一个耗尽区,耗尽区两边是不会移动的离子,这就形成了一个平行板电容器,我们称它为耗尽区电容(depletion capacitance)

电容器的电容为:

C

=

ϵ

A

d

→

C

j

=

ϵ

S

i

A

j

W

0

C=\frac{\epsilon A}{d}\rightarrow C_{j}=\frac{\epsilon_{Si}A_j}{W_0}

C=dϵA→Cj=W0ϵSiAj

然而和一般平行板电容器不同的是,pn结中的电容器与通过pn结的电压有关

在反向偏置时,耗尽区电容为:

C

j

=

C

j

0

1

+

V

R

V

b

i

C_j=\frac{C_{j0}}{\sqrt{1+\frac{V_R}{V_{bi}}}}

Cj=1+VbiVRCj0

其中

C

j

0

C_{j0}

Cj0是零偏置时的耗尽区电容

在正向偏置时,耗尽区电容为:

C

j

=

C

j

0

(

1

−

V

D

V

b

i

)

m

C_j=\frac{C_{j0}}{(1-\frac{V_D}{V_{bi}})^m}

Cj=(1−VbiVD)mCj0

这个m是一个常数,取决于pn结的种类

若为突变结(abrupt junction)则为1/2

若为线性结(linear junction)则为1/3

6.1 侧壁电容

零偏置时的电容

C

j

0

C_{j0}

Cj0实际上包含两部分,一部分由面积决定,一部分由周长决定

由周长决定的电容被称为侧壁电容(sidewall capacitance)

完整的零偏置电容表达式为:

C

j

0

=

C

j

0

a

×

(

面

积

)

+

C

j

0

s

w

×

(

周

长

)

C_{j0}=C_{j0a}\times(面积)+C_{j0sw}\times(周长)

Cj0=Cj0a×(面积)+Cj0sw×(周长)

7. pn结制图

了解pn结之后,我们需要知道如何在layout中表现它,这个我们之后再提

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?