文章目录

视频链接

视频目录

1 - 早期的计算 - Early Computing

2 - 电子计算 - Electronic Computing

3 - 布尔逻辑与逻辑电路 - Boolean Logic & Logic Gates

4 - 二进制 - Representing Numbers and Letters with Binary

5 - 算术逻辑单元 - How Computers Calculate - the ALU

6 - 寄存器 & 内存 - Registers and RAM

7 - 中央处理器 - The Central Processing Unit(CPU)

8 - 指令和程序 - Instructions & Programs

9 - 高级 CPU 设计 - Advanced CPU Designs

10 - 编程史话 - Early Programming

11 - 编程语言 - The First Programming Languages

12 - 编程原理:语句和函数 - Programming Basics: Statements & Functions

13 - 算法初步 - Intro to Algorithms

14 - 数据结构 - Data Structures

15 - 阿兰·图灵 - Alan Turing

16 - 软件工程 - Software Engineering

17 - 集成电路、摩尔定律 - Integrated Circuits & Moore’s Law

18 - 操作系统 - Operating Systems

19 - 内存 & 储存介质 - Memory & Storage

20 - 文件系统 - Files & File Systems

21 - 压缩 - Compression

22 - 命令行界面 - Keyboards & Command Line Interfaces

23 - 屏幕 & 2D 图形显示 - Screens & 2D Graphics

24 - 冷战和消费主义 - The Cold War and Consumerism

25 - 个人计算机革命 - The Personal Computer Revolution

26 - 图形用户界面 - Graphical User Interfaces

27 - 3D 图形 - 3D Graphics

28 - 计算机网络 - Computer Networks

29 - 互联网 - The Internet

30 - 万维网 - The World Wide Web

31 - 网络安全 - Cybersecurity

32 - 黑客与攻击 - Hackers & Cyber Attacks

33 - 加密 - Cryptography

34 - 机器学习与人工智能 - Machine Learning & Artificial Intelligence

35 - 计算机视觉 - Computer Vision

36 - 自然语言处理 - Natural Language Processing

37 - 机器人 - Robots

38 - 计算机中的心理学 - Psychology of Computing

39 - 教育型科技 - Educational Technology

40 - (完结) 奇点,天网,计算机的未来 - The Singularity, Skynet, and the Future of Computing

多图预警

笔记

第5集·算术逻辑单元 - How Computers Calculate - the ALU

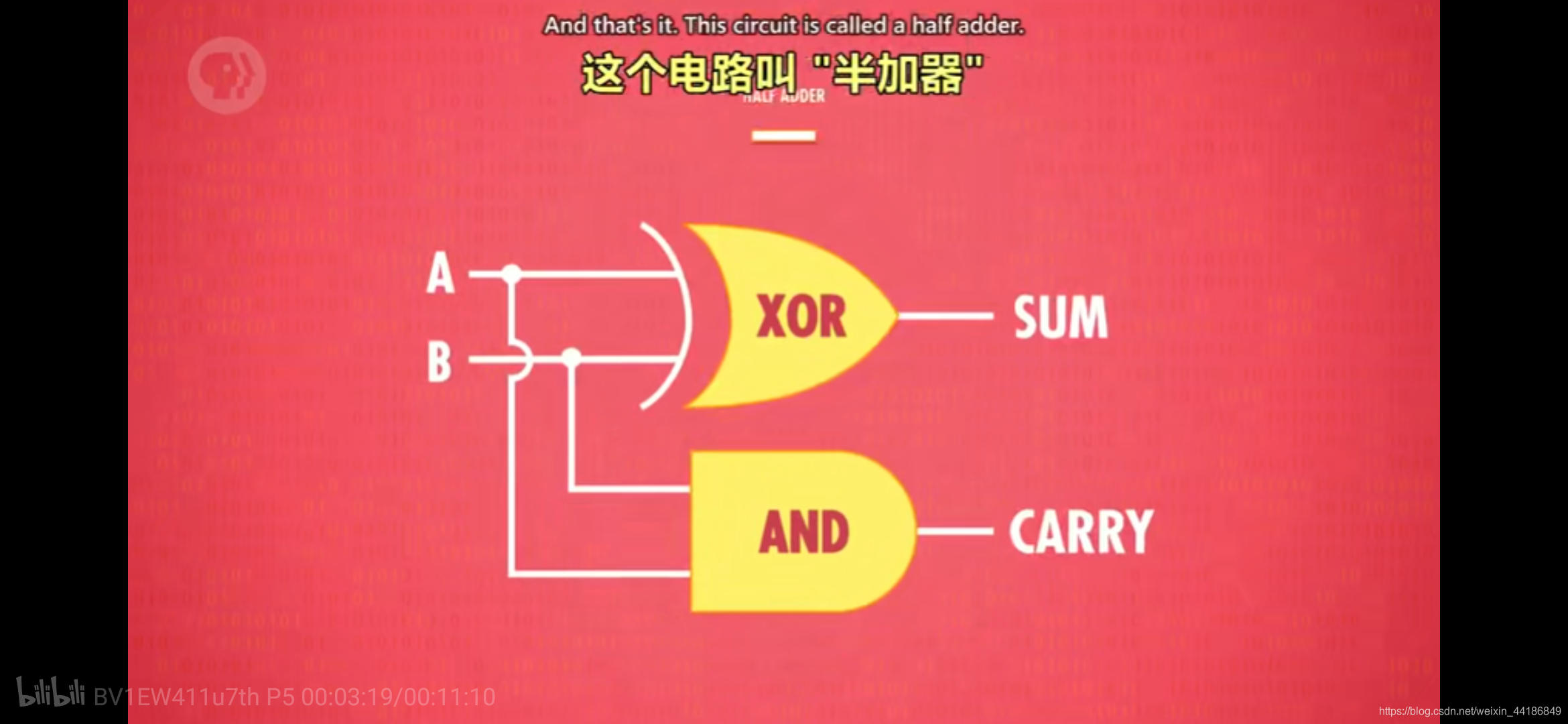

半加器

为啥会制造半加器这种玩意儿,因为我们要进行计算,计算二进制中 两个1bit数的计算,比如A+B, 那怎么表示结果呢? 你可以试试, A+B会出现哪些情况, 0+0=0、0+1=1、1+0=1、1+1=10,就只有这四种情况,0为 false ,1为true。那么怎么表示 A+B,用前面学到的逻辑门去比对输入与输出的结果,发现只有XOR异或门能匹配20位的结果,但遗憾的是,当A+B是 1+1=10的情况下,0可以正确表示,但是进位的1,无法表示,还少一位。这个进位有什么特点?同为1才输出1,其它输出0,对不对?什么门与之匹配,与门嘛,所以上图的半加器就诞生了 。这个半加器对于 两个1bit的数相加的结果是完全正确的,为啥起名叫半加器,我想是因为这个门虽然能够正确显示两个数的相加结果但是对于 输出侧的利用是不充分的,因为 输出侧只会是00,01,10,但是11是无法达成的,故此叫半加器吧。

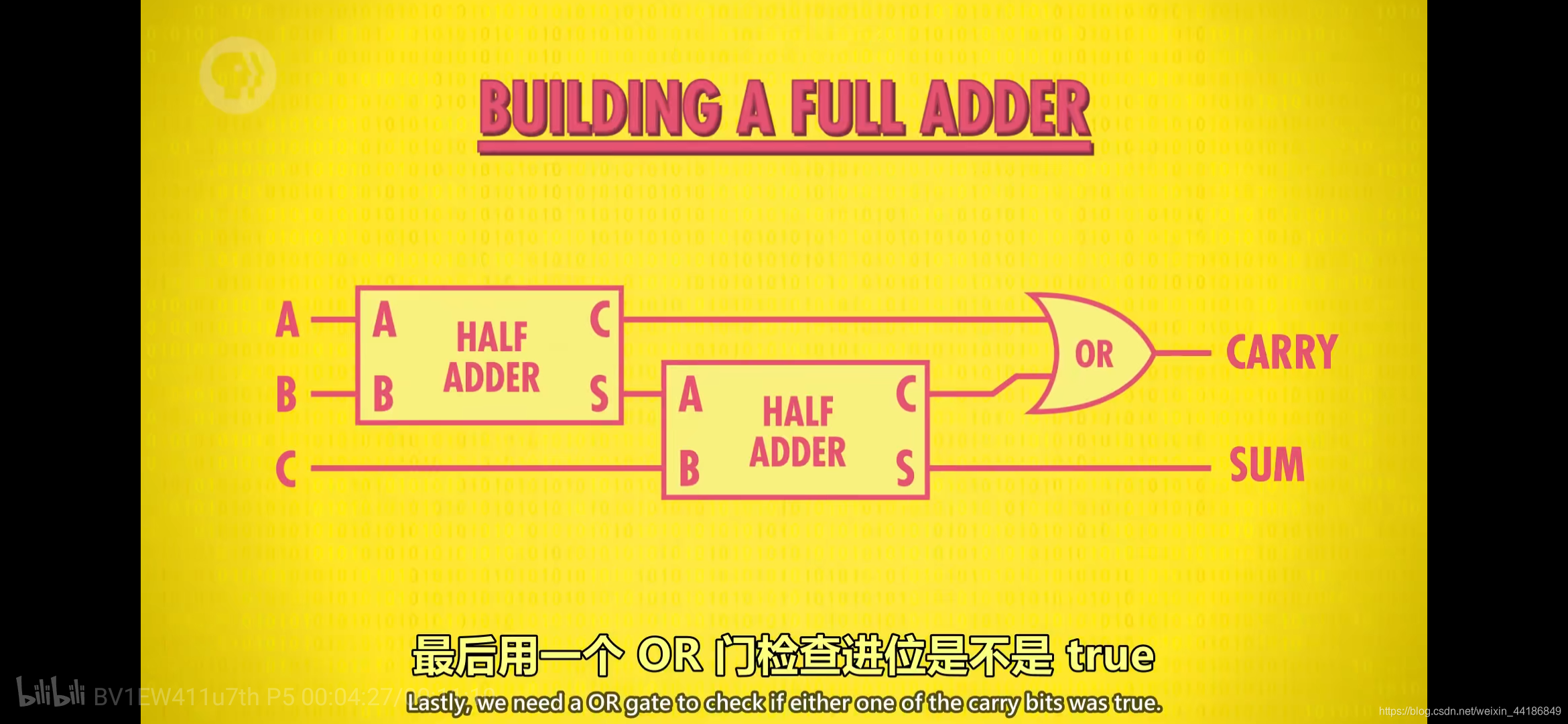

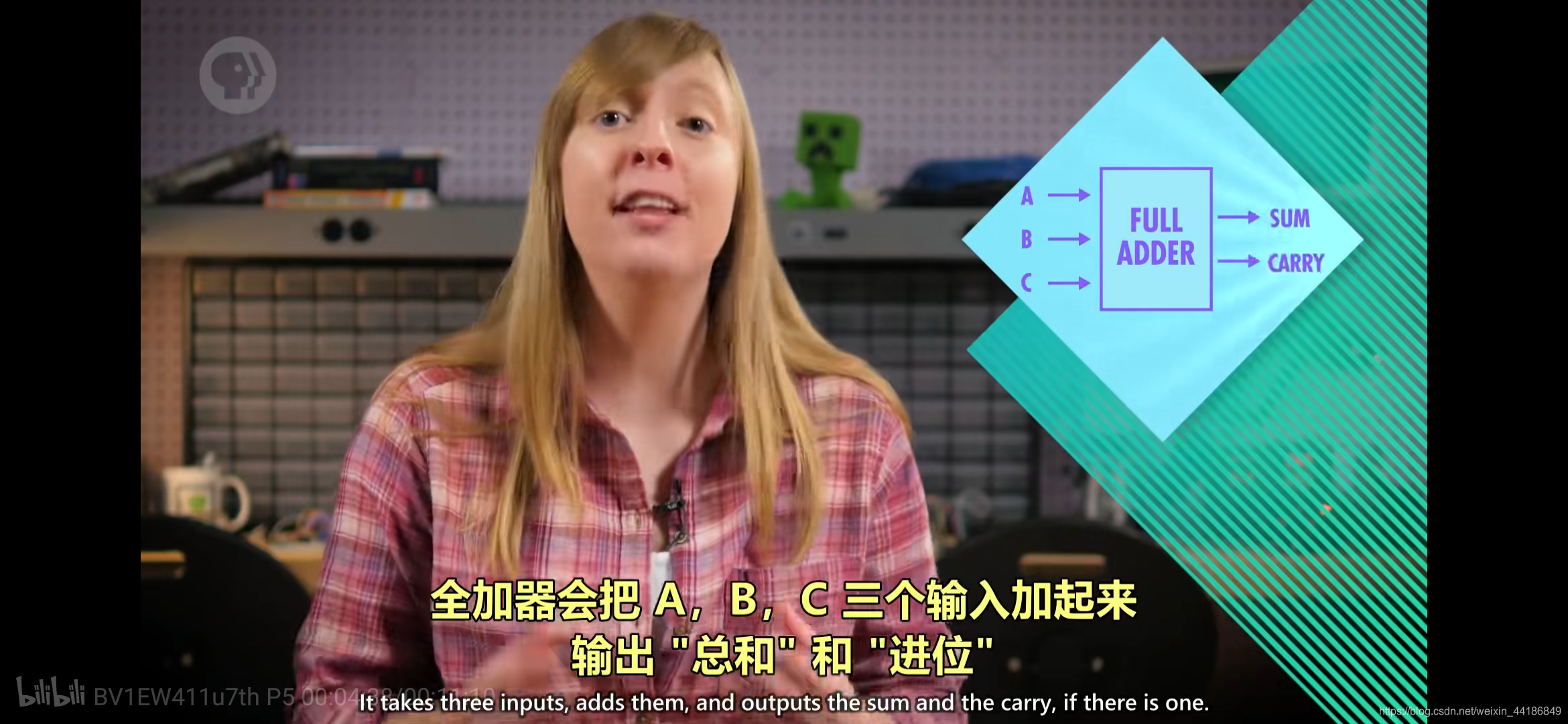

全加器

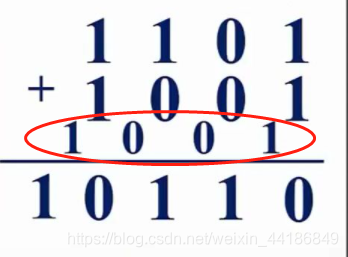

我们模拟下 1101+1001的情况, 可以看出会有进位的产生, 进位和选原先的两个数一起相加计算, 这样最多会有三个数相加的情况, 而半加器只有两个数相加,所以我们需要一个能处理三个数相加的全加器。全加器什么特点呢?其实就是模拟上述算式的方式, 三个数ABC先计算两个数AB的结果, 然后把结果的sum位与C相加得到的sum位就是最终的sum位, 那 进位呢? AB相加的进位X , 然后 第一次结果与C相加的进位Y, 这两个进位相或就是最终的进位。为啥?其实 两个进位XY分别是0+0,1+0,0+1的情况都好理解,XY相或的结果就是0,1,1这个是完全符合的,但是1+1的结果不应该是10吗?这样会溢出,不会的,因为进位上不会有1+1的情况,你可以反推,如果A+B的进位X是1,说明A B都要为1, A+B的sum位就为0,0+C,无论C是0还是1都不会出现进位Y为1的情况。其实你也可以列一张表,就是ABC分别为0和1的情况下的sum位和进位的表,只有222=8种情况,你会发现,全加器的结果就是完全符合的。

浮点数表示

一个32bit的浮点数,通常会用最顶位表示符号,接下来的8位表示指数位,剩下的23位表示实数位。

比如该图 value=(-1)0 X2(136-127)X1.222=625.9

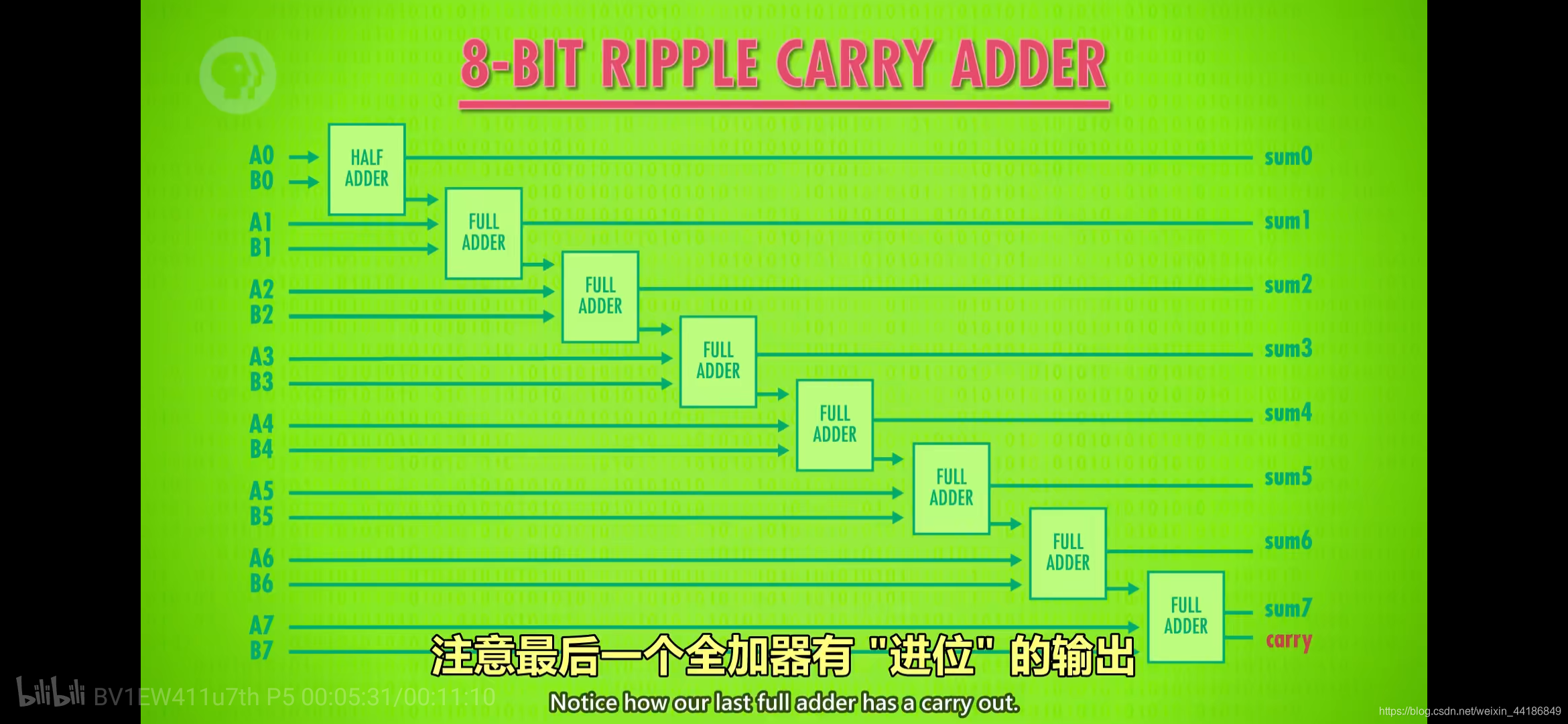

行波进位加法器

如图,构成了一个8bit数相加的加法器,输入 A和B (为8bit位宽),可计算出结果,C0 位相加有进位, 进位和 C1位的两个数A1 和B1相加 就是三个数相加使用全加器,依次排布,构成了一个8bit位宽的加法器,最终结果 可以看到,会有一个最终进位carry, 这个会反应溢出的情况。前面的sum0-7 已经有8bit了。

ALU算术逻辑单元

ALU算术逻辑单元就是由像上述的行波进位加法器构成的,比如做加法,INPUTA INPUTB分别为A数和B数,输入,OUTPUT就会输出相应结果, 还有一个carry位 连接到OVERFLOW, 做溢出标识符,如果有溢出为true说明 相加的结果太大已经溢出了。除了加法还能减法,其原理和 行波进位加法器类似,以及做两数是否相等的比较,如该图的右下角的逻辑相等器,将A和B相减后的结果输入到逻辑相等器,凡事有一个数不为0 ,输出就会为false,即不想等,只有全部都为 0时,输出才为true,即相等。ALU就是集成了这些逻辑运算和必要标识的一个统一体unit,通过这个ALU可以进行一些常规的算数操作和判断。

第6集·寄存器 & 内存 - Registers and RAM

锁存器

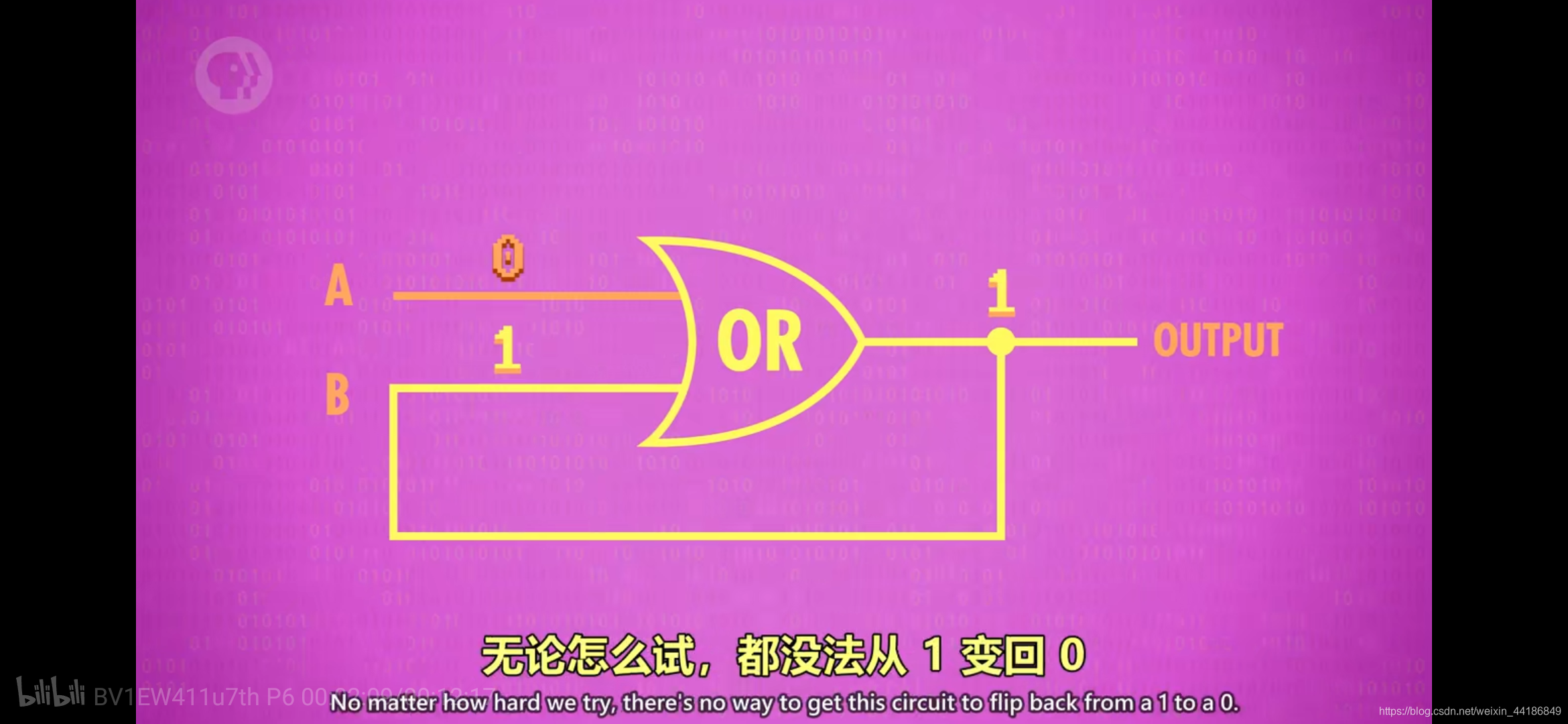

我们如何维持一个bit的信息保持不变, 这幅图的构建就是能保持1即true的信息不变,当起初AB都为0,A输入1,则OUTPUT也为1,立马会回到B,同置为1,再经过OR门,OUTPUT还是为1,这样1就被保存了起来, 这时候无论A输入0还是1,OUTPUT都不会改变了。

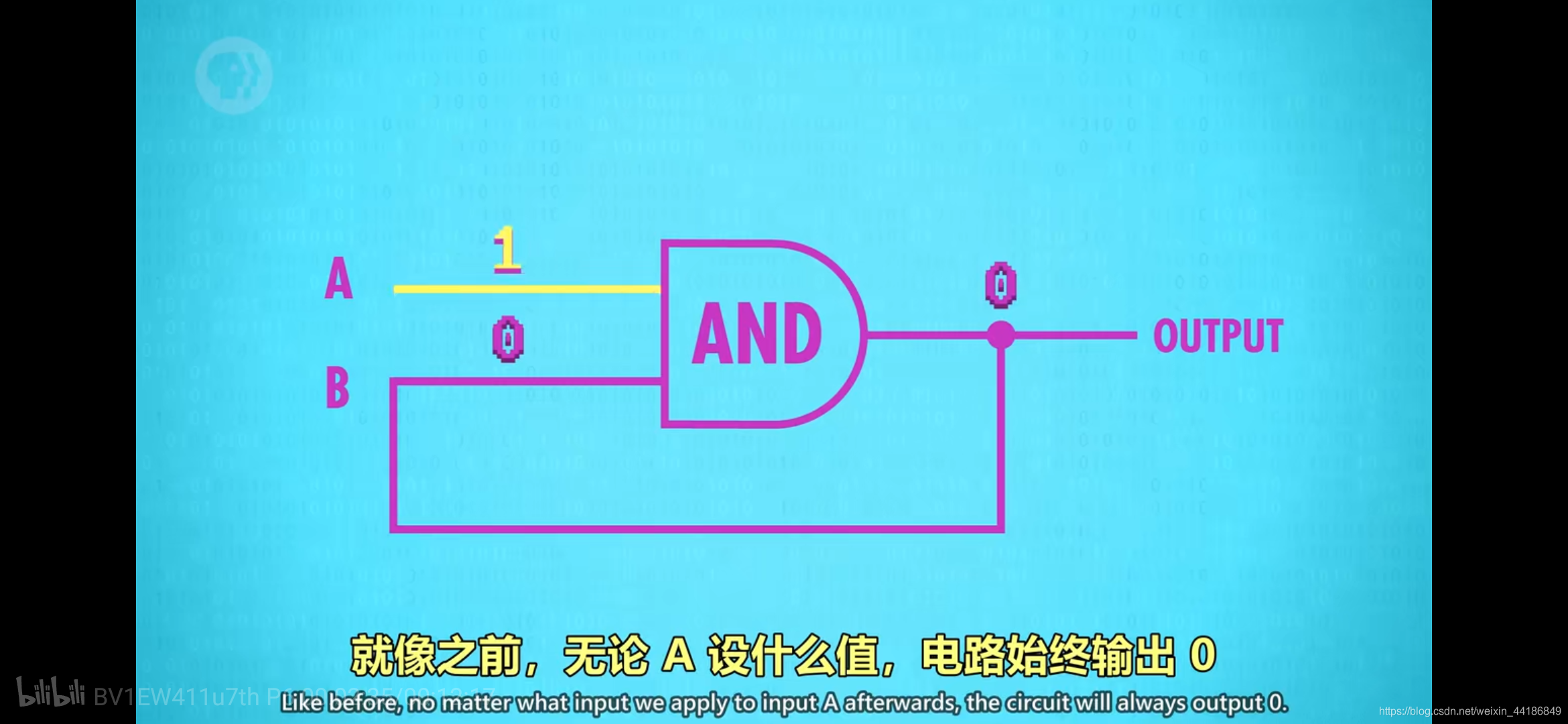

我们如何维持一个bit的信息保持不变, 这幅图的构建就是能保持0即tfalse的信息不变,无论A输入0还是1,OUTPUT都不会改变了。

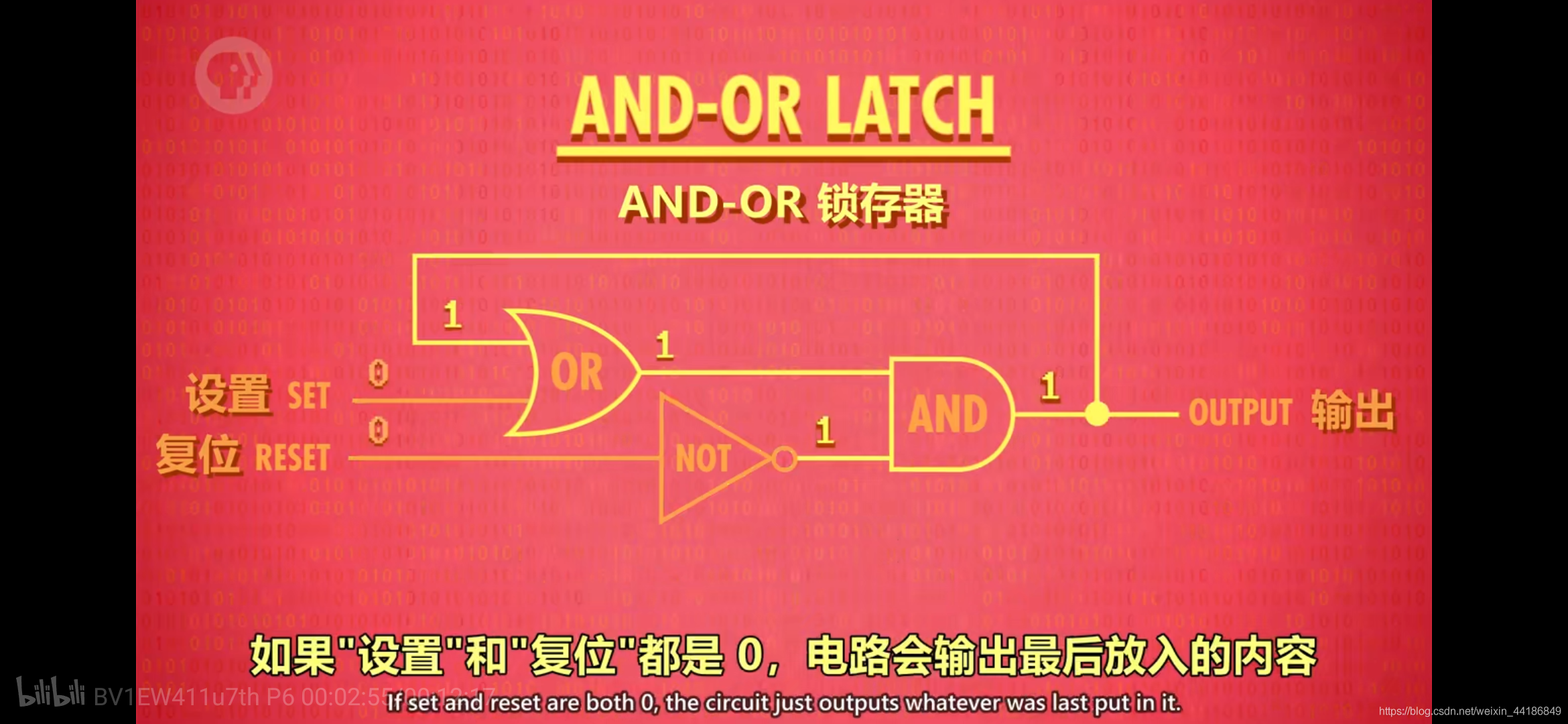

将上面的结构组合一下,设置和复位都为0时,电路最后输入的是啥就为锁住啥,当复位打开为1,设置什么0还是1都不管用,OUTPUT都是0。复位为0时,会锁住1,但是如果为0,SET给1的话,就会OUTPUT为1,这个时候SET就不管用了。要想管用得把复位调到1。

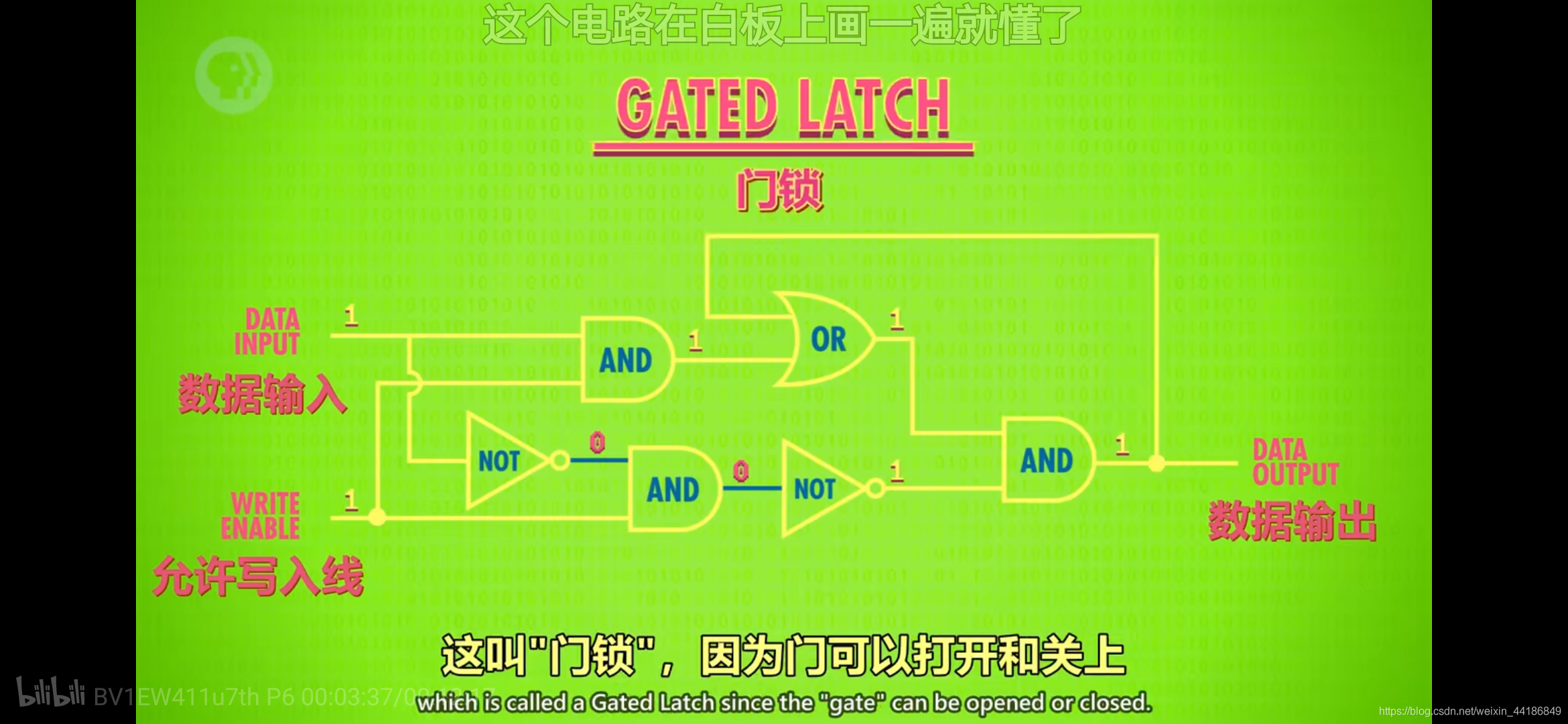

门锁

这个电路你试试就知道,允许写入线的开关,决定数据输入是否有效。只是这个电路是怎么想出来的?咋们的目的事要做一个可以存储数据的电路,输入一个值,能保存下来,先从简单的1bit开始。输入了一个数值,电路能保存这个数值。由上面自连接的或门和与门,可以看出,想要锁定一个值,还是容易的,但是锁住之后就不能修改了,然后你就会想到扩充,输入一根控制先,让它受控制。锁存器就出来了。锁存器的操作不是我们常规容易理解的。然后门锁就出来了。这样一步一步的制造出来的一个电路,当然这里面一定是包含了大量的非常熟悉的对逻辑门的理解,这种电路的设计就是经验和创造力了的体现。

我再来整理一下这个门锁的运行流程。为了书写方便,数据输入端我设为A,允许写入端我设为B,先从图上的内容说起,我们将B端置为1,A端直连的与门结果就为A端输出的结果,再经过或门。我们就输入1好了,好,我们现在来看看下面这个与门,由于经过一个非门,变成0,再过与门,一定为0,再经过非门又变成1,所以最后一个与门的下面的输入为1,上面的输入也为1,最终的输出就为1。现在我们把A端输入变成0,依旧推演一下,上面的与门结果必定为0,下面的与门由A端的0经过非门变成1后结果为1再经过非门变成0,最终的结果就为0。现在把B端的输入变为0即,不允许写入,我们刚刚将0锁存了, 现在把A端变为1试试能不能改变结果,B端为0,会控制上下连个与门的结果都为0,无论你A端输入什么,所以下面的0再经过非门就变成1,再到最后的与门,这个与门输出最终结果为0还是1,就取决于上面一根输入线了,上面的输入线是或门而来,或门的下面一根线我们已经确定一定为0,那或门的结果就取决于已经锁存的数值,锁存的是什么,就依旧是什么,所以实现了不允许写入。

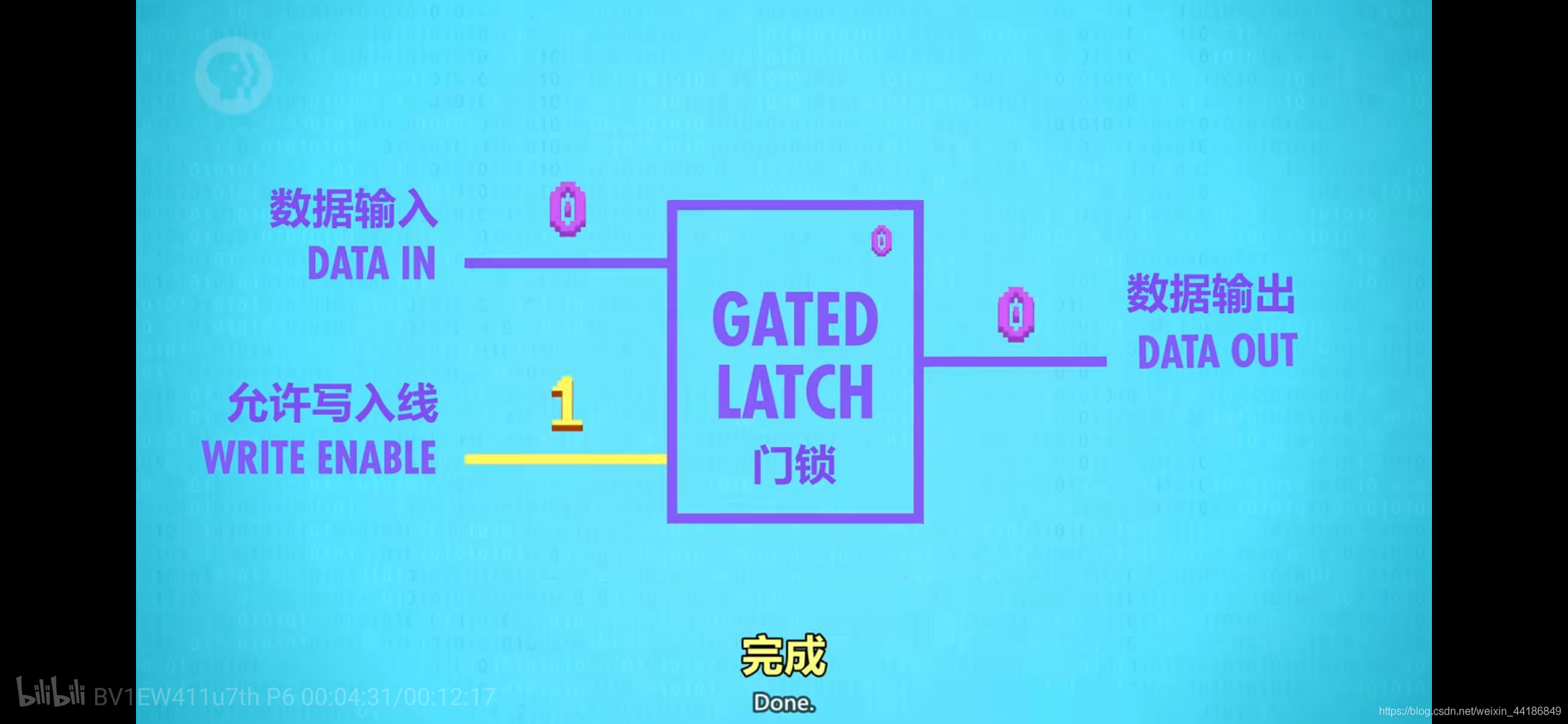

理解了上面的电路的逻辑原理,就能实现,我们想要的结果,不用在关心里面的逻辑。我们把它抽象,一根数据输入线,一根允许写入线,一根数据输出线。只有当允许数据写入线打开时,门锁才受数据输入的影响,否则门锁会保持原先锁住的内容。

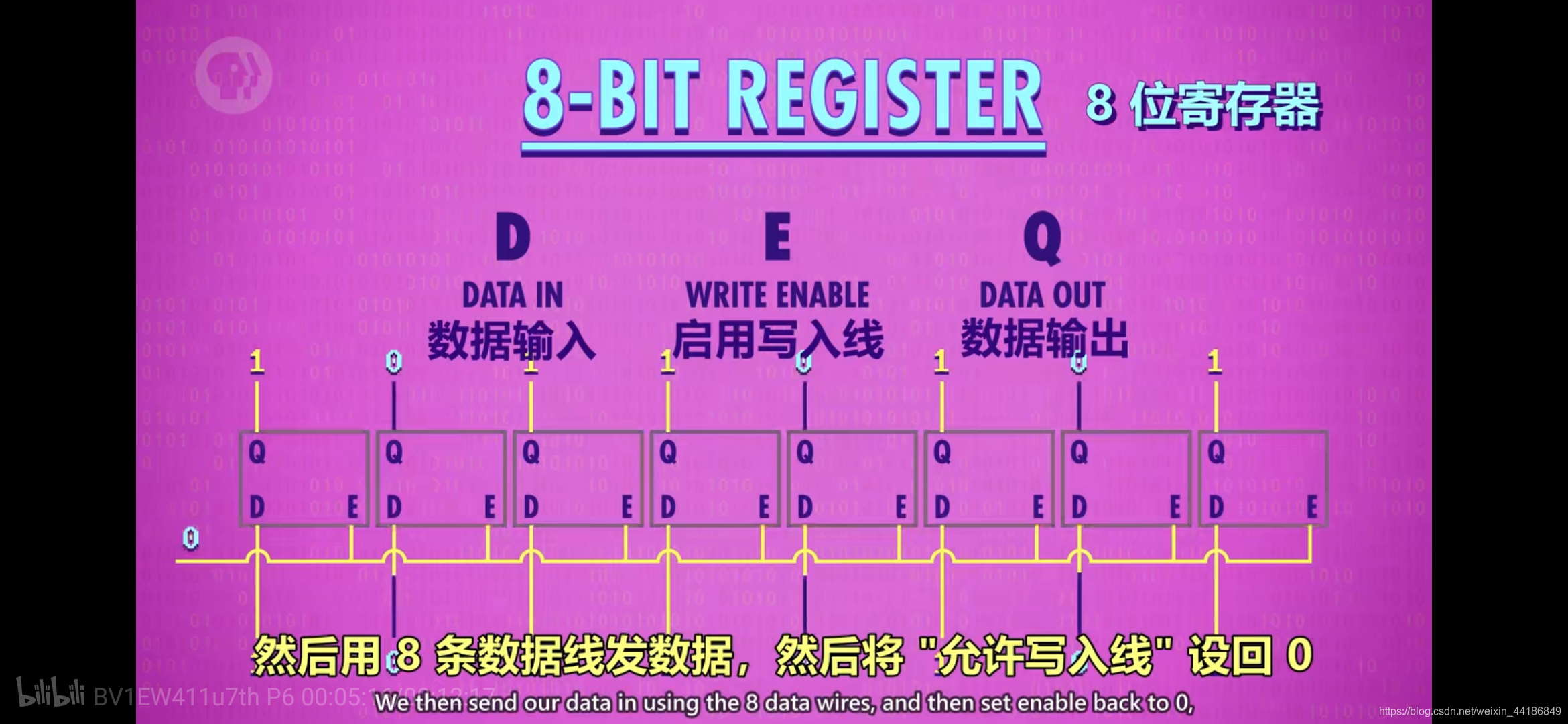

寄存器

一个门锁做好了,很显然它的数据量太小了,只有1bit,将其扩充,并排摆放8个,用 1根线控制8个门锁的允许写入线,8根数据线发数据,8根数据线输出数据。当我们打开控制线时,输入可存放到这个寄存器当控制线关闭,输入就不能影响寄存器了,寄存器保留之前的数据。其实这里我们要理一下思绪,就是我们默认的经验是一个数据输入,然后统一存储,比如这个寄存器,不是有8bit的位置,那我输入一个数据10010011,不就能存下这个值吗,确实可以,但是它不方面,实际上,这一排的门锁都只会存一个数据的特定位置的1bit的信息,因为这一系列的内容的索引是不同地址。下面的门锁矩阵个就能比较直观的体现这一点。

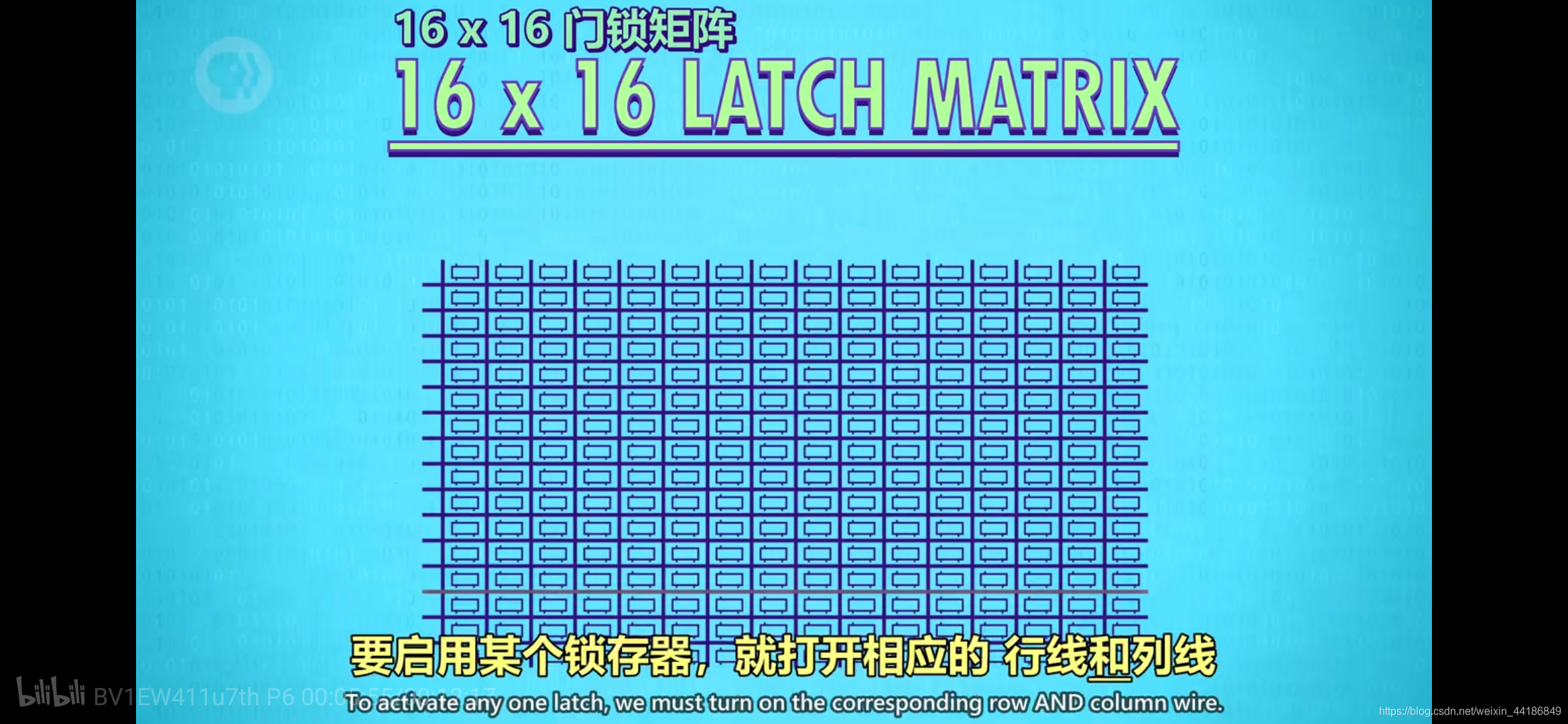

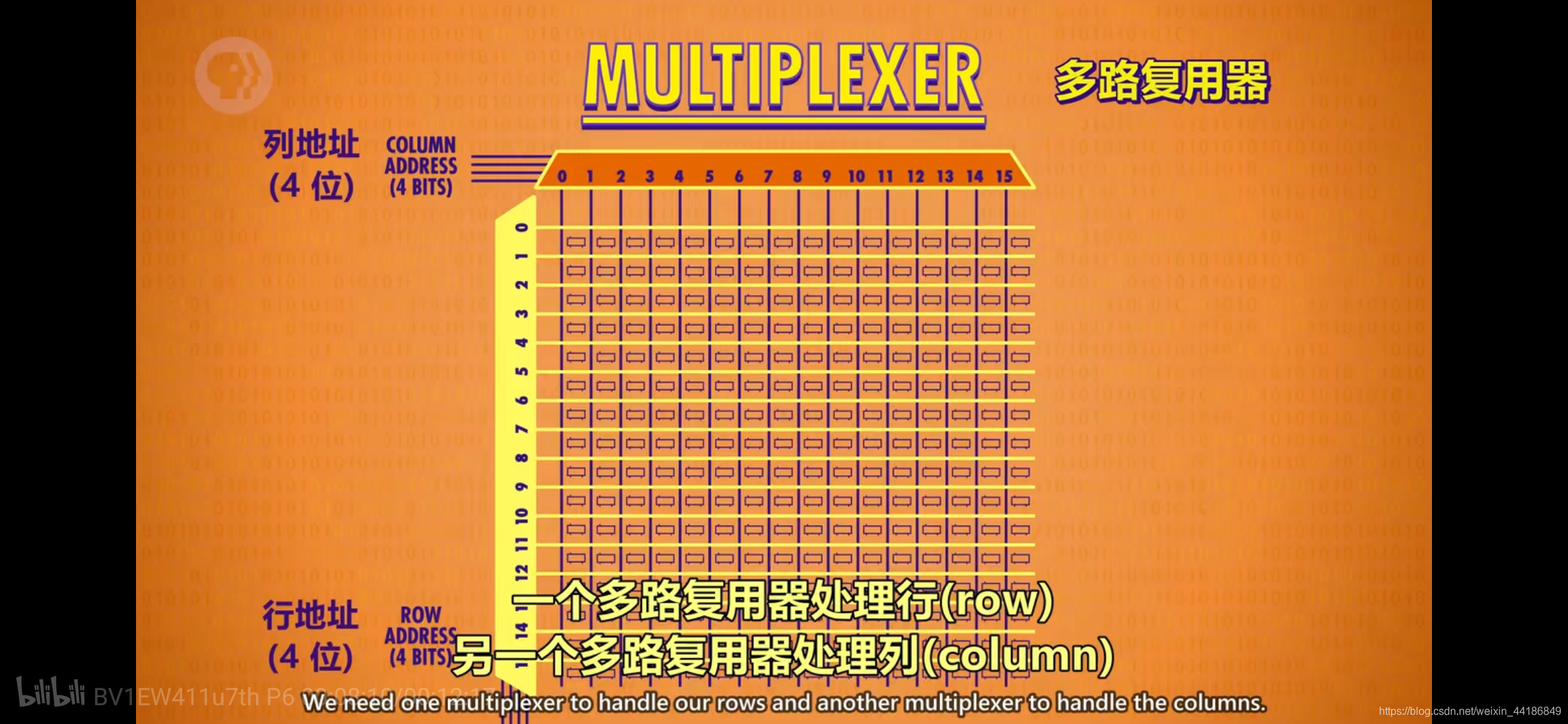

多路复用器

在工业上为了节省成本,我们又要扩大内存,如果还按照上面的并排摆放门锁,那就会产生很多不必要的开销。比如做一个256bit的寄存器,那就要256+256+1=513根线。我们换一种思路,将他们排布成矩阵,16*16,每一个门锁都对应独一的位置,由行号和列号决定。

将这个1616根线,分别接入多路复用器,一个4bit的位置信息就能确定走哪一根线,比如0010,那就是走2号线,行和列都一样的原理,那么一个8bit的行列信息就能控制1616矩阵的某一块门锁了。这个矩阵中的门锁其实对应的是地址。所以这个矩阵就只需要16+16+1+1=34,节省了不是一点点。

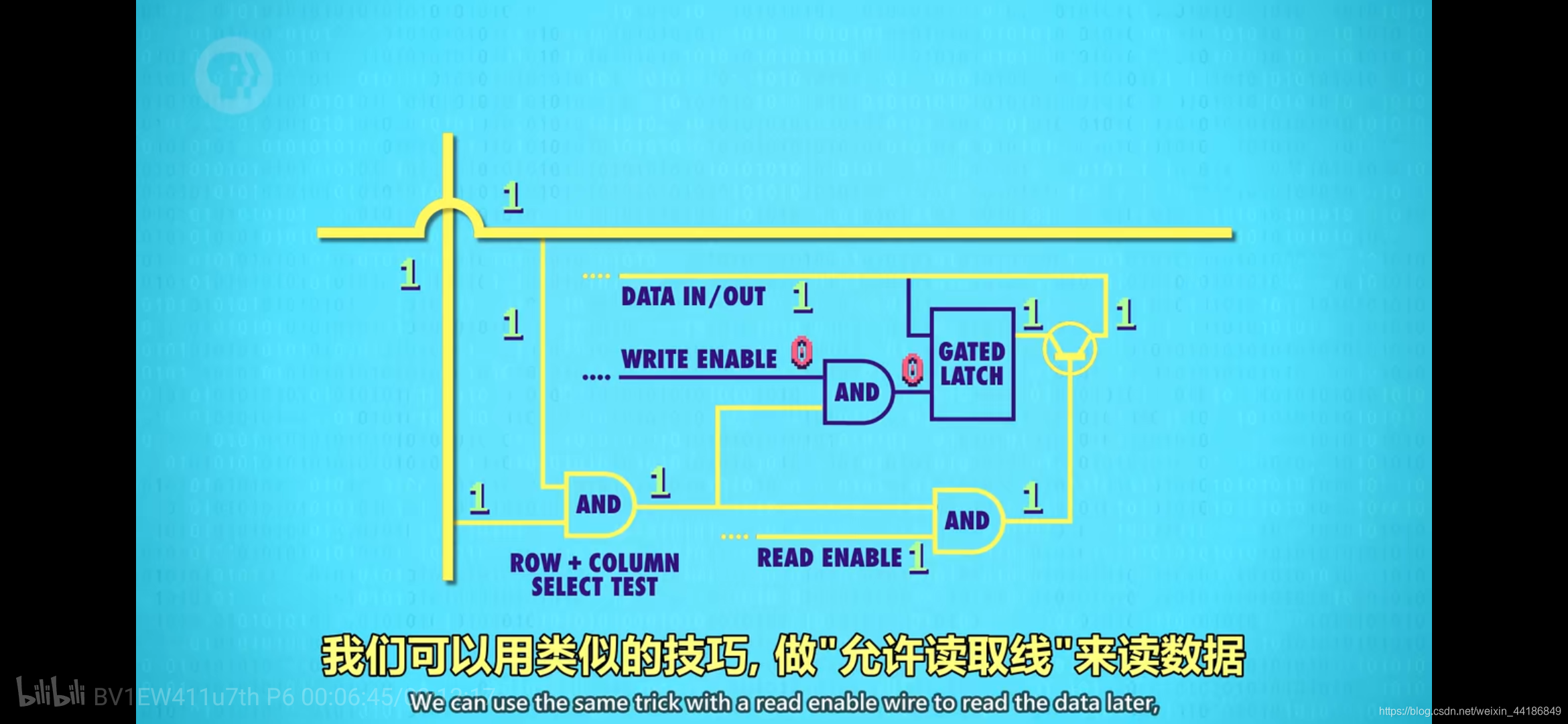

上述门锁放大,可以看出,只有当门锁的行和列都通的时候,这个门锁才可能会生效,比如这时候让可以读取,和行列得到与门再与,那个二极管才会通DATAOUT的线才会有门锁出来的结果,这样才能读取到数据。

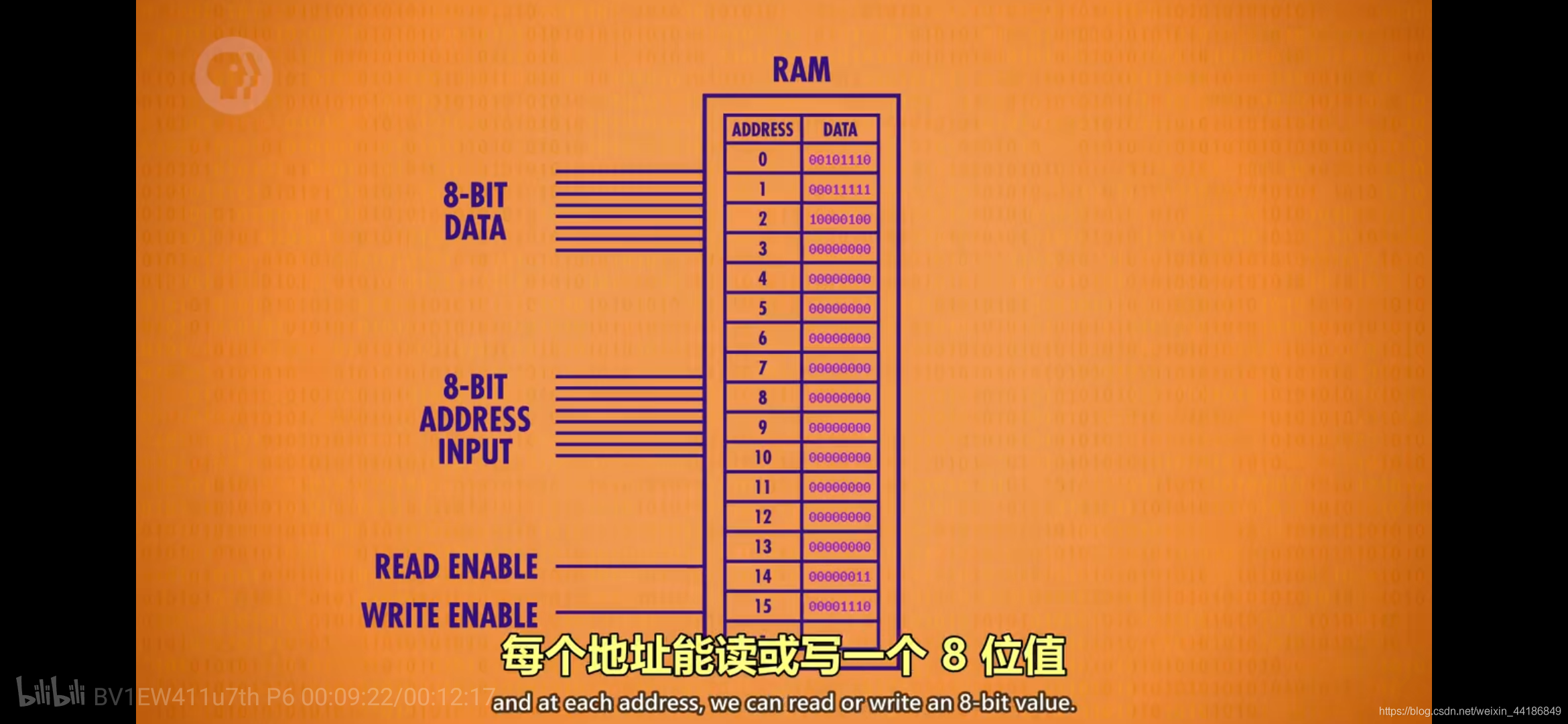

RAM

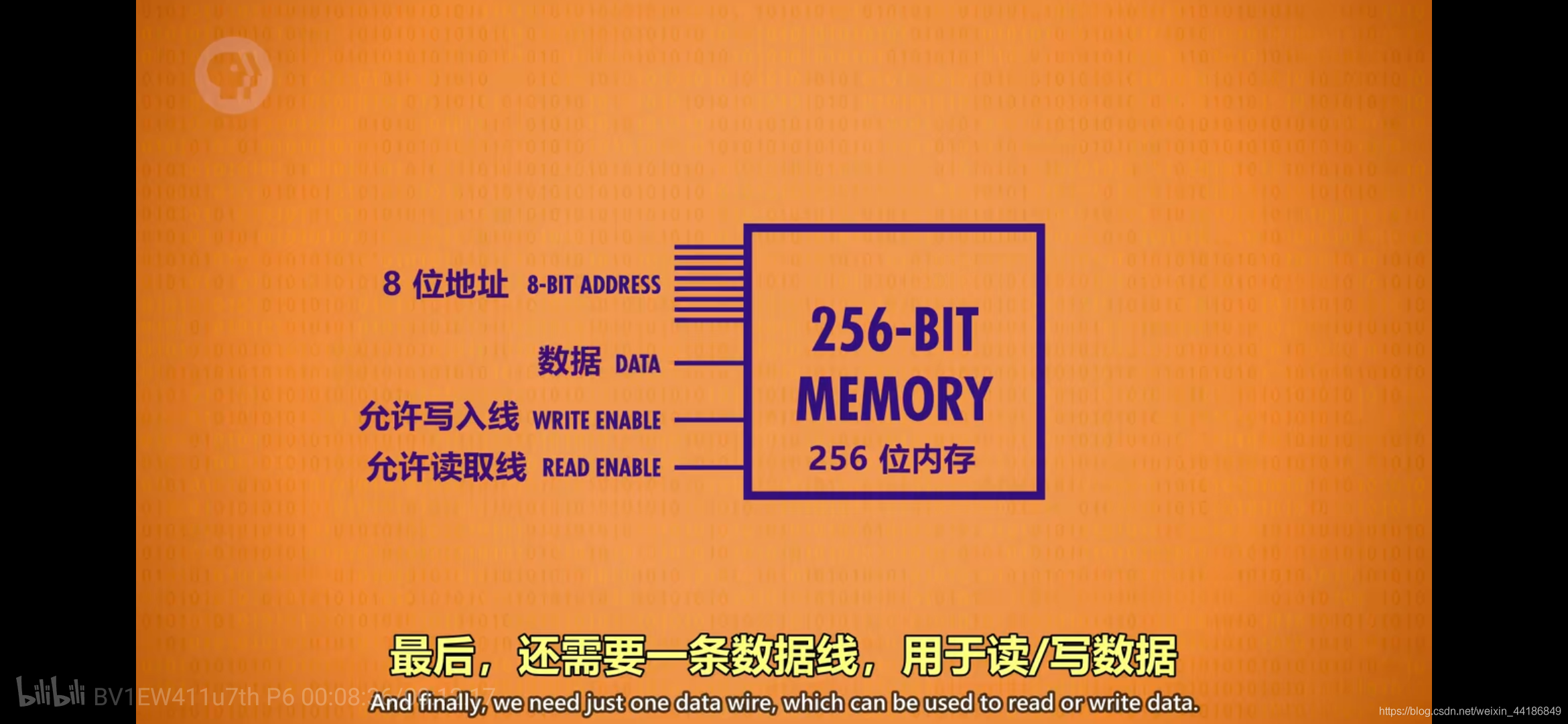

我们知道了内部原理,再进一步抽象,256bit的内存,由一个8bit的地址线,其实地址线就看出内存的大小了,28=256,然后一根数据线,一根允许写入线,一根允许读取线。非常简单,不过一个这样的内存也没什么用,它只能在指定的位置存1bit信息。

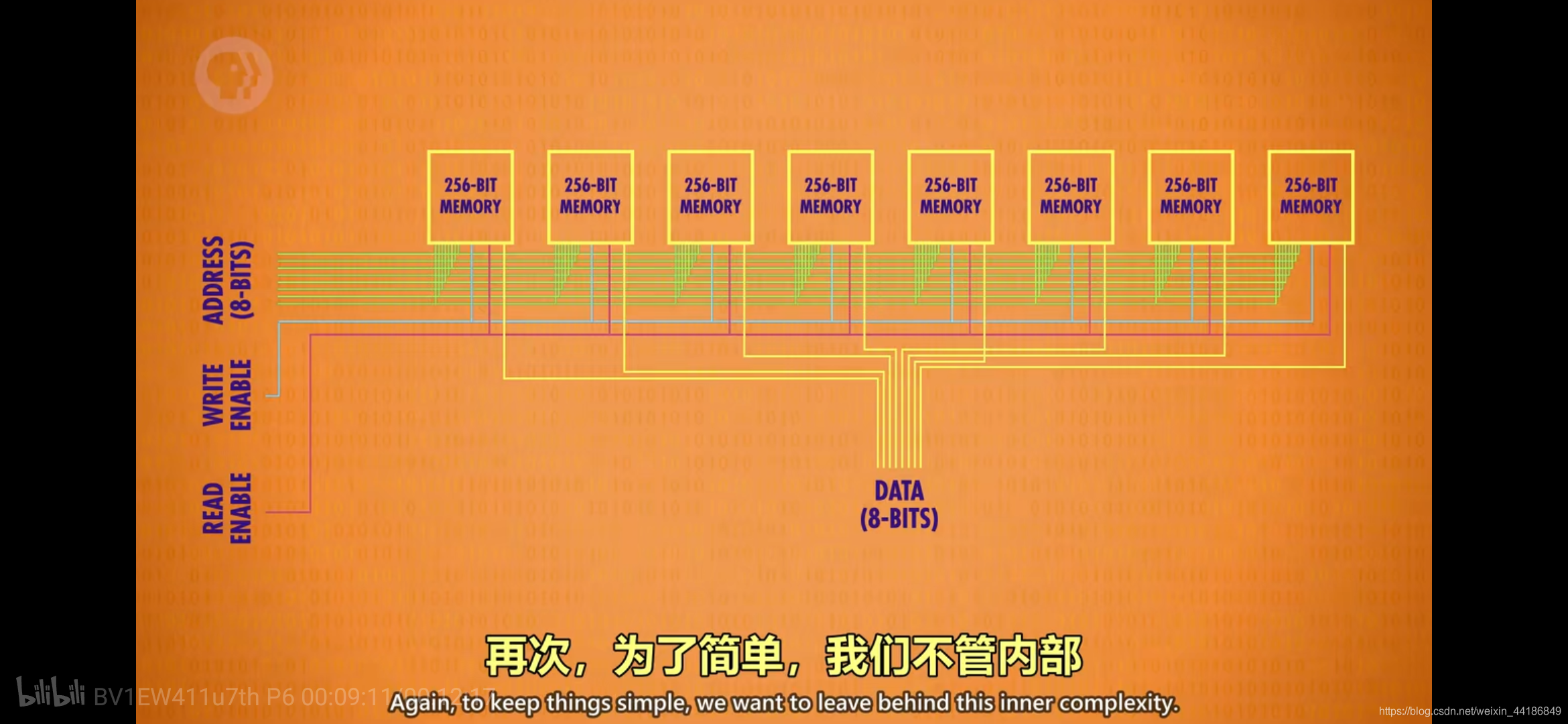

我们再把内存并列8个,地址线统一管理,比如00100101的地址,8个内存都是去同一个地址门锁,都是第2行第5列的地址。然后我们对8个内存的数据线进行并列管理,确定了位阶,这时候再输入一个数,就能是8bit的数了,比如输入01010001,其实就是分别将0,1,0,1,0,0,0,1分别存入了同一地址下的第1,2,3,4,5,6,7,8块内存当中,当然这要允许写入线打开,然后读取的时候,只要地址是原先的地址,读取的就是原先的数值。

我们进一步将它抽象,这就是我们的RAM,随机存取存储器。由8bit的地址,可存取8bit宽(8位值)的数据,然后一根读取,一根写入线来控制。如果我们想扩大位宽,的话,增加的是并列的内存块。如果我们想增加地址量的话,增加的是门锁矩阵数量。

这是我们常见的内存条RAM,小小的空间能存800万位。

第7集·中央处理器 - The Central Processing Unit(CPU)

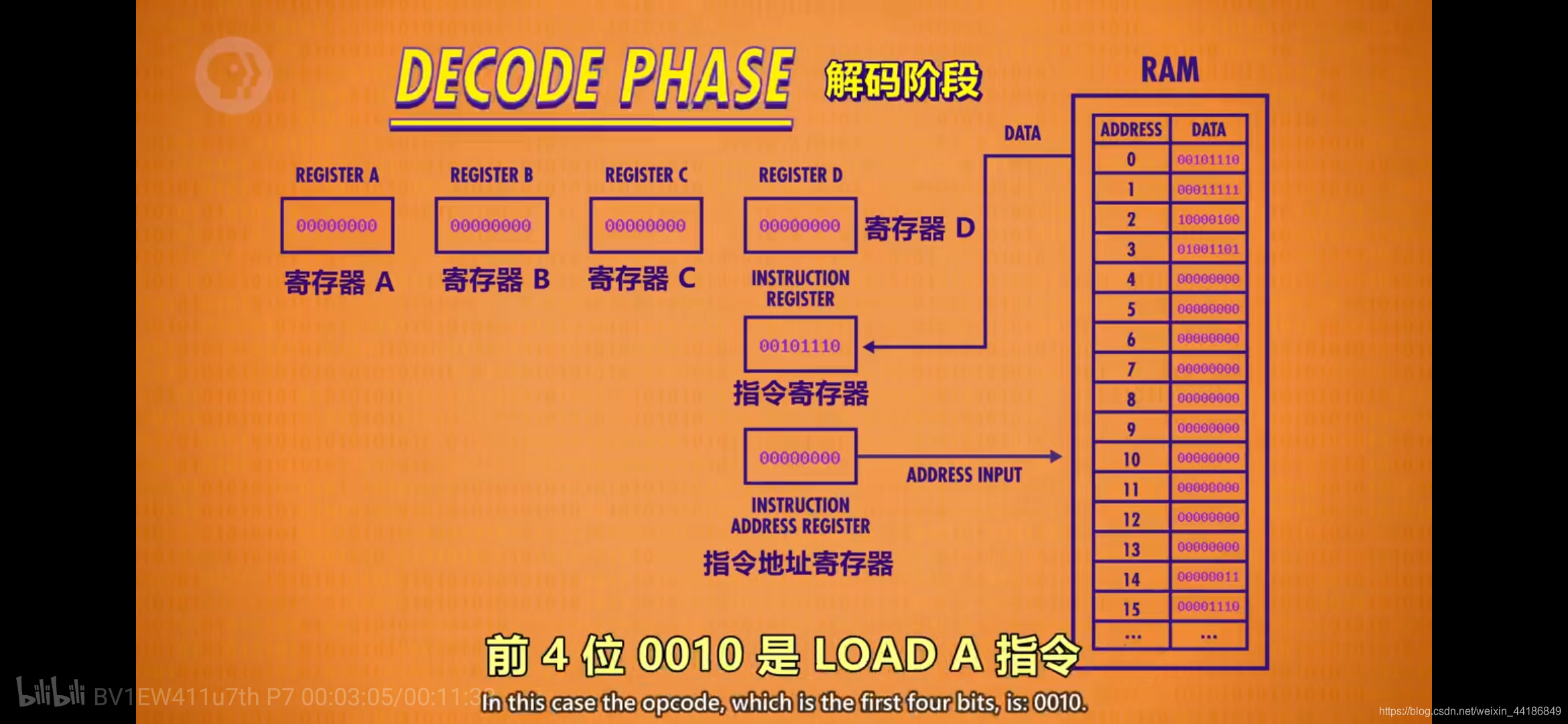

解码

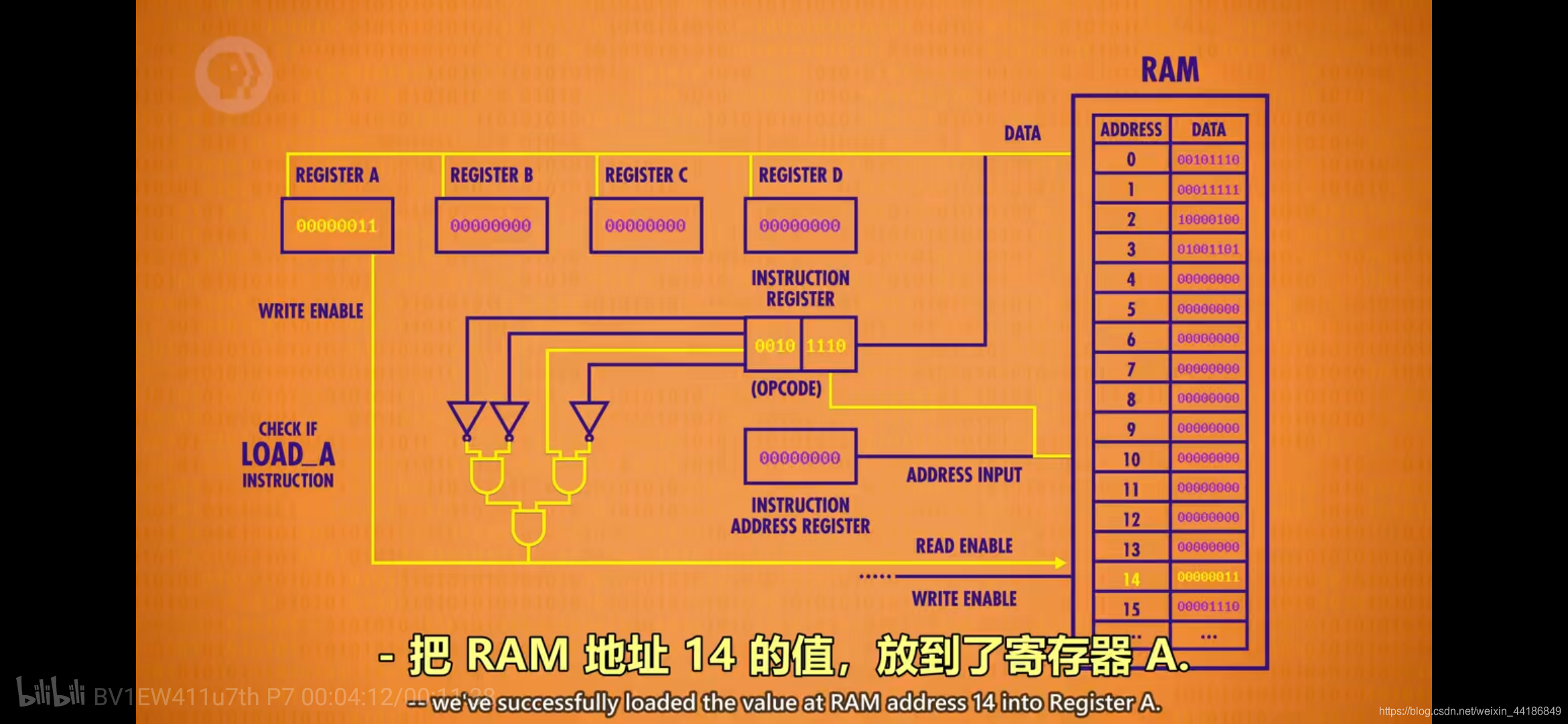

现在我们开始模拟跑我们的CPU,准备一个RAM,还记得一个8位宽的RAM 起码会留出一组8根的数据线,一组地址线,然后写入线和读取线。再来ABCD四个寄存器,其实一个8bit的寄存器正好上面有介绍,由8个并排的门锁构成,8根输入线,8根输出线,1根允许写入线控制,当然我们这里的寄存器,还会多一根允许读取线,另外8根输入线也是抽象成1根,这些线怎么连的,我们现在不关心。好,我们现在开始运行,先从指令地址寄存器开始,我们从地址00000000开始,该地址会索引到RAM的Address0号位置(其实它有16*16=256个地址位),先获取到地址0地址的DATA为00101110,至于这一串是什么含义其实是设计CUP的时候规定好的,我们将指令4|4划分,前4位是操作指令,后四位是操作地址。获取到这一串的DATA再去到指令寄存器,再由指令寄存器去做指令判断。

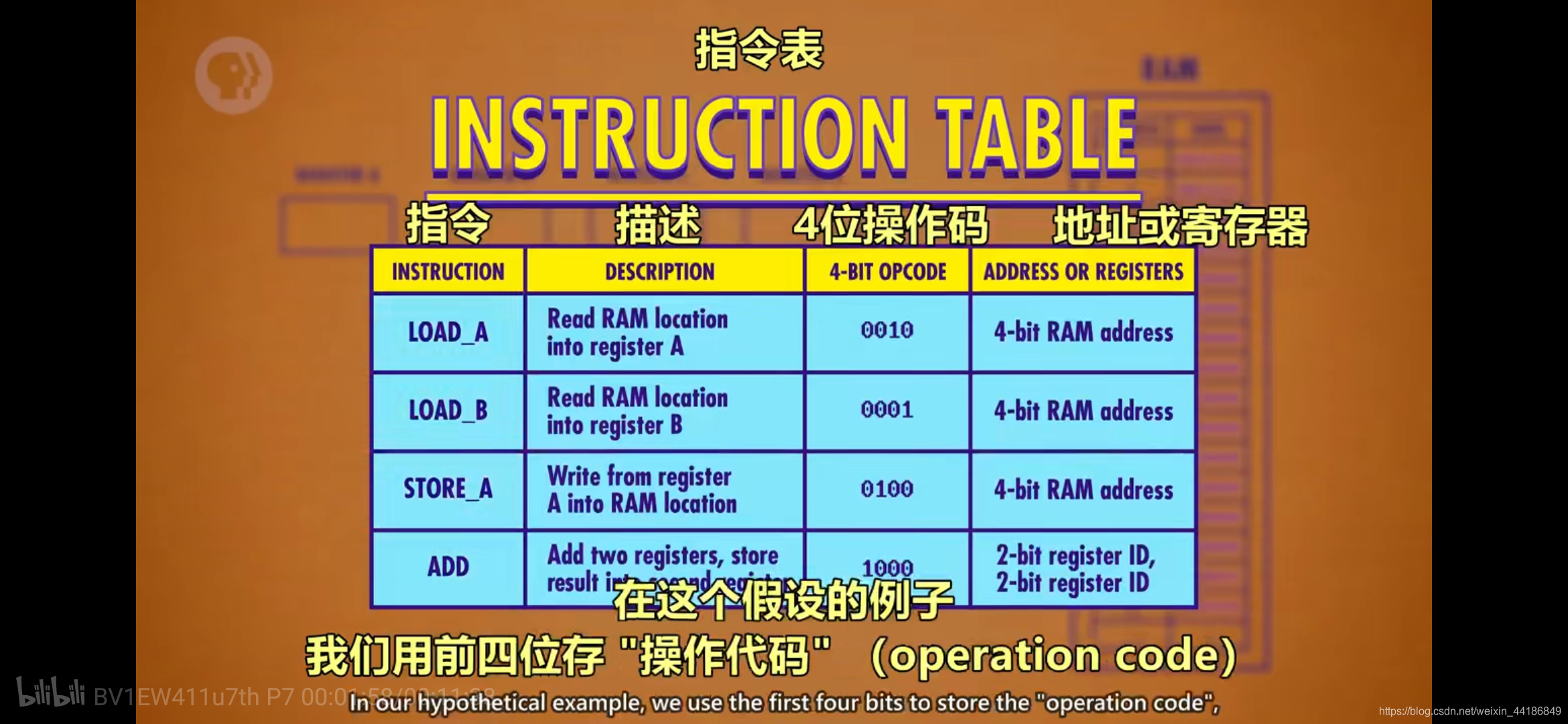

这里我们之间单的列举了最基本的四中指令,0010 加载到A寄存器,0001加载到B寄存器,0100存储A寄存器的值,1000,将寄存器的值相加。

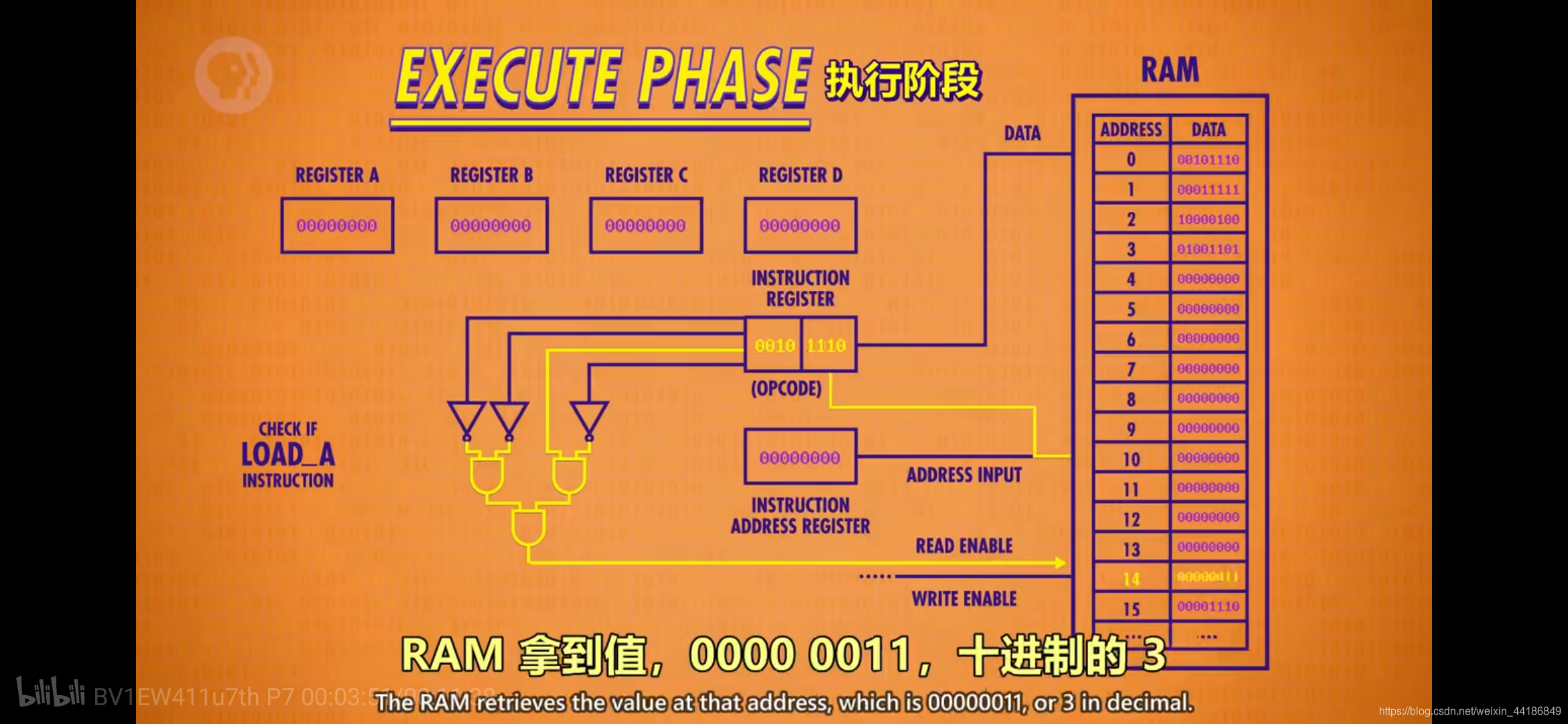

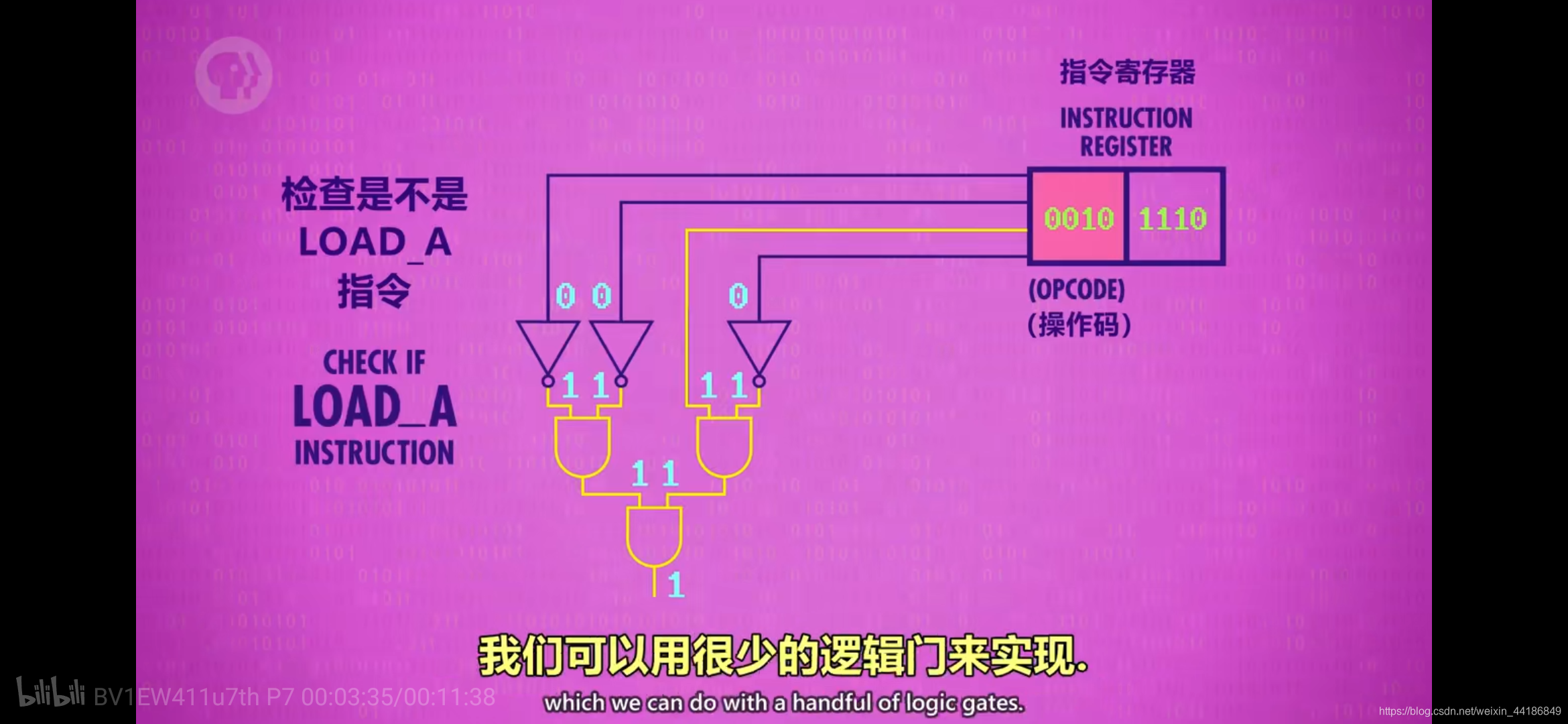

我们来看第一条指令。00101110,前四位0010,表示加载到A寄存器的指令,加载谁呢?加载地址为1110的数据,1110的部分就会与RAM的地址线联通,经过多路复用器打开指定地址的门锁,即14号地址。0010的部分,会经过指令检查逻辑来判断。

当指令是0010时,该逻辑门群才会输出1,当该逻辑们群路径通了的时候就说明指令是0010。

已经经过逻辑门群逻辑判断知道是0010,是 LAOD-A,所以这个逻辑门群的线或打开RAM的允许读取线,这个线是连读取线而不是写入线,是因为我们在设计CPU的时候已经规定了0010是加载,所以0010要连读取线,以及连接寄存器A的允许写入线。读取的是哪个地址的DATA是由后半部分的4位1110的地址来确定的,因为后半部分1110连接的是地址线,多用复路器会只打开RAM地址为14的门锁,然后RAM的数据OUTPUT就是该地址的数据,即RAM的DATA与ABCD的输入线相连,但是只有A的允许写入线是打开的,所以,RAM的14号地址的数据00000011被寄存到了寄存器A。如此,各个操作指令的执行逻辑流程就通顺了。其它的指令也是同样的逻辑,只不过经过的逻辑门群判断后的连线有所区别。

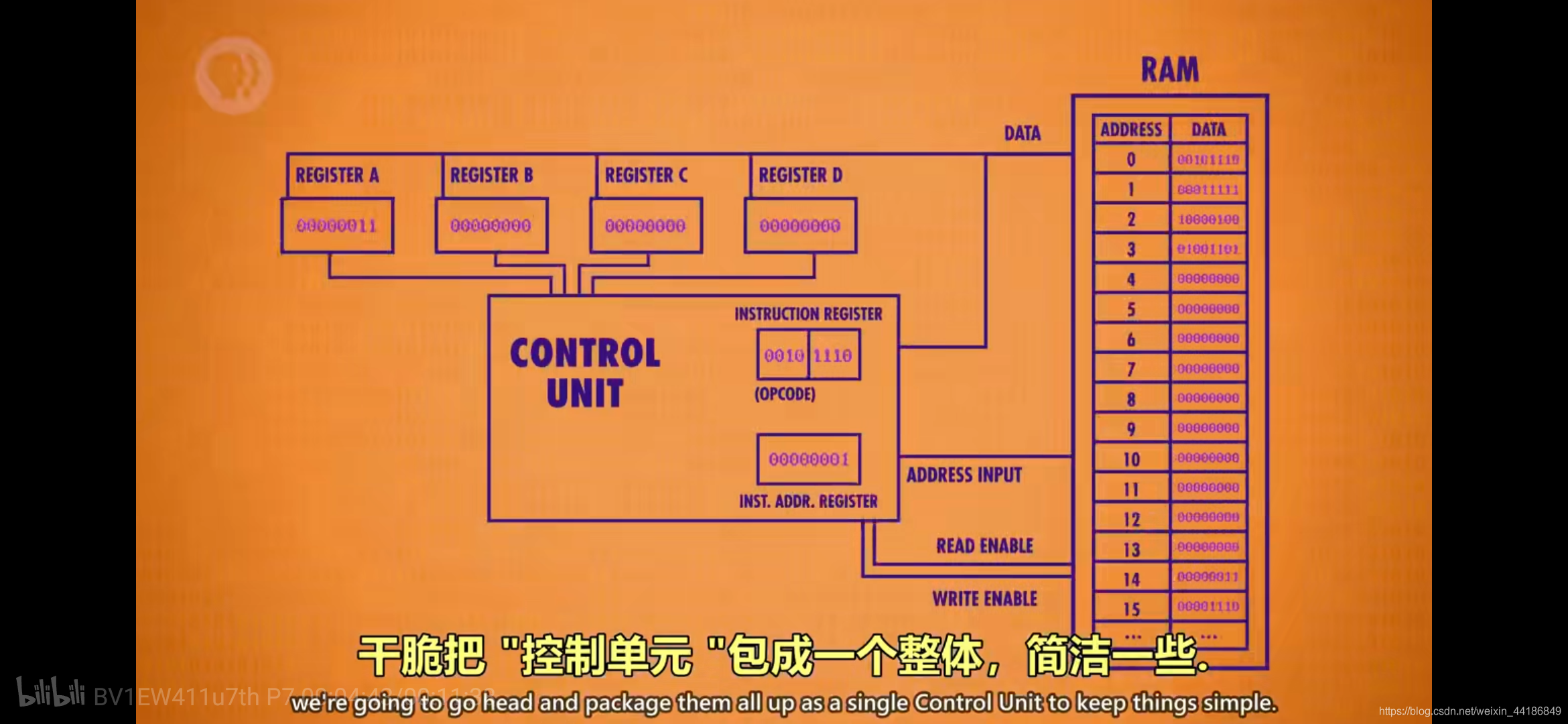

既然如此,我们知道了里面的控制原理,把控制单元包成一个整体好了,又进一步抽象了。

执行

现在我们来操作10000100的指令,这条指令是1000要把寄存器A和B的值相加存入0100地址。当我们判断出是1000指令,就会让ALU的允许操作线打开,该输入线,分别连接寄存器A和B的值,ALU内部是由一群半加器和全加器计算的,输出的数值与RAM的数据线相连,将数据传入RAM,传给谁,传给0100地址即4号地址。

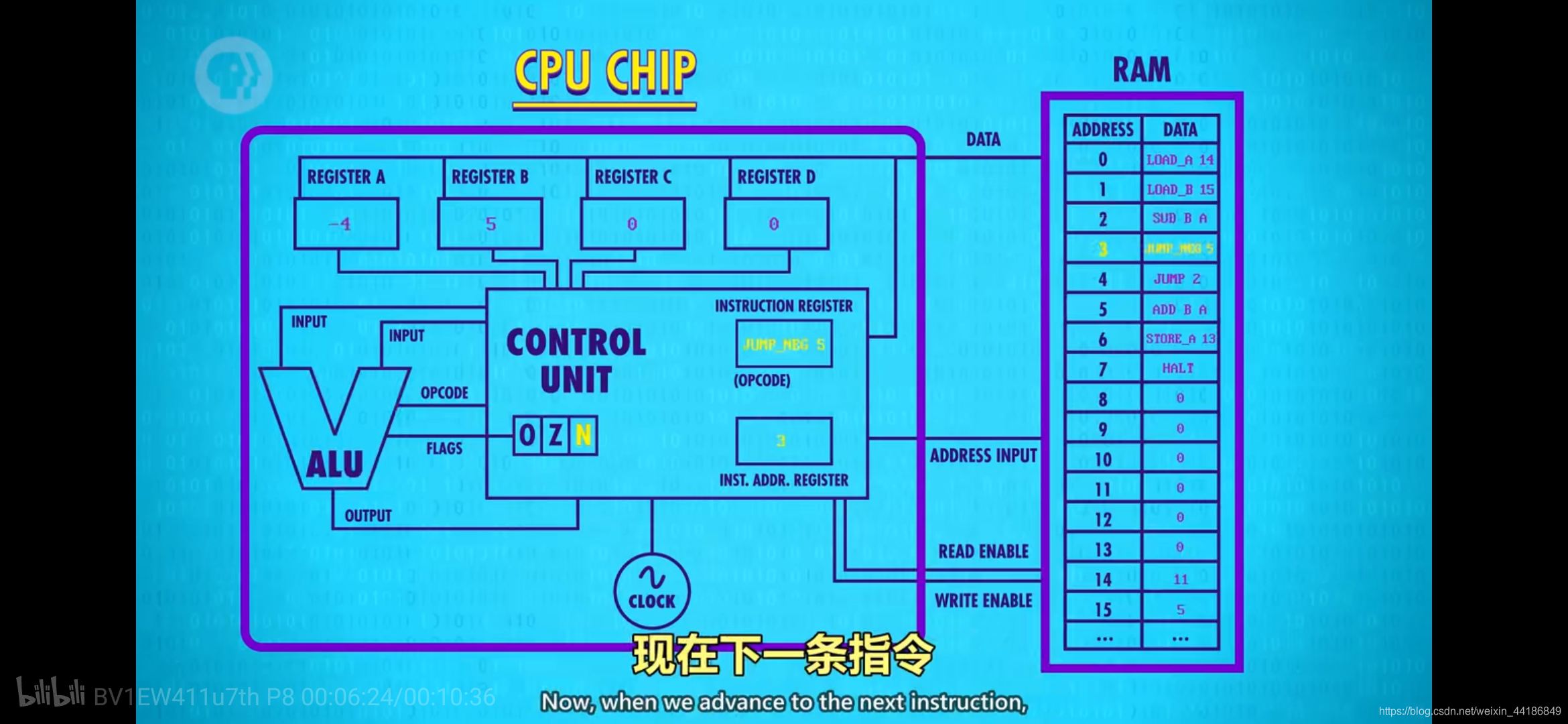

控制单元,加上ALU,再加时钟,寄存器等,我们把它放到盒子里,就成了一个独立组件,CPU。

英特尔的4004CPU架构也是类似的可以看到。其实CPU的底层构都是简单的,一系列的逻辑门去判断执行存储,难的是一层一层的抽象。

第8集·指令和程序 - Instructions & Programs

执行程序

我们给RAM做好几条简单的指令,从addres0开始,LOADA-14,加载14号地址的数据到寄存器A,就是11;下一步LOADB-15加载15号地址数据到寄存器B;下一条SUDB A,寄存器A减去B值存入寄存器A;接下来做条件跳转,当ALU的FLAGS负号标记符为真,则跳转到5,否则不动,往下执行JUMP2,跳转到2,可以发现又继续相减,接着又判断是否为负,直到为负值,跳转到5,ADDBA,把B的值加到A,存入A,然后STROEA 13,存储A寄存器的值到地址13,最终结束HALT。这一系列指令其实是计算11/5的余数的程序。CPU就这样 运转起来了。

第9集·高级 CPU 设计 - Advanced CPU Designs

缓存

CPU和RAM之间是由总线连接的,之间的数据交互需要时间,虽然电的速度非常快,这段距离也很短,但是你架不住上GHZ的频率。所以设计了缓存,缓存的作用就是在按地址取码的时候,不是取来一条,而是一批,当这条码解好,要解下一条时,先从缓存里面查询有没有需要的地址内容,如果有就直接获取了,这样能大大节省数据交互时间,如果没有就从RAM里面去获取。

流水周期

我们CPU执行通常分为三个阶段,FCTCH取码,DECODE解码 EXECUTE执行,按照之前的设计方式,我们就得等这一条的三个阶段全部执行完毕了,才能执行下一条,这会产生大量的闲置时间。比如我取一条A指令,现在先取码,这时候 解码和执行的组件就处于限制状态,然后进入解码模块,取码和执行又处于闲置状态。所以设计师设计了流水线操作,如图,这样原本3*7=21个时钟周期的过程,只需要3+6=9个时钟周期。大大节省了闲置时间。

多线程与多核,4个不同的进程可以分别在不同的核心中同时执行,这大大加快了系统的速度。由于4个核心都在一个芯片上,因此它们之间的通信也要更快,系统也会有更小地延迟。

526

526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?