NullReferenceException: Object reference not set to an instance of an object

NullReferenceException

“你调用的对象是空的。” 为那些在初学者 C#/.NET 程序员时从未遇到过此错误消息的人投下第一块石头。

当您收到 NullReferenceException 时,就会出现这个臭名昭著且可怕的错误消息。当您尝试访问当前持有空引用的变量的成员(例如,方法或属性)时,会抛出此异常。

但是什么是空引用呢?首先什么是“参考”?如何阻止 NullReferenceException 在您的代码中发生?这就是我们今天要介绍的内容。

我们将从基础开始,简要说明 C#/.NET 中的引用。之后,您将了解什么是空引用。在这一点上,您已经看到了整个画面的一半。

在这一轮理论定义之后,我们将进入更实际的问题,教你如何在实践中避免 NullReferenceException。让我们深入挖掘。

什么是空引用

我们已经知道 NullReferenceException 是由空引用引起的。但是什么是空引用呢?它与非空引用有何不同?

在 .NET 中,您可以将数据类型分为两类:值类型和引用类型。如果你有一个值类型的变量,它存储值本身。另一方面,引用类型变量本身不保存值。它们持有指向对象在内存中所在位置的引用。

如果它能帮助您更好地形象化它,您可以将引用视为指向网页的链接,或指向计算机上文件的快捷方式。诸如 int(和其他数字原始类型)、DateTime 和 boolean 之类的类型是值类型。也就是说,结构是值类型。类是引用类型。

因此,引用是引用类型的变量包含的内容。不过,这些变量可以指向“无”,这就是我们所说的空引用:不指向任何对象的引用。当您尝试调用上述变量的方法或另一个成员时,您会得到 NullReferenceException。

如何避免

空引用错误占所有应用程序错误的很大一部分。它们通常是由于没有添加额外的逻辑来确保对象在使用它们之前具有有效值而导致的非常简单的问题。下面是一些避免 NullReferenceException 的方法。

如果传入的变量“text”为空,以下代码将抛出 NullReferenceException。您不能对空字符串调用 ToUpper()。

public void MyMethod(string text)

{

//Throws exception if text == null

if (text.ToUpper() == “Hello World”)

{

//do something

}

}

使用 Null 条件运算符来避免 NullReferenceExceptions

您可以使用“?”来代替大量的“variable != null”类型检查。并且您的代码将短路并返回 null 而不是抛出异常。通过下面的一些示例,这将更有意义:

text?.ToUpper(); //前面的例子,将返回空

int? length = customerList?.Length; // 如果 customerList 为 null,则为 null

Customer first = customerList?[0]; // 如果 customerList 为 null,则为 null

int? count = customerList?[0]?.Orders?.Count(); //如果 customerList、第一个客户或订单为 null,则为 null

使用 Null 合并来避免 NullReferenceExceptions

另一个很棒的功能是null coalescing,即“??” 操作符。它非常适合为空变量提供默认值。它适用于所有可为空的数据类型。

以下代码在没有空合并的情况下抛出异常。添加“?? new List()”防止“对象引用未设置到对象的实例”异常。

List<string> values = null;

foreach (var value in values ?? new List<string>())

{

Console.WriteLine(value);

}

空值导致问题的简单示例

一些最常见的原因是设置、数据库调用或未返回预期值的 API 类型调用。例如,您向数据库中添加了一个新字段,但没有为每条记录填充默认值。随机记录被查询,并且代码没有说明新字段为空。

编程的黄金法则

多年来,我一直对我的团队说一句话。我称之为编程的黄金法则。我认为每个新程序员都需要一个能说明这一点的纹身。

“如果它可以为空,它将为空”

好消息是,通过添加额外的逻辑和代码来确保对象在尝试使用它们之前不为空,可以避免很多空引用错误。开发人员应该始终假设一切都是无效的,并且在他们的代码中非常防御。假设每个数据库调用都会失败,每个字段都会弄乱其中的数据。良好的异常处理最佳实践至关重要。

防止空引用异常的技巧

- 用有效值初始化变量。

2.如果变量可以为null,则检查是否为null并适当处理

3.使用“?” 可能时在方法上使用运算符。stringvar?.ToUpper();

4.使用像Resharper这样的工具来帮助指出潜在的空引用异常

使用 C# 8.0 的可空类型避免 NullReferenceException

空引用错误的主要原因之一是在 C 中,每个引用类型对象始终可以为空。如果您,开发人员,有权说:“我希望这个字符串永远不会为空”怎么办?更好的是,如果这个决定是由编译器本身强制执行的,以防止您和其他开发人员意外地将 null 分配给所述变量怎么办?听起来不错?好消息:这是 C# 第八版的一个真正的特性,毫不奇怪,它被称为可空类型。

该功能以巧妙而强大的方式工作。它将引用类型重新定义为默认情况下不可为 null——许多人认为它们从一开始就应该如此。然后,它添加了一种新的语法,允许您定义可为空的变量(不过,这并不是真正的新语法,因为它与多年来用于可空值类型的语法相同。)

为了更好地理解,请看以下示例:

static int Add(string numbers)

{

return numbers.Split(“,”).Select(int.Parse).Sum();

}

在 8.0 之前的 C# 版本中,上面的代码是危险的。numbers 变量可能为 null,这会在尝试使用 Split 方法时导致 NullReferenceException。

使用 C# 8.0 可为空的引用类型功能,你会很安全。该变量永远不会为 null,对 Split 方法的调用也永远不会抛出异常。任何将 null 传递给 Add 方法的尝试都会导致编译错误。

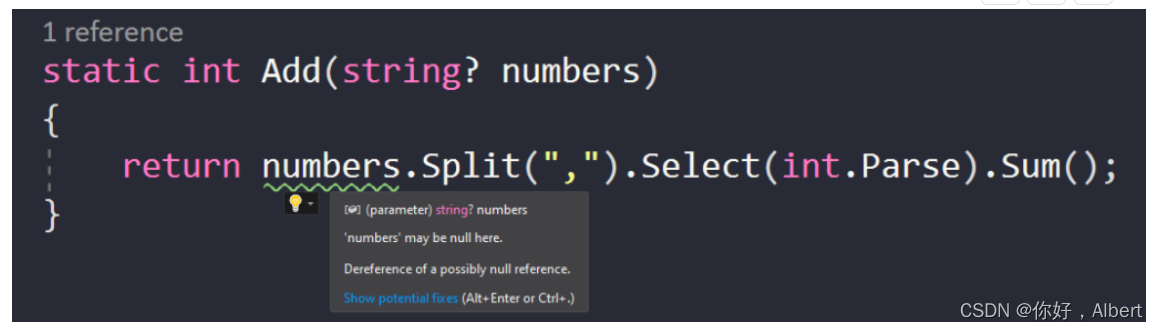

但是如果你想在数字中允许 null 怎么办?在这种情况下,您只需在类型名称后添加一个问号:

static int Add(string? numbers)

{

return numbers.Split(“,”).Select(int.Parse).Sum();

}

现在情况发生了巨大变化。由于数字现在可以为空,编译器会提示您检查变量的值,并发出警告(您可以将警告变成编译器错误,以提高安全性):

编译器让我知道“数字”可以为空。可能的解决方案包括:

使用 if 语句确保变量具有有效引用

在调用 Split 方法时使用已经提到的空合并运算符

通过删除问号再次使“numbers”变量不可为空

抑制给我们警告的规则(这会破坏整个目的,但是嘿,这是一个选择。)

请记住,此功能是可选的。也就是说,默认情况下它是禁用的,您必须在项目配置中激活它。这样做的原因是运送已经启用的功能会导致大多数代码库发生重大变化。

所以:遵循我的黄金法则:如果它可以为空,它将为空!

其他原因

unity3d函数执行顺序:Awake->OnEable->Start->FixedUpdate->Update->LateUpdate->OnGUI->Reset->OnDisable->OnDestroy

注意是不是在调用时,变量还没有初始化

1692

1692

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?