一、简介

2019年10月,在恩智浦 ARM 技术大会上一则宣传语彻底引爆微控制器界,“单片机首次迈入 1GHz 主频大关”。

i.MX RT 系列的 i.MX RT1170 首次将 ARM Cortex-M7 的主频提升至 1 GHz,并且首次引入双核概念,双核系统搭载一颗高性能内核和一颗高能效内核。

一颗主频高达 400MHz Cortex-M4 内核,这颗 Cortex-M4 可以用作专门处理一些相对简单的外设资源、金融级别的信息安全、低运行/低待机功耗,有了这颗高能效的 Cortex-M4 内核,另一颗超高性能的 Cortex-M7 核可以专注于音视频识别与处理、千兆以太网通信控制等复杂任务上,双核系统中这两颗内核均可作为主从关系,用户可以自定义主从关系,从核由设定的主核启动后激活

二、i.MX RT1170 应用

这颗强劲的 MCU 的应用也十分广阔:

智能家居的HMI或主处理器

音频/语音处理

新兴消费/零售设备

工业控制

楼宇控制

智能能源系统

马达驱动

医疗仪器

汽车/摩托车 HMI

Auto 处理器

三、双核通信

3.1 双核通信简介

有着高性能和高能效双核的 i.MX RT1170 ,在双核系统中双核间的通信更是系统中十分重要的环节,双核间有四种通信分享资源方式 :

MU

SEMA4

RDC/XRDC2

分享内存

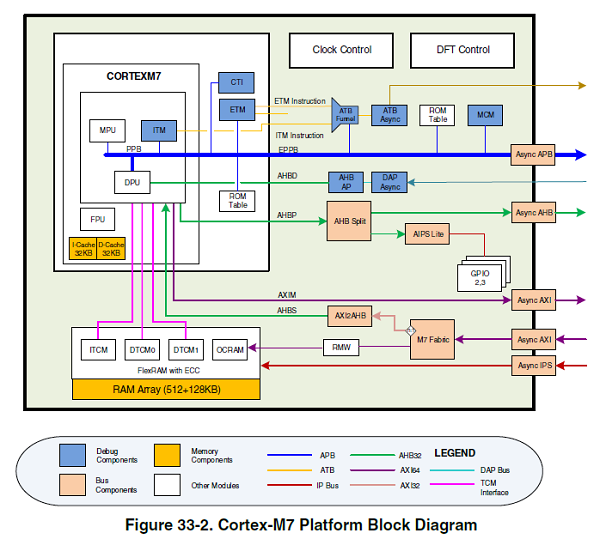

3.2 ARM Cortex M7 核

Cortex-M7 处理器是一款高效、高性能的嵌入式处理器,具有低中断延迟、高效、简易调试等特性,并向后兼容现有主要的 Cortex-M 处理器,处理器有一个超标量顺序流水线,可以通过它双发指令。32kb 指令/ 32kb 数据的 L1 缓存与可配置大小指令和零访问等待 TCM (默认为 256kB ITCM /256kB DTCM) 具有 ECC 接口,赋予 i.MX RT1170 卓越的处理能力与实时性能。

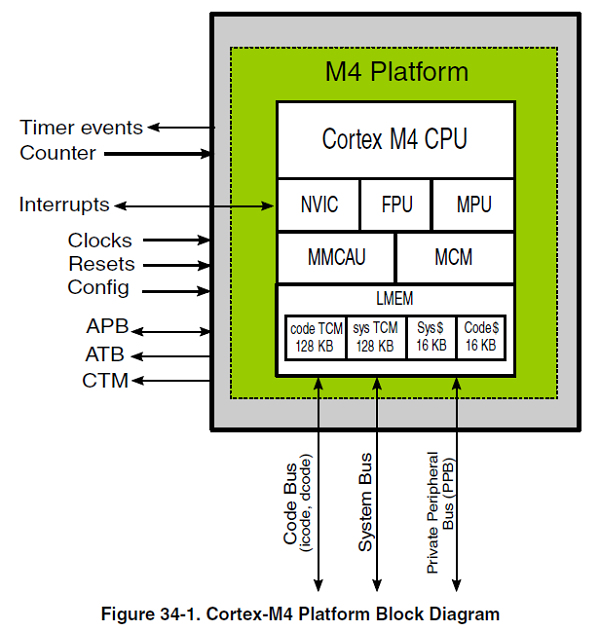

3.3 ARM Cortex M4 核

Cortex-M4 内核为 SoC 提供了额外的通用处理能力,具有较低的功耗和快速的中断响应时间,Cortex-M4 包括一个单精度浮点单元 (FPU) 、两个 32 位系统总线接口,TCM 内存支持 ECC,16kb 代码/ 16kb 系统缓存支持奇偶校验,保证强大处理能力的同时确保程序和数据的可靠性。

3.4 电源架构

双核架构意味着会提升功耗,i.MX RT1170 MCU 针对不同电力需求应用设计,如低功耗、长电池寿命、始终开机、瞬间开机能力,并且不需要冷启动。为了满足这些要求,芯片设计的重点是减少电流消耗的同时,使峰值性能达到最高水平,并且也达到持续性能的平衡水平,通过使用了多种电源管理技术,组合以提高系统功耗设计的灵活性。

多达 16 个可编程电源设定点,用于根据当前处理器工作情况、功能的使用和电源要求配置时钟源、外设时钟、电压、系统电源域和其他外设资源,在多核系统开发中,可根据应用功耗需求考量每个 CPU 内核适当的功耗模式配置,以满足内核与整个系统的需求。

3.5 电源管理架构特性

-

可编程电源模式转换规则

-

单个CPU核的独立运行模式

-

多核架构的智能时钟和电源管理

-

UPI (Unified power management interface) 统一电源管理界面,对所有片上资源包括时钟、电源、复位、外设等进行统一管理。

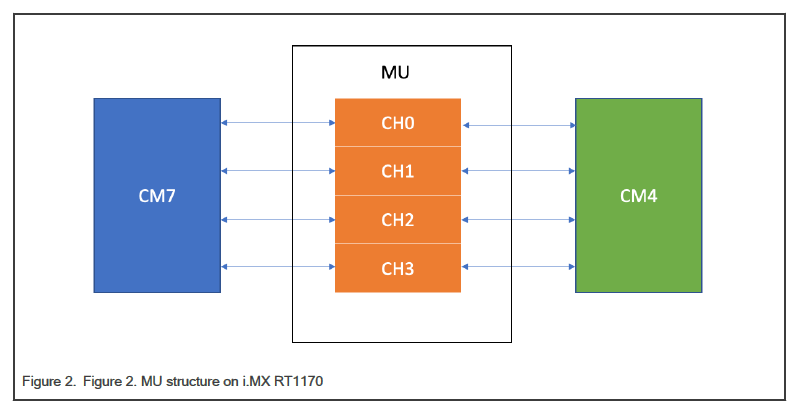

3.6 MU

通过 MU(Messaging Unit)消息传递单元,一个核可以向另一个核发送 32 位的消息,并触发另一个核的中断,它支持四个双向通道。

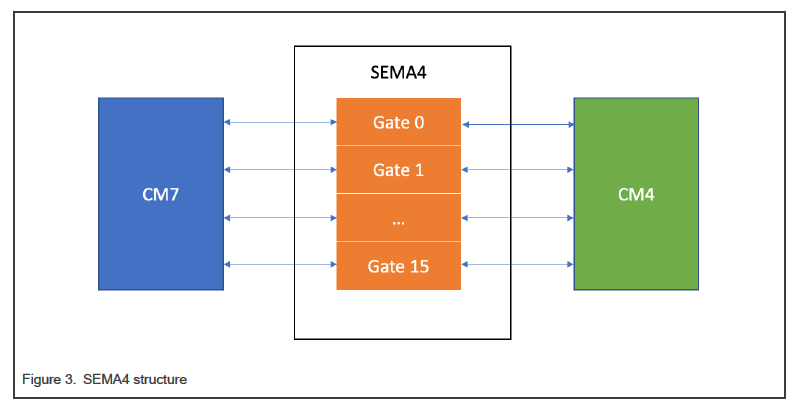

3.7 SEMA4

SEMA4 通常用于保护多核环境中的资源,以防止不同的主机同时使用一个资源,该资源可以是内存块、外设或者甚至是内存中的 SW 对象,SEMA4最多支持 16 个门,只有成功锁住这个门并获得 sema4 的核,才能使用这个sema4门保护的资源,其他核必须等待,直到拥有这个门的核,释放或开放这个门。

3.8 RDC/XRDC2

RDC/XRDC2 用于资源隔离,资源可以是外围设备或内存,权限可以被读、写,也可以同时被读和写。

例如,我们可以将 LPUART1 分配到 CM7 域,那么只有 CM7 核可以访问 LPUART1。如果其他总线主机( 如 CM4 核)访问 LPUART1 就会发生 ISR 冲突

3.9 分享内存

CM7 核和 CM4 核都可以访问共享内存,如果一个数据块需要从一个核传递到另一个核,那么 MU 共享内存可以是一个很好的候选。

典型的工作流程如下:

-

一个核向 B 核写入块数据

-

步骤 1 完成后,A 核触发 B 核 MU 中断,B 核知道 A 核有数据块准备好。

-

B 芯读取数据块并处理。

-

步骤3完成后,B核触发 A 核 MU 中断,A 核知道 B 核已经处理了数据块,然后 A 核可以加载 B 核的下一个数据块。

四、双核通信例程

4.1 创建双核 MU 工程

以下例程介绍以四种通信方式中的 MU 通信方式为例,从创建 SDK 工程开始、概述例程、到演示例程效果。

4.1.1 SDK 获取

SDK 可再 NXP 官网根据需求添加部件自定义生成 SDK,NXP MCUXpresso SDK Builder 的链接如下 MCUXpresso SDK Builder

4.1.2 创建 MU 工程

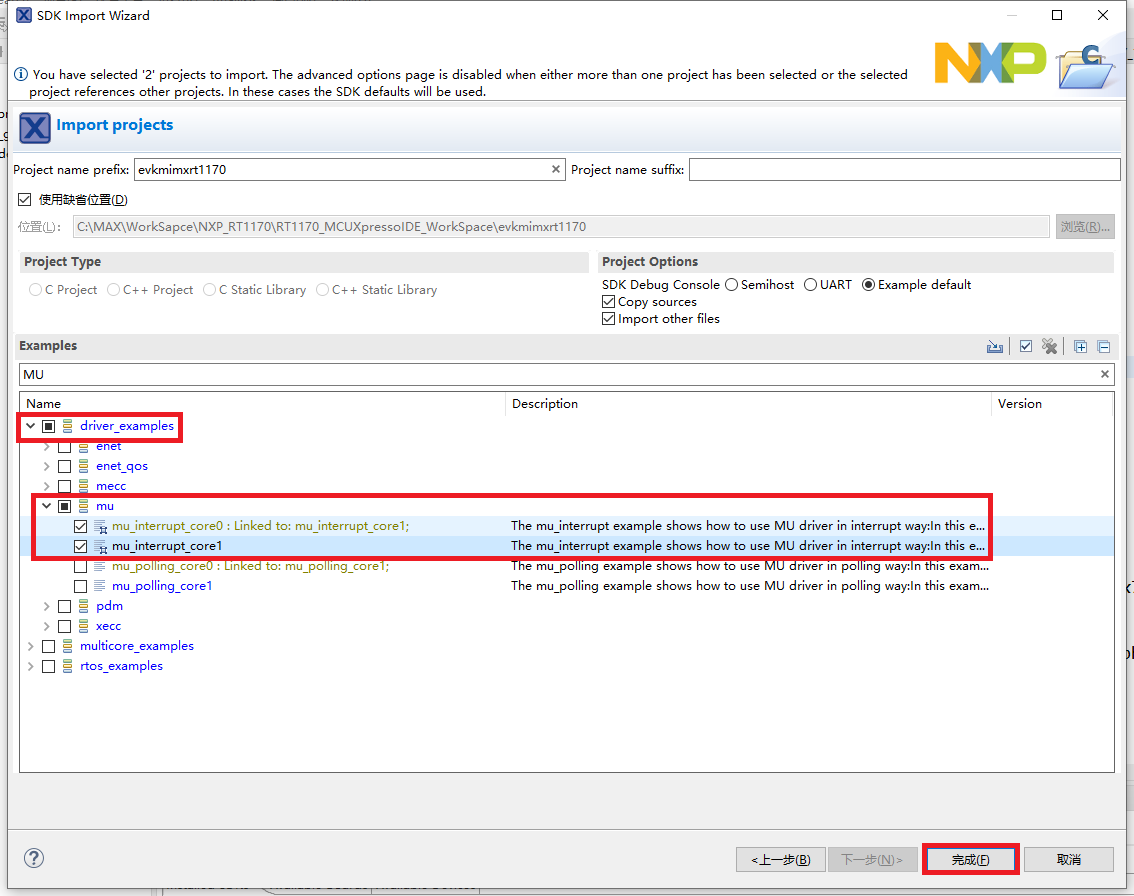

文件 -> Import SDK Examples -> evkimxrt1170 -> driver_examples -> mu -> 选择 mu_interrupt_core0 会Link 上 mu_interrupt_core1 自动勾选。

4.1.3 双核通信调试

双核调试指南,请参阅入门 MCUXpresso SDK For MMXRT1170-EVK ( 文档MCUXSDKMIMXRT117XGSUG),可在 MCUXpresso SDK Builder 官网上找到。

五、芯片 BOOT

5.1 Boot

工程的 Application 代码存放在FLASH中,每次上电 CPU 都会自动从 FLASH 里获取用户的 Application 代码,然后由 Bootloader 跳转至 Application 代码执行,这个操作就是 Boot。

5.3 主从核 Boot

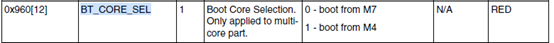

i.MX RT1170 MCU 启动过程在任何复位时开始,其中硬件复位逻辑会强制Arm核心由 BT_CORE_SEL 位的设定决定从片上引导 ROM 的开始执行。

如果BT_CORE_SEL 位为 1,ROM 将从 Cortex-M4 核心而不是Cortex-M7 核心执行,由于 Cortex-M4 核的 ROM 执行时间较慢,所以从 M4 核心引导会比较慢。

5.4 Boot 方式

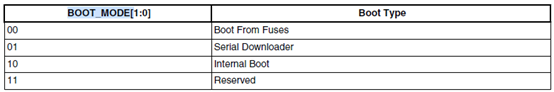

引导 ROM 代码使用内部寄存器 BOOT_MODE[1:0] 的状态,以及各种 eFuses 值和 GPIO 设置的状态来确定设备的引导操作。

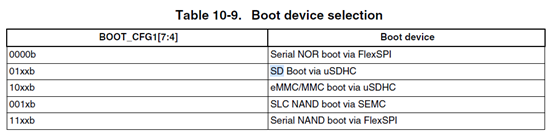

i.MX RT1170 MCU 外部启动设备类型的选择由寄存器 BOOT_CFGI[7:4] 控制:

i.MX RT1170 支持以下存储器加载启动 flash 设备:

-

Serial NOR flash via FlexSPI Interface

-

Serial NAND Flash via FlexSPI Interface

-

NAND Flash with SEMC interface, located on CS0, 8-bit/16-bit bus width.

-

SD/MMC/eSD/SDXC/eMMC5.0 via uSDHC interface, supporting high capacity cards

-

Serial NOR/EEPROM boot via LPSPI

946

946

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?