1、关于function new里的string name、uvm_component parent?

(截至目前的答案)是new函数里的默认参数,不一定要赋值,直接像下面这么写就可以:

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction2、build_phase和main_phase是什么?

uvm验证总结(三)------phase机制 - 知乎 (zhihu.com)

(参考以上内容,只记录我想要的部分)

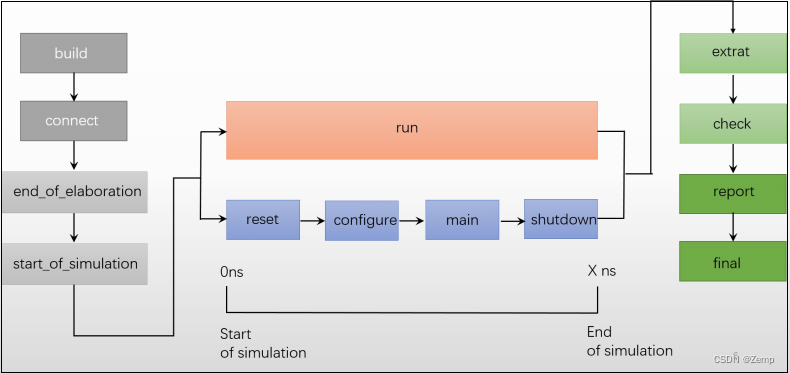

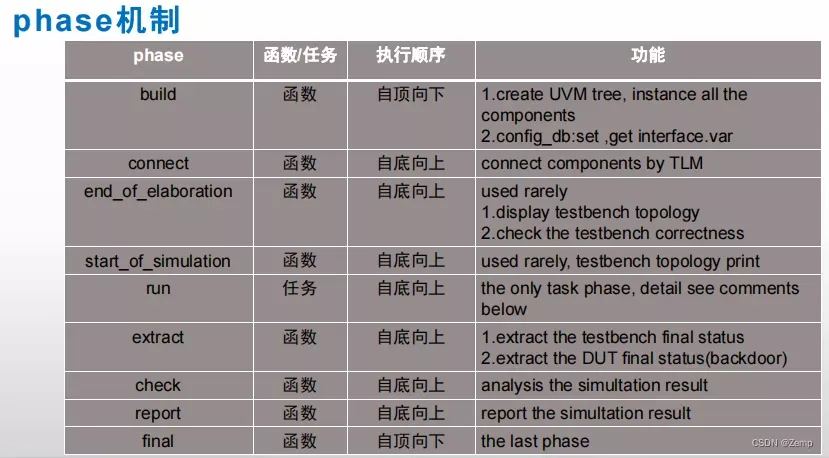

UVM中的phase总体可以分为function phase和task phase两大类,其中function phase 不消耗仿真时间,task phase 需要消耗仿真时间。

这里面除了run_phase是task_phase之外,其余全都是function_phase。因此,得出以下结论:

(1)build_phase是function_phase,main_phase是task_phase。

(2)在build_phase中可以定义一些组件例化和配置的任务,main_phase中通常要执行激励、采样等任务。

这其中的执行顺序如上所示,因此得出结论:

(3)build_phase在mian_phase之前执行。

对于同一个component的phase执行顺序如上所示,对于不同component的phase执行顺序如下所示。

3、UVM中什么时候用virtual?

(12条消息) uvm中virtual如何使用_zsmcdut的博客-CSDN博客_uvm virtual function(参考来源)

(1)virtual interface:在不同组件中例化的接口是独立的,改变的仅仅是当前接口的值。

(2)virtual class :必须使用 extends class来进行实体化才可以使用,OOP规定,只要class中存在一个没有实现的pure function,就不允许例化这个class

(3)virtual function/task:避免在uvm中出错的最好方式是,如果该class不会被继承,则所有的function/task都不需要加virtual。如果该class会被继承,则用户定义的function/task(除new()、randomized()、pre_randomize()、pose_randomize()以外),都应该加上virtual。

4、uvm_top、uvm_test_top的区别是什么?

1-uvm_root, uvm_top, uvm_test_top - _见贤_思齐 - 博客园 (cnblogs.com)(参考来源)

(1) uvm_top:UVM中真正的树根,任何组件实例都在它之下(如果组件的parent为null,那么该组件为uvm_top的子组件)。uvm_top是一个全局变量,是uvm_root的一个实例,也是uvm_root唯一的实例。uvm_top的名字是_top_,但是在显示路径时,并不会显示这个名字,而只显示从uvm_test_top开始的路径

(2)uvm_test_top:通过run_test语句创建的实例的名字为uvm_test_top,无论传递给run_test的参数是什么,创建的实例的名字都为uvm_test_top。

uvm_test_top的parent是uvm_top,而uvm_top的parent是null。UVM中,支持uvm_top下有多个叶子节点,但是,多个叶子节点不能都叫uvm_test_top。

5、带参数的宏在使用时,分号是多余的。比如:

if(flag)

`uvm_info("my_driver", "driver is called!", UVM_LOW);

else

`uvm_info("my_driver", "driver is not called!", UVM_LOW);

//编译会报错在uvm_info后加上一个分号,分号即一个空语句,编译时在关键字if后看到的是两条语句,如果没有begin...end包围,那么就存在语法错误。

//一种方法是去掉分号

if(flag)

`uvm_info("my_driver", "driver is called!", UVM_LOW)

else

`uvm_info("my_driver", "driver is not called!", UVM_LOW)

//如果非要加上分号,则需要加上begin...end

if(flag)

begin

`uvm_info("my_driver", "driver is called!", UVM_LOW);

end

else

begin

`uvm_info("my_driver", "driver is not called!", UVM_LOW);

end6、uvm_object_utils扩展而来的类里,function new中只有string name

function new(string name = "my_transaction");

super.new(name);

endfunction7、在UVM种,同城使用TLM(Transaction Level Modeling)实现component之间的transaction之间的通信。

数据发送的方式有很多种,其中一种是uvm_analysis_port;

数据接收的方式也有很多种,其中一种是uvm_blocking_get_port。

在定义了端口之后,还没有实现通信,需要在env中使用fifo将两个端口联系在一起。

1089

1089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?