A SR锁存器

A.a 触发器概述

触发器定义:能够存储1位二值信号(0或1)的基本单元电 路(与非门等)统称为触发器。触发器是构成时序逻辑电路的 基本电路,是联系组合逻辑电路和时序逻辑电路 的桥梁。

触发器的两个基本特点 :

1 两个互补的输出端Q和Q’,具有两个能自行保持的稳定状态(双稳) 表示逻辑状态的‘0’和‘1’;

2 根据不同的输入信号可以置成1或0状态。

3 可以从一个稳定状态转移到另一个稳定状态。

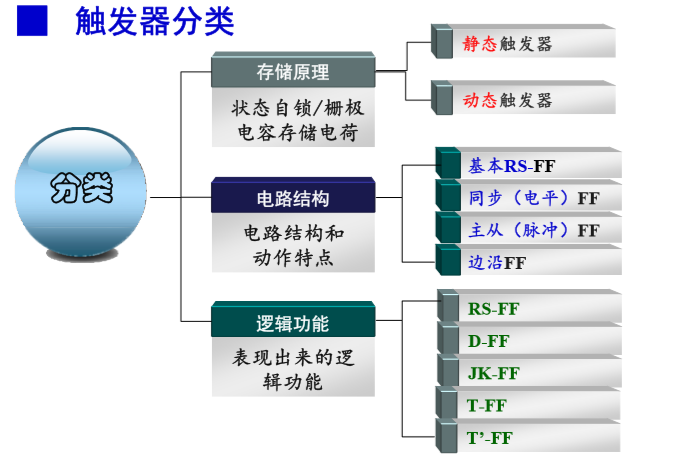

触发器(FF)分类

本章讲的都是静态的触发器。

A.b SR锁存器(基本RS触发器)

SR锁存器(又称基本RS触发器)是各种触发 器电路中结构形式最简单的一种(输入信号直接作用在触发器是上面,无需触发信号),同时,它又是 许多复杂电路结构触发器的基本组成部分。

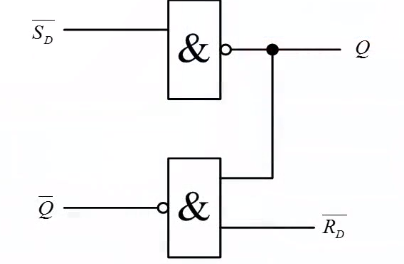

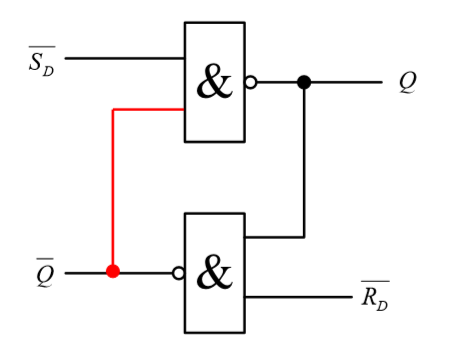

演变

上图只是一个组合逻辑电路,没有存储记忆功能。

加入红线后不再是简单的组合逻辑电路,而拥有存储记忆功能了。

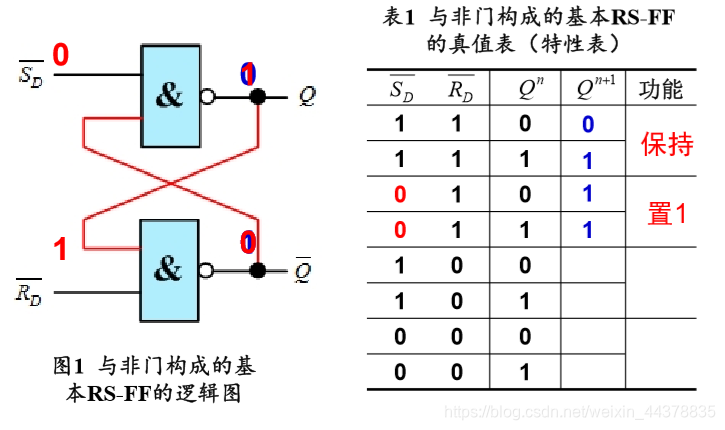

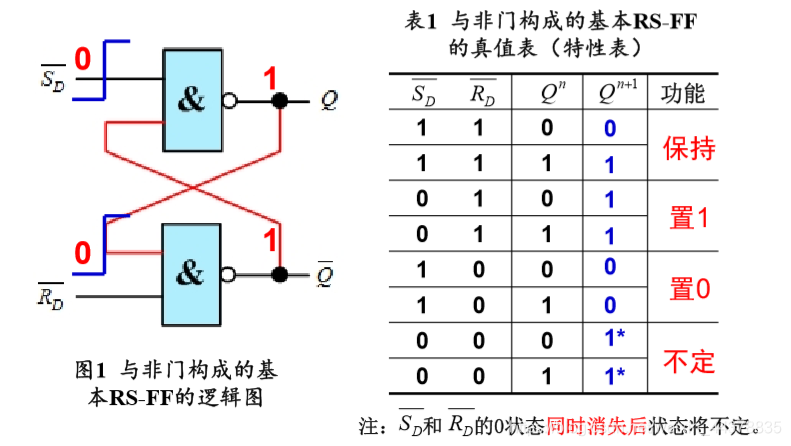

A.b.a 与非门构成的SR锁存器工作原理

|  |

|  |

Q

n

Q^n

Qn为电路的原态,为0时表示电路当前的

Q

Q

Q为0,

Q

′

Q'

Q′为1;

Q

(

n

+

1

)

Q^(n+1)

Q(n+1)为新态。

图中蓝色为原态的值。

S

D

S_D

SD可以理解为Set Data缩写;

R

D

R_D

RD可理解为Reset Data缩写。两者都是低电平有效。

第四个图输出不满足

Q

Q

Q与

Q

′

Q'

Q′的逻辑定义,是一种特殊情况。输出状态由两个输入上升沿的前后决定(谁先变为1),所以功能为不定。

与非门构成的SR锁存器特点:

1 触发器新的状态

Q

n

+

1

Q^{n+1}

Qn+1(也叫次态)不仅与输入状态 有关,而且触发器原来的状态

Q

n

Q^n

Qn(也叫初态)有关;

2 由与非门构成的基本R-S触发器用

S

D

′

S'_D

SD′和

R

D

′

R'_D

RD′分别表 示“置1”输入端和“置0”输入端,它们均以低电平作为输 入信号;

3 由于

S

D

′

=

R

D

′

=

0

S'_D=R'_D=0

SD′=RD′=0时出现非定义的

Q

=

Q

′

=

1

Q=Q'=1

Q=Q′=1状 态,而且当

S

D

′

和

R

D

′

S'_D和R'_D

SD′和RD′同时回到高电平以后触发器的状态 难于确定,因此正常工作时应遵守

S

D

R

D

S_DR_D

SDRD=0的约束条件, 即不应加以

S

D

′

=

R

D

′

=

0

S'_D=R'_D=0

SD′=RD′=0的输入信号。

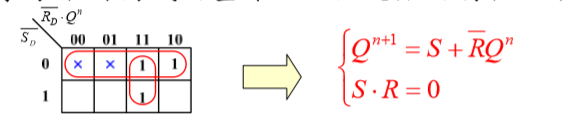

与非门构成的SR锁存器描述

将

S

D

R

D

=

0

S_DR_D=0

SDRD=0作为输入约束条件,由卡诺图化简 可得与非门构成的基本RS-触发器的特性方程如下:

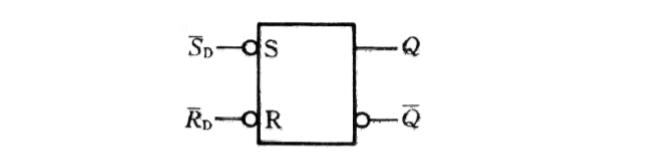

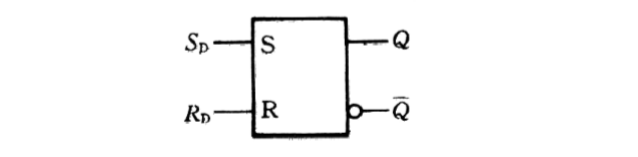

与非门构成的基本RS-触发器的图形符号如下:

图中圆圈表示低电平有效。

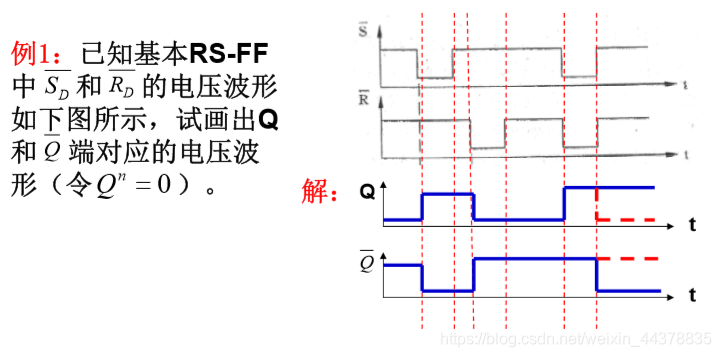

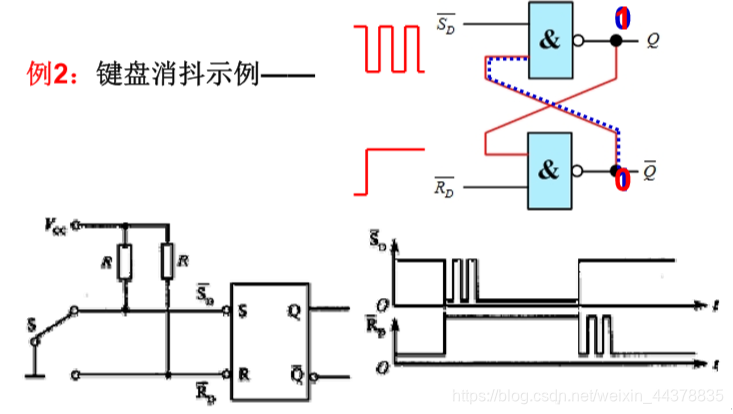

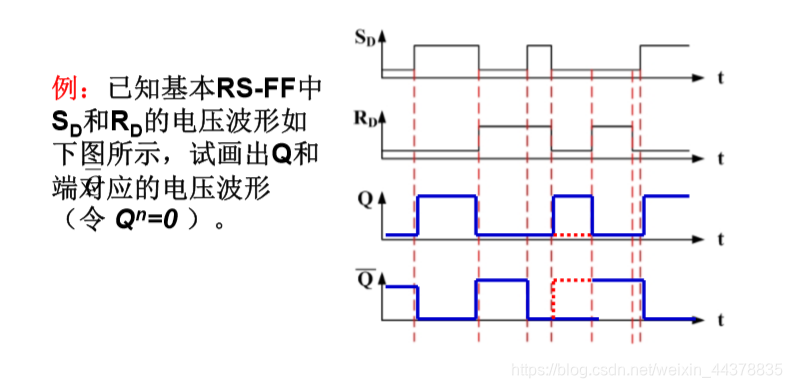

与非门构成的SR锁存器应用举例

红色虚线表示此段状态不定,可能1也可能0(前面为00输入)。

Q

′

n

Q'^n

Q′n稳定为0,所以

Q

n

+

1

Q_{n+1}

Qn+1稳定为1.

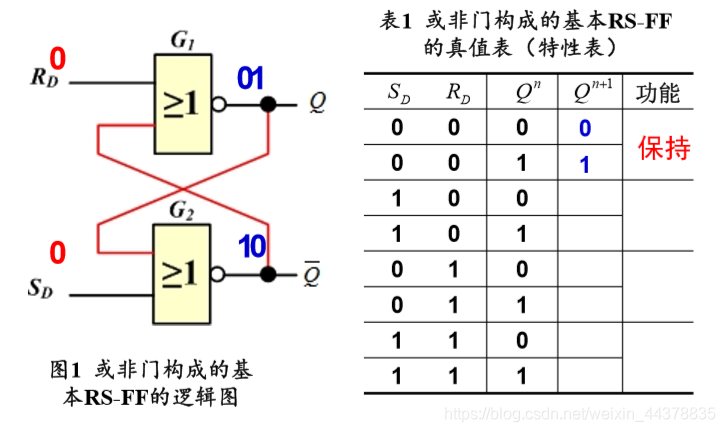

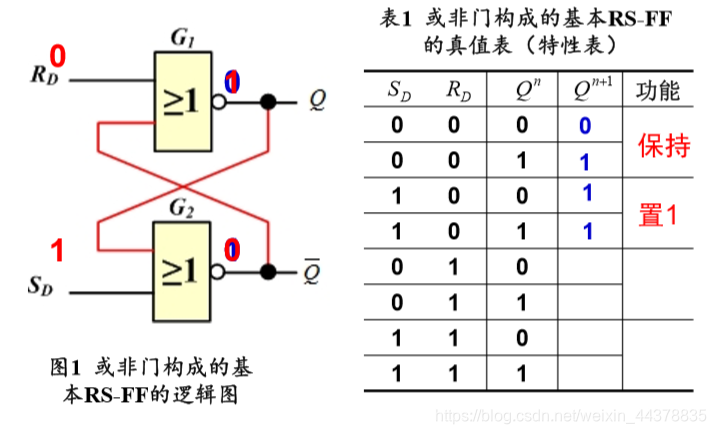

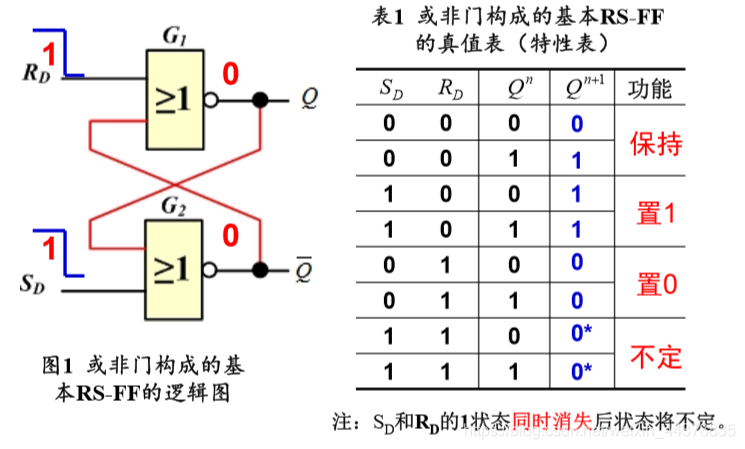

A.b.b 或非门构成的SR锁存器工作原理

输入高电平有效

|  |

|  |

或非门构成的SR锁存器特点

1 触发器新的状态

Q

n

+

1

Q_{n+1}

Qn+1(也叫次态)不仅与输入状态 有关,而且触发器原来的状态

Q

n

Q_n

Qn(也叫初态)有关;

2 由或非门构成的基本R-S触发器用 S D S_D SD和 R D R_D RD分别表示 “置1”输入端和“置0”输入端,它们均以高电平作为输入 信号;

3 由于

S

D

=

R

D

=

1

S_D=R_D=1

SD=RD=1时出现非定义的状态,而 且当

S

D

S_D

SD 和

R

D

R_D

RD 同时回到低电平以后触发器的状态难于确 定,因此正常工作时应遵守

S

D

R

D

=

0

S_DR_D=0

SDRD=0 的约束条件,即不 应加以

S

D

=

R

D

=

1

S_D=R_D=1

SD=RD=1的输入信号。

或非门构成的基本RS触发器描述

将

S

D

R

D

=

0

S_DR_D=0

SDRD=0作为输入约束条件,由卡诺图化简 可得或非门构成的基本RS-触发器的特性方程如下:

或非门构成的基本RS-触发器的图形符号如下:

4222

4222

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?