In the previous exercises, we used simple logic gates and combinations of several logic gates. These circuits are examples of combinational circuits. Combinational means the outputs of the circuit is a function (in the mathematics sense) of only its inputs. This means that for any given input value, there is only one possible output value. Thus, one way to describe the behaviour of a combinational function is to explicitly list what the output should be for every possible value of the inputs. This is a truth table.

For a boolean function of N inputs, there are 2N possible input combinations. Each row of the truth table lists one input combination, so there are always 2N rows. The output column shows what the output should be for each input value.

在前面的练习中,我们使用了简单的逻辑门和几个逻辑门的组合。这些电路是组合电路的例子。组合的意思是电路的输出只是它的输入的一个函数(在数学意义上)。这意味着对于任何给定的输入值,只有一个可能的输出值。因此,描述组合函数行为的一种方法是显式列出输入的每个可能值的输出。这是真值表。

对于一个有N个输入的布尔函数,有2N种可能的输入组合

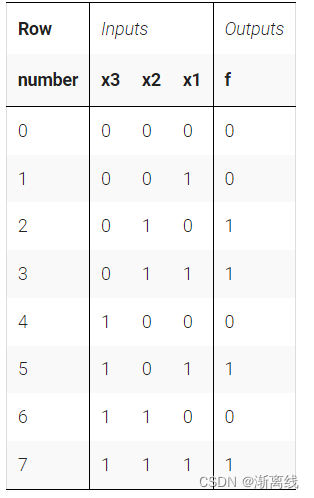

The above truth table is for a three-input, one-output function. It has 8 rows for each of the 8 possible input combinations, and one output column. There are four inputs combinations where the output is 1, and four where the output is 0.

上面的真值表是针对一个三输入一输出函数的。8个可能的输入组合中的每一个都有8行,还有一个输出列。有四个输出为1的输入组合,四个输出为0的输入组合

Synthesizing a circuit from a truth table

用真值表合成电路

Suppose we want to build the above circuit, but we’re limited to using only the set of standard logic gates. How would you build arbitrary logic functions (expressed as a truth table)?

One simple method to create a circuit that implements the truth table’s function is to express the function in sum-of-products form. Sum (meaning OR) of products (meaning AND) means using one N-input AND gate per row of the truth table (to detect when the input matches each row), followed by an OR gate that chooses only those rows that result in a ‘1’ output.

For the above example, the output is ‘1’ if the input matches row 2 or row 3 or row 5 or row 7 (This is a 4-input OR gate). The input matches row 2 if x3=0 and x2=1 and x1=0 (This is a 3-input AND gate). Thus, this truth table can be implemented in canonical form by using 4 AND gates that are ORed together.

假设我们想要构建上面的电路,但是我们被限制只能使用一组标准逻辑门。如何构建任意逻辑函数(表示为真值表)?

创建实现真值表功能的电路的一个简单方法是用乘积和的形式表示函数。乘积的和(意思是OR)(意思是AND)意味着在真值表的每一行使用一个n个输入与门(检测输入是否匹配每一行),后面跟着一个OR门,只选择那些导致输出“1”的行。

对于上面的示例,如果输入匹配第2行或第3行或第5行或第7行(这是一个4输入或门),则输出为’1’。如果x3=0和x2=1以及x1=0,则输入匹配第2行(这是一个3输入and门)。因此,这个真值表可以通过使用4个or的AND门以规范形式实现。

答案

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

//assign f = (x1&x2&x3) | (x1&x2&(~x3)) | ((x1)&x2&(x3)) | (x1&(~x2)&x3);

always@(*)

begin

case({x3,x2,x1})

3’b000,3’b001,3’b100,3’b110:f = 0;

3’b010,3’b011,3’b101,3’b111:f = 1;

default:f = 1’b0;

endcase

end

endmodule

429

429

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?