目标:

1.实现外在HDL code(手写)与simulink软件的交互。

2.实现HDL code(simulink生成的)与模块之间的再交互(Reusing components)。

3.实现subsystem子模块的熟悉使用。

耽误了一上午,现在开始!

Example one

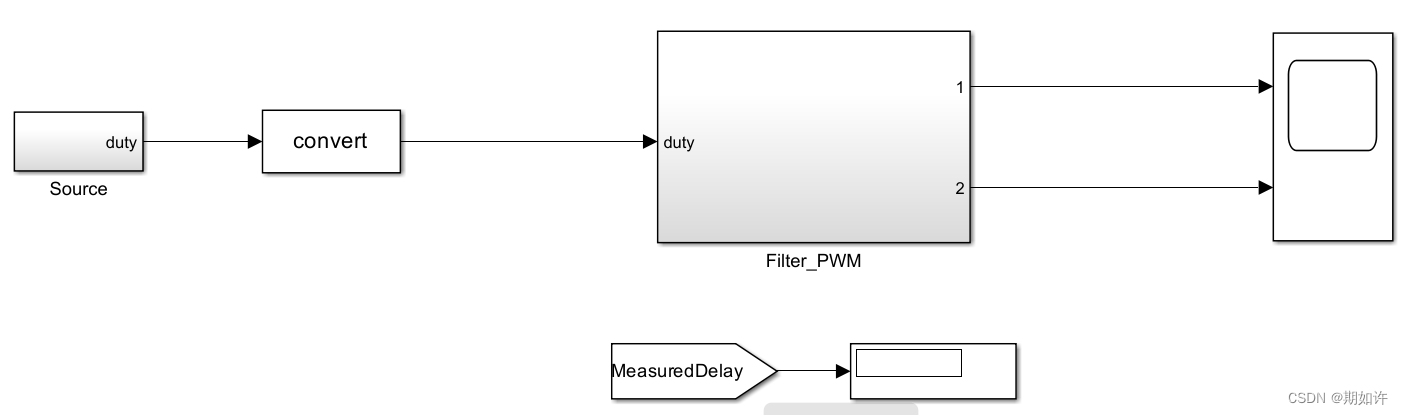

打开自带模块:“pmsm_driver” 并且run it

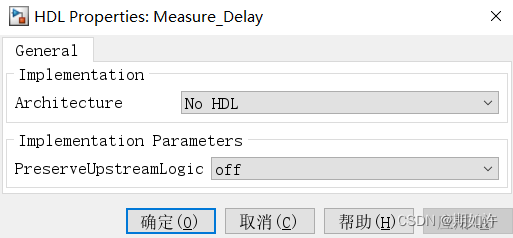

有个MeasureDelay模块报错,所以我们将这个模块设置为 no HDL,这样就ignore it!

Exmaple Two

如何生成a Black Box Interface from a Subsystem?

在子系统中添加subsystem模块,选择blackbox模式即可。

再在subsystem模块中添加HDL语言,clk、reset、enable都是默认的,但是名字需要自己校对一下,并且reset上下沿触发必须仔细看看,然后点击生成HDL模型即可。

理解:The code within the docblock is independent of the original code.

注意:在FIR模块中,有许多的重复子模块相乘,比如滤波器系数,那么这个时候可以将各个Area转变为原子子系统,再继续封装,只需要将参数表述一致,但是每个Stage可以设置不一样。例如:第一个C=1;第二个C=2;第三个C=3;

最终生成HDL Code 的话就会将所有Stage的v文件,个数减少到1个Stage文件,不会改变程序最后的逻辑结果。

全局配置:Global Settings里面设置Coding Style,勾选产生HDL从masked subsystem中(封装系统)。

总结:可靠性不高,不如尝试System Generator功能。

5597

5597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?