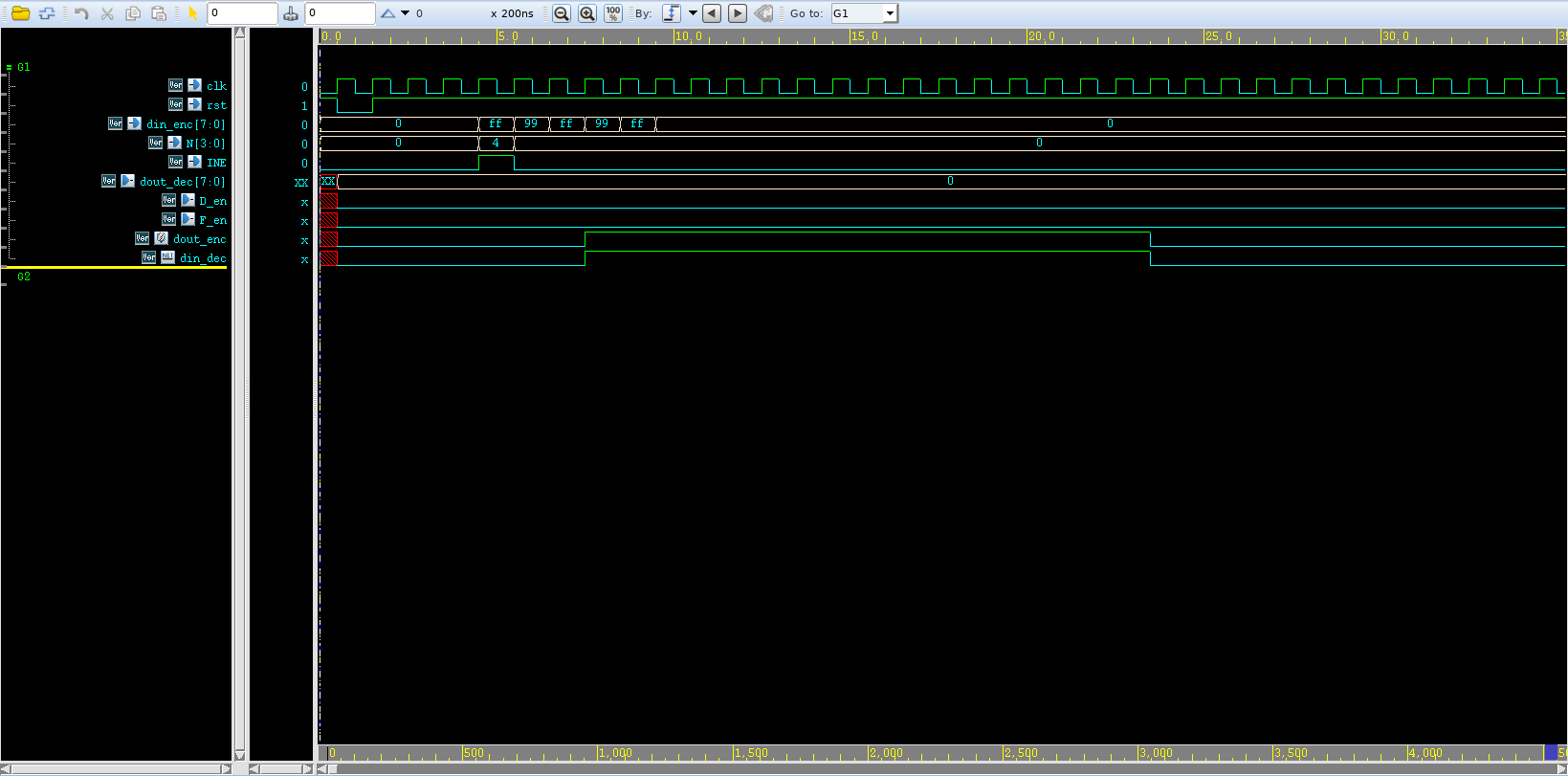

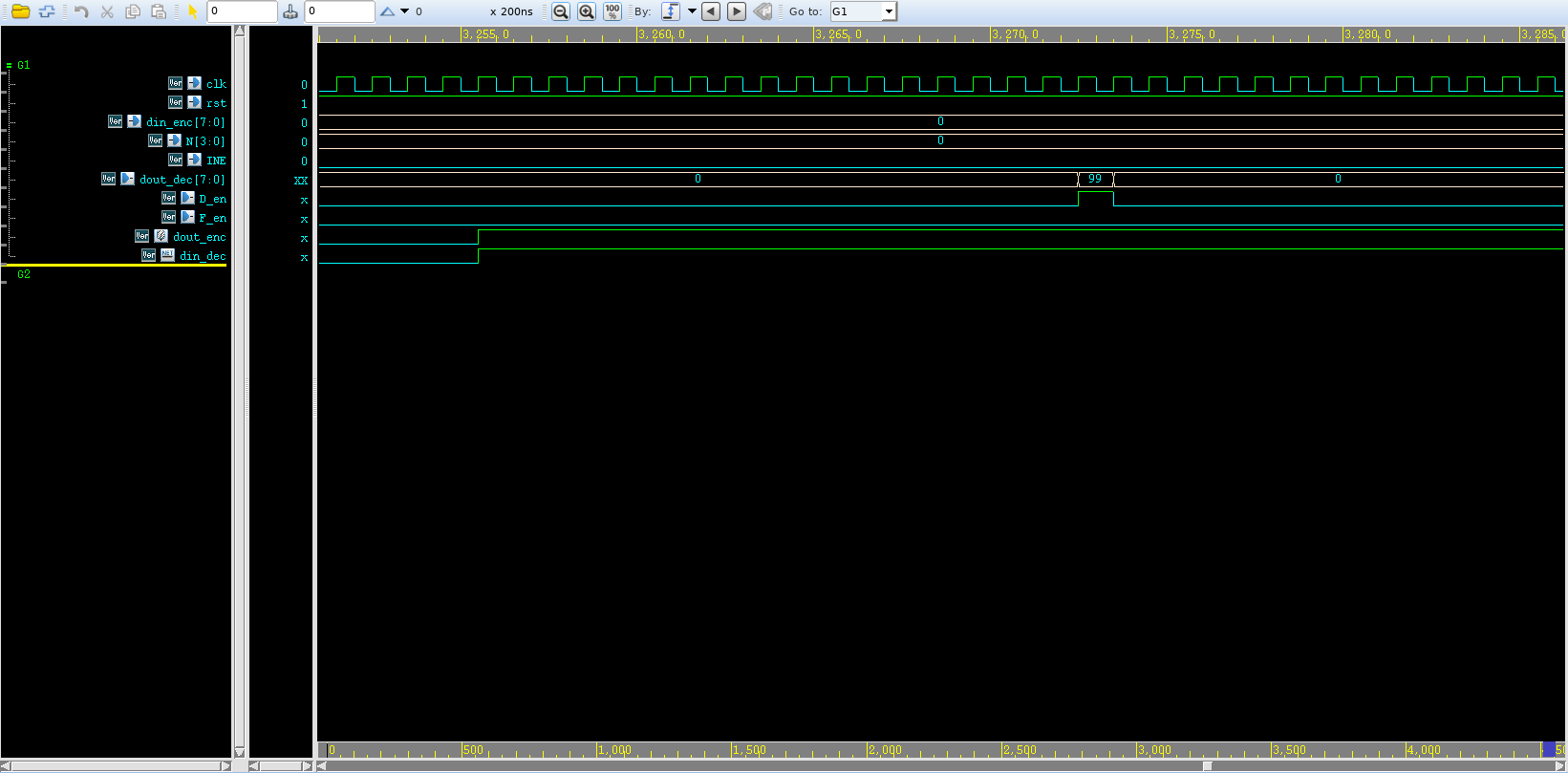

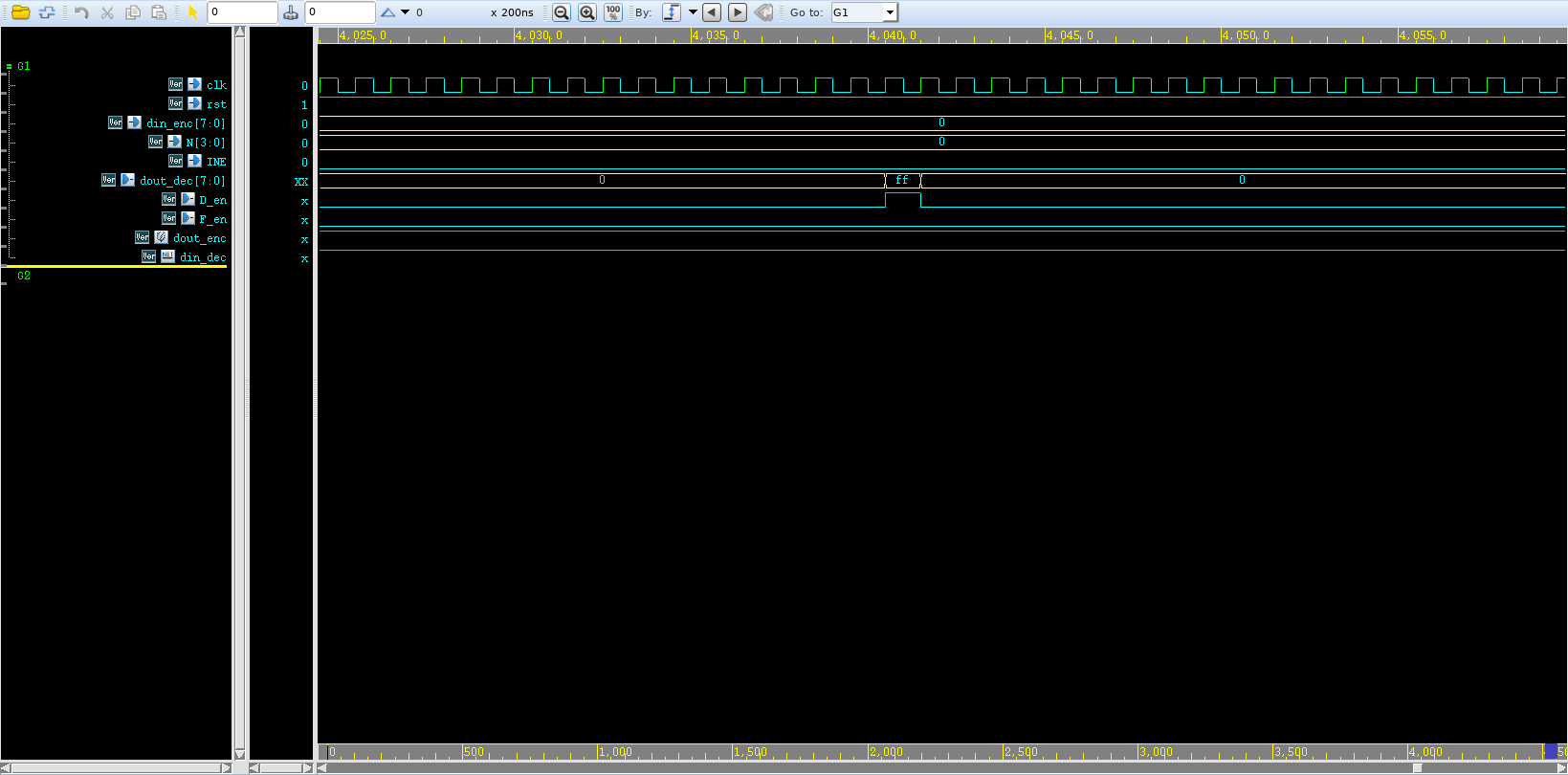

PCM_ENC_DEC_TEST_5.v

`timescale 10ns/1ps

module PCM_ENC_DEC_TEST_5;

reg clk;

reg rst;

reg [7:0] din_enc;

reg [3:0] N;

reg INE;

wire [7:0] dout_dec;

wire D_en;

wire F_en;

parameter half_cycle = 10;

PCM_ENC_DEC ut5

(

.clk(clk),

.rst(rst),

.din_enc(din_enc),

.N(N),

.INE(INE),

.dout_dec(dout_dec),

.D_en(D_en),

.F_en(F_en)

);

initial begin

clk = 0;

forever begin

clk = # half_cycle ~ clk;

end

end

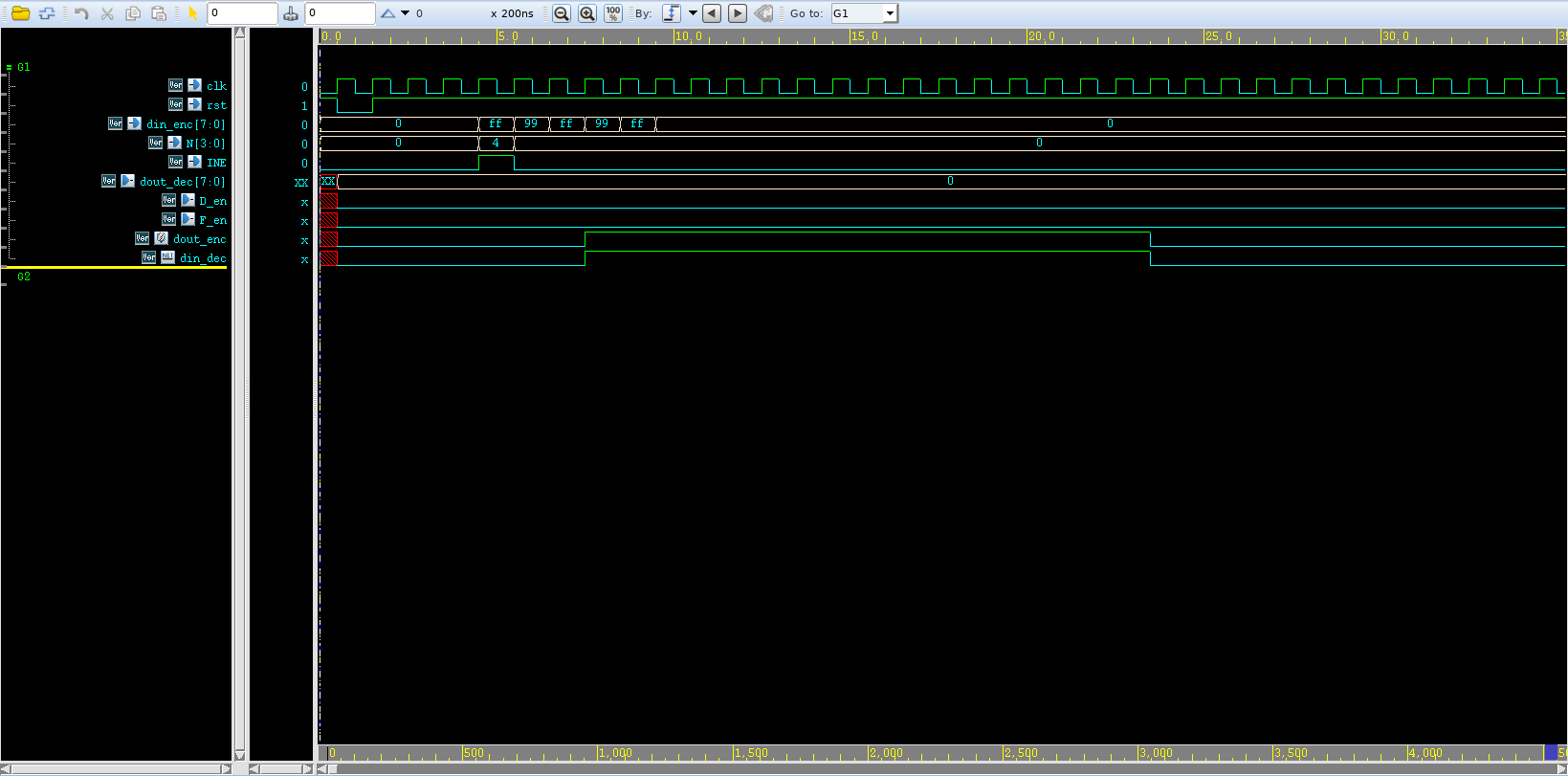

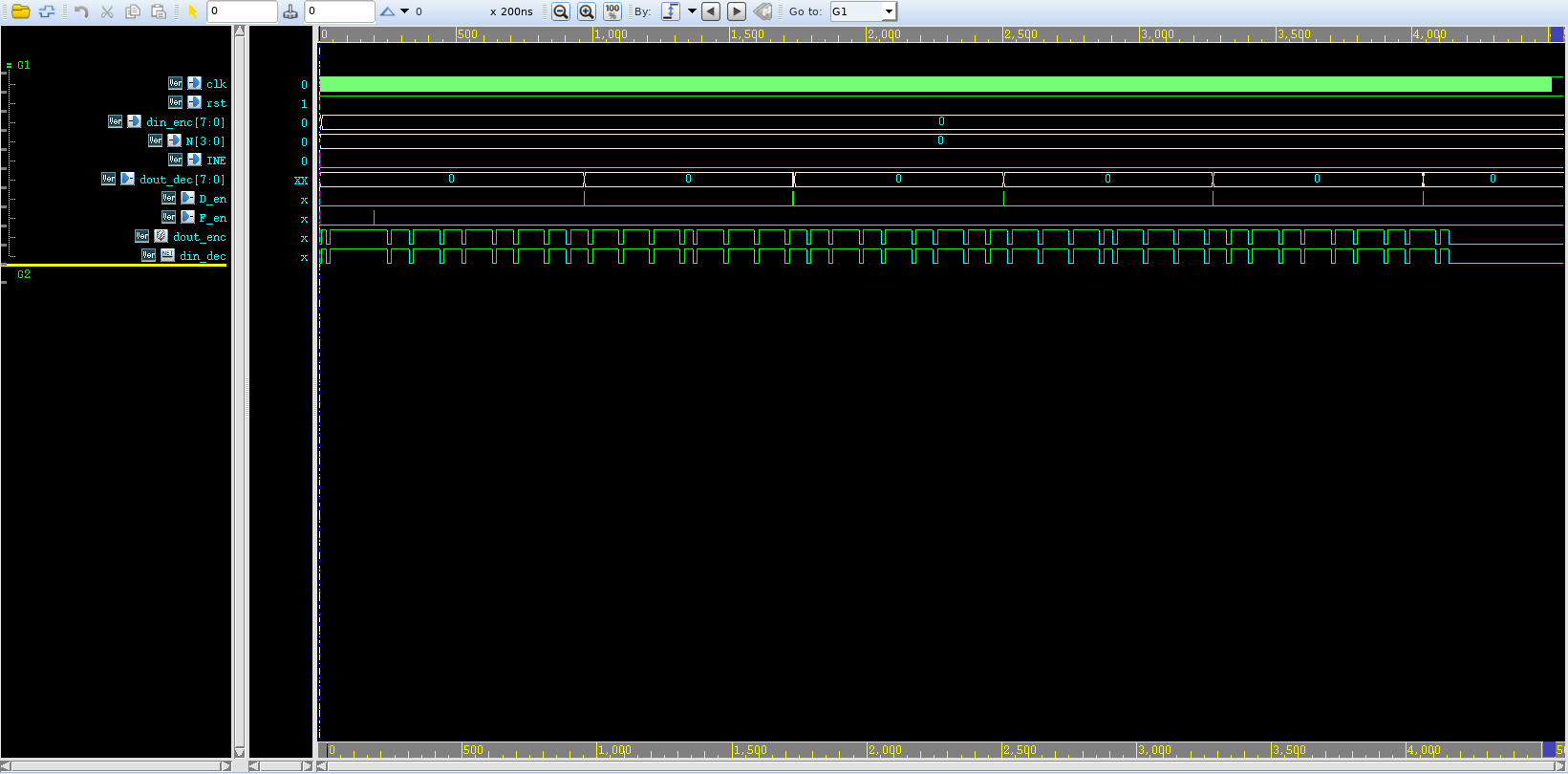

initial begin

rst = 1;

# (1 * half_cycle) rst = 0;

# (2 * half_cycle) rst = 1;

end

initial

din_enc <= 0;

N <= 0;

INE <= 0;

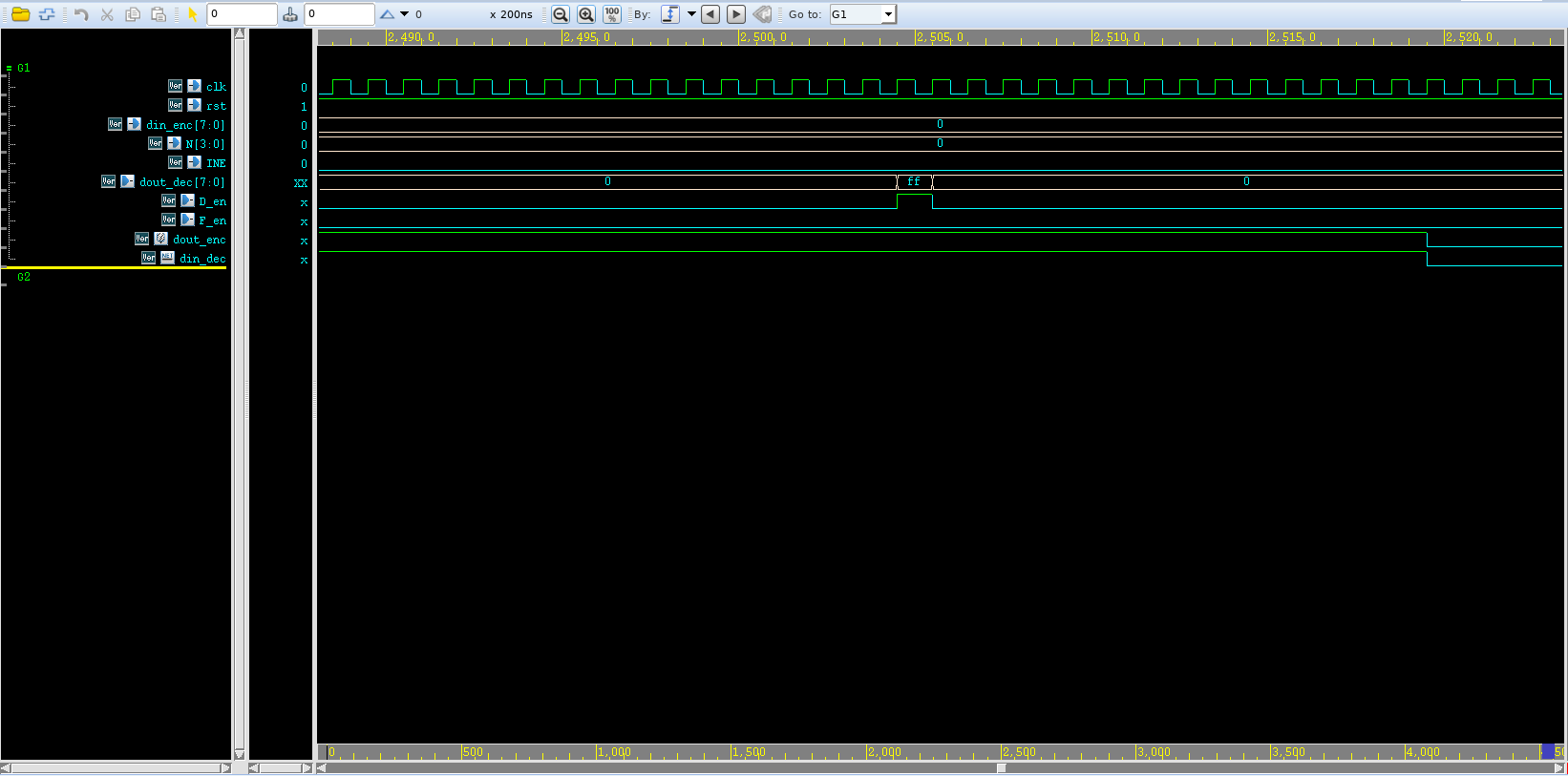

repeat (5) @ (posedge clk);

din_enc <= 8'hFF;

N <= 4'd4;

INE <= 1;

repeat (1) @ (posedge clk);

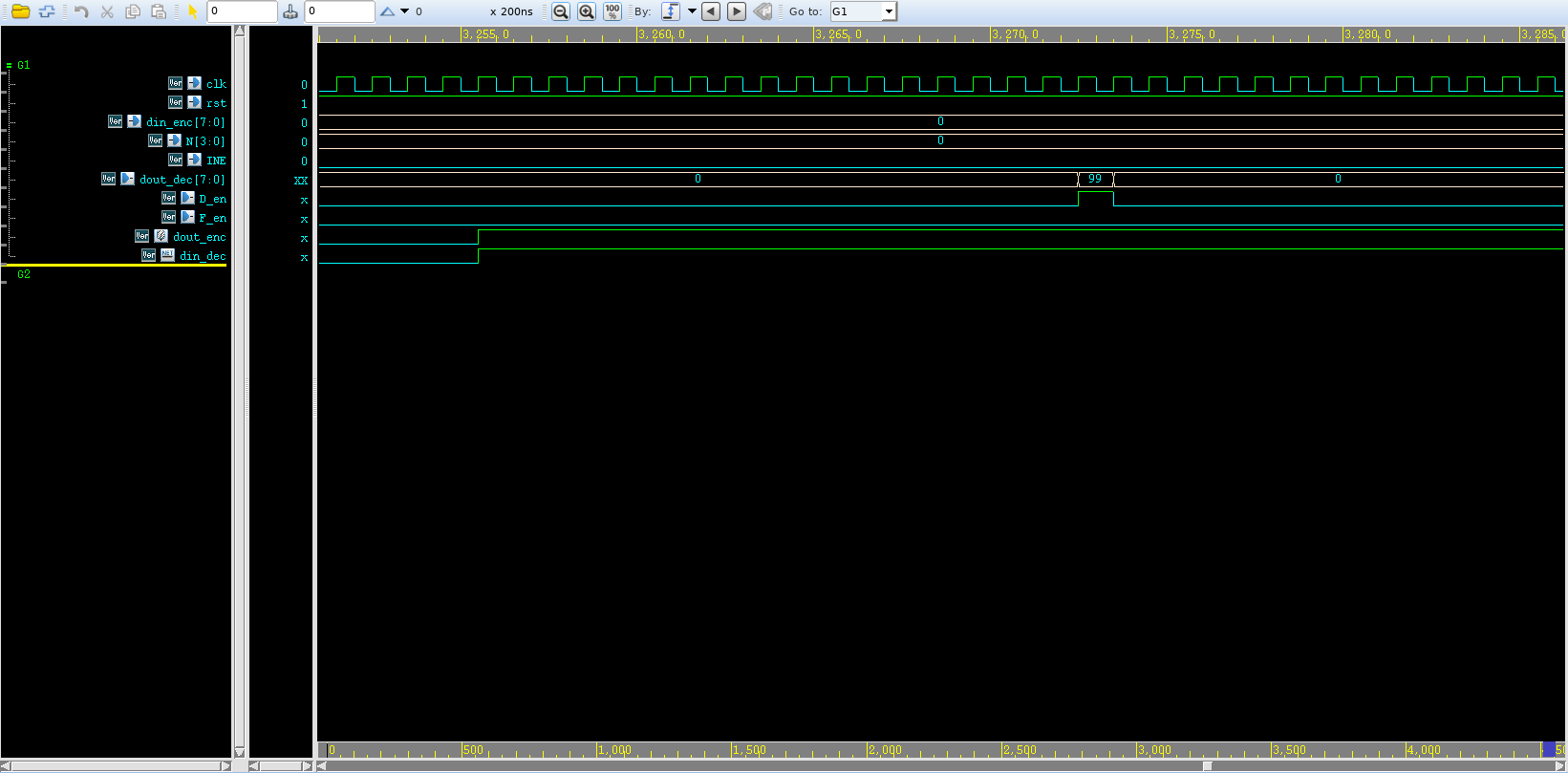

din_enc <= 8'h99;

N <= 0;

INE <= 0;

repeat (1) @ (posedge clk);

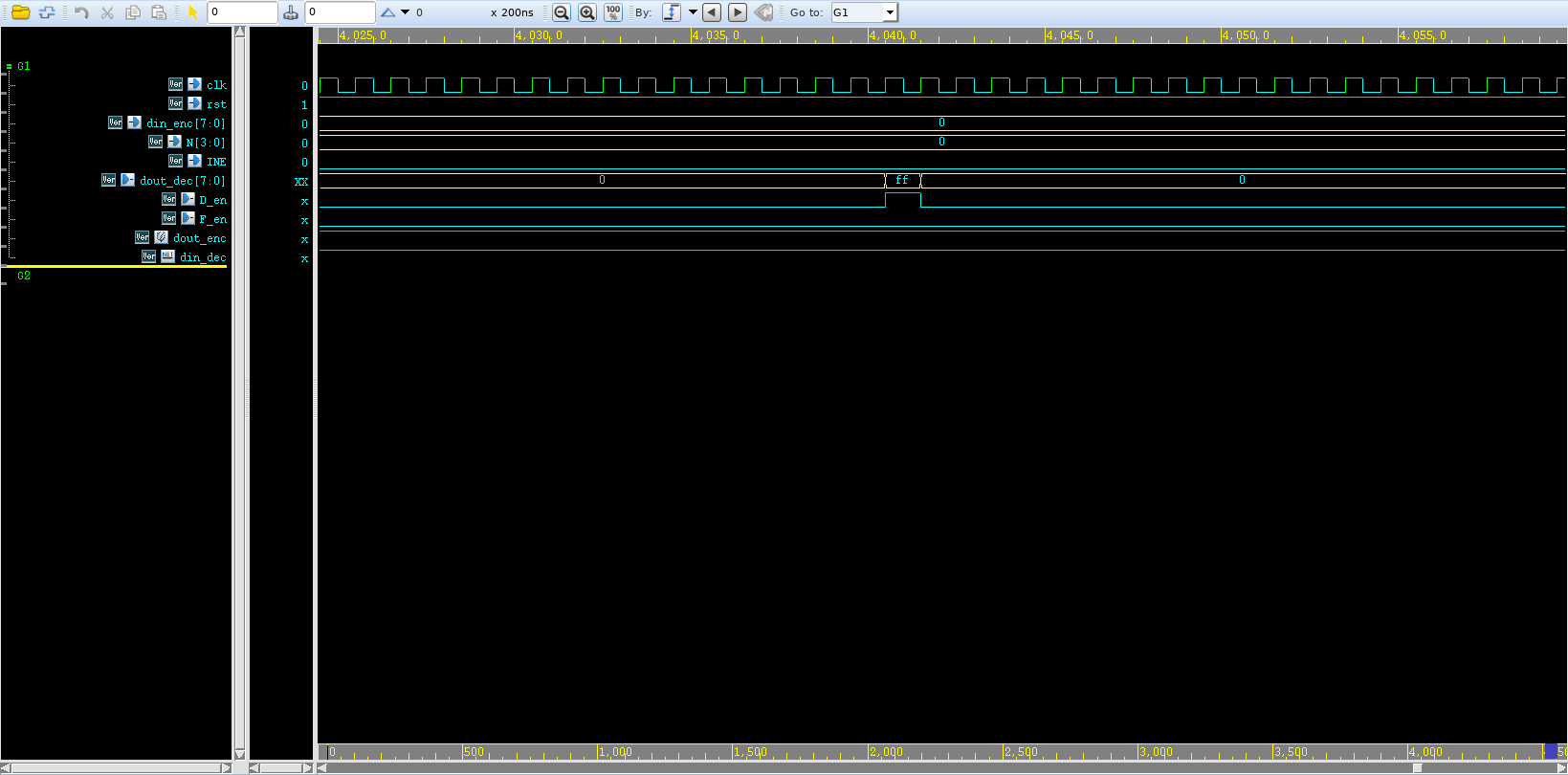

din_enc <= 8'hFF;

repeat (1) @ (posedge clk);

din_enc <= 8'h99;

repeat (1) @ (posedge clk);

din_enc <= 8'hFF;

repeat (1) @ (posedge clk);

din_enc <= 0;

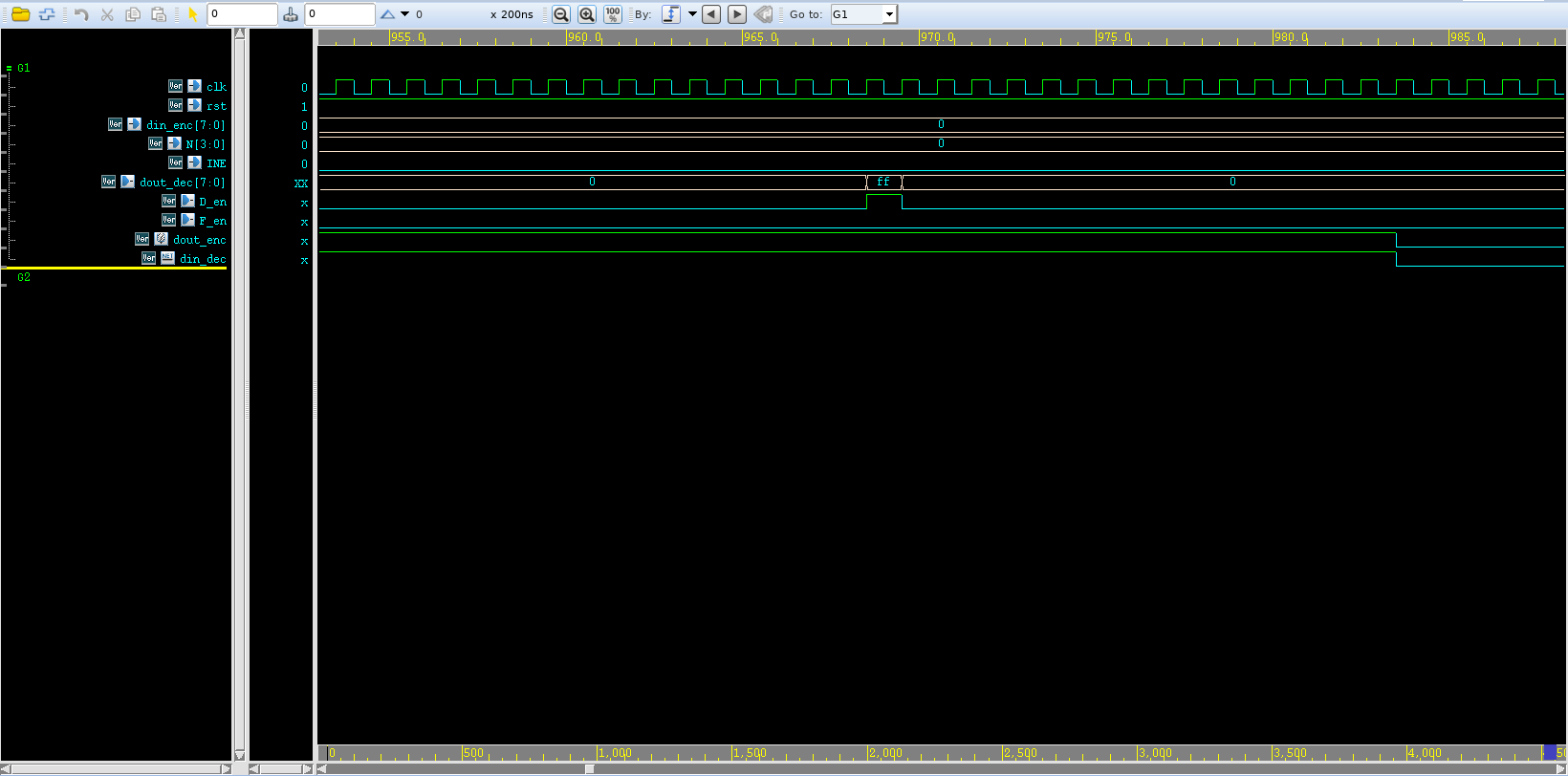

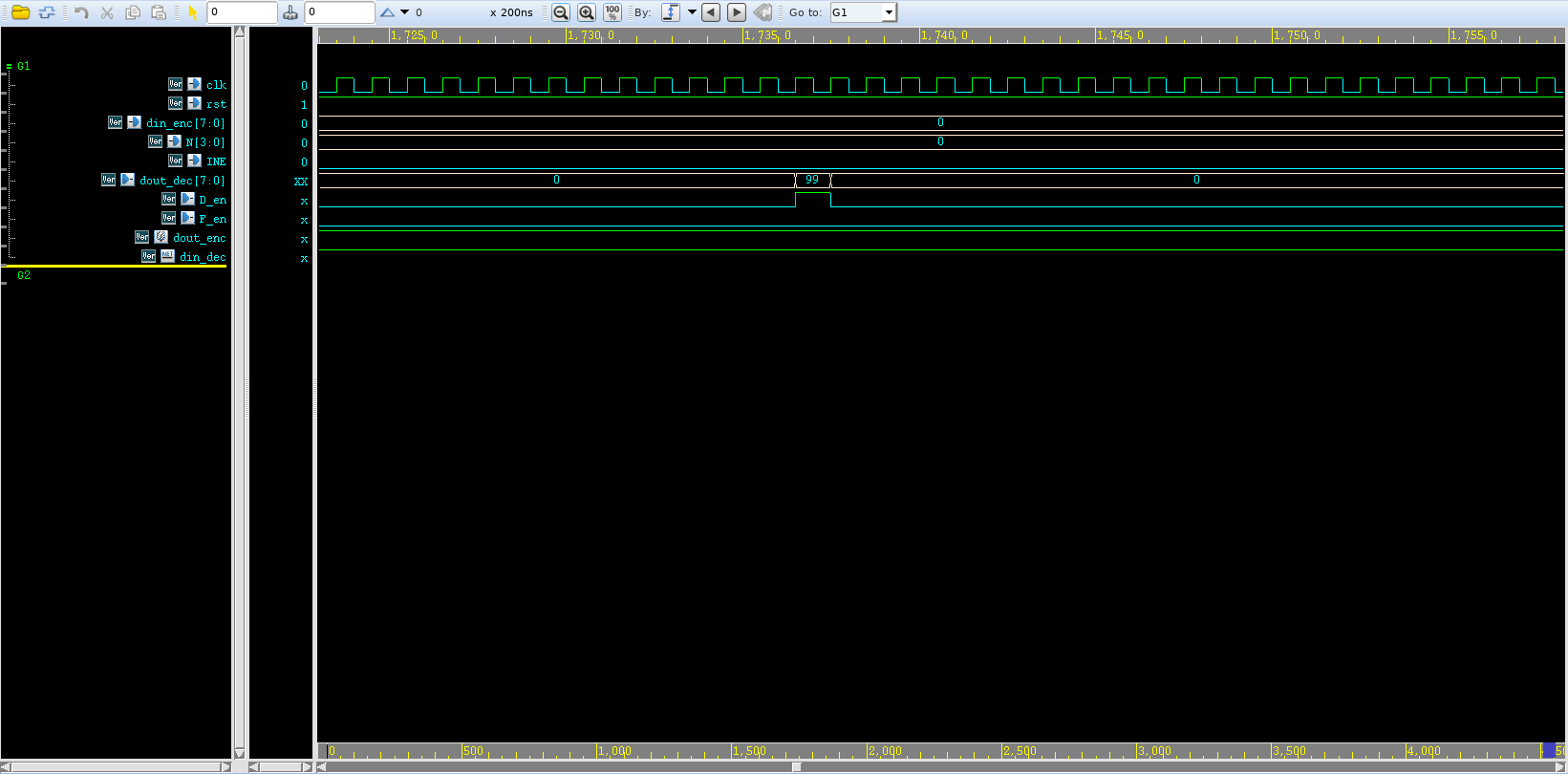

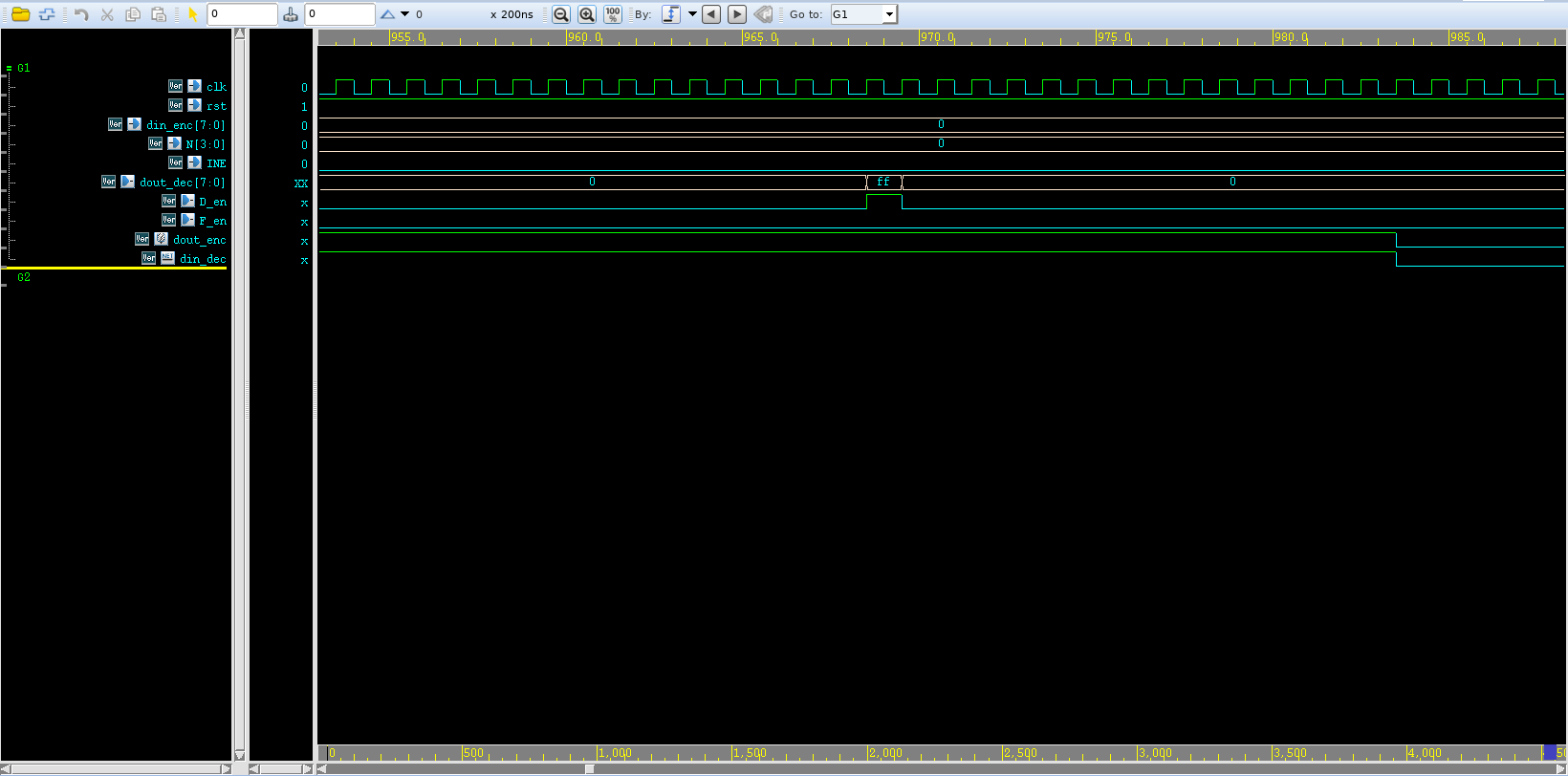

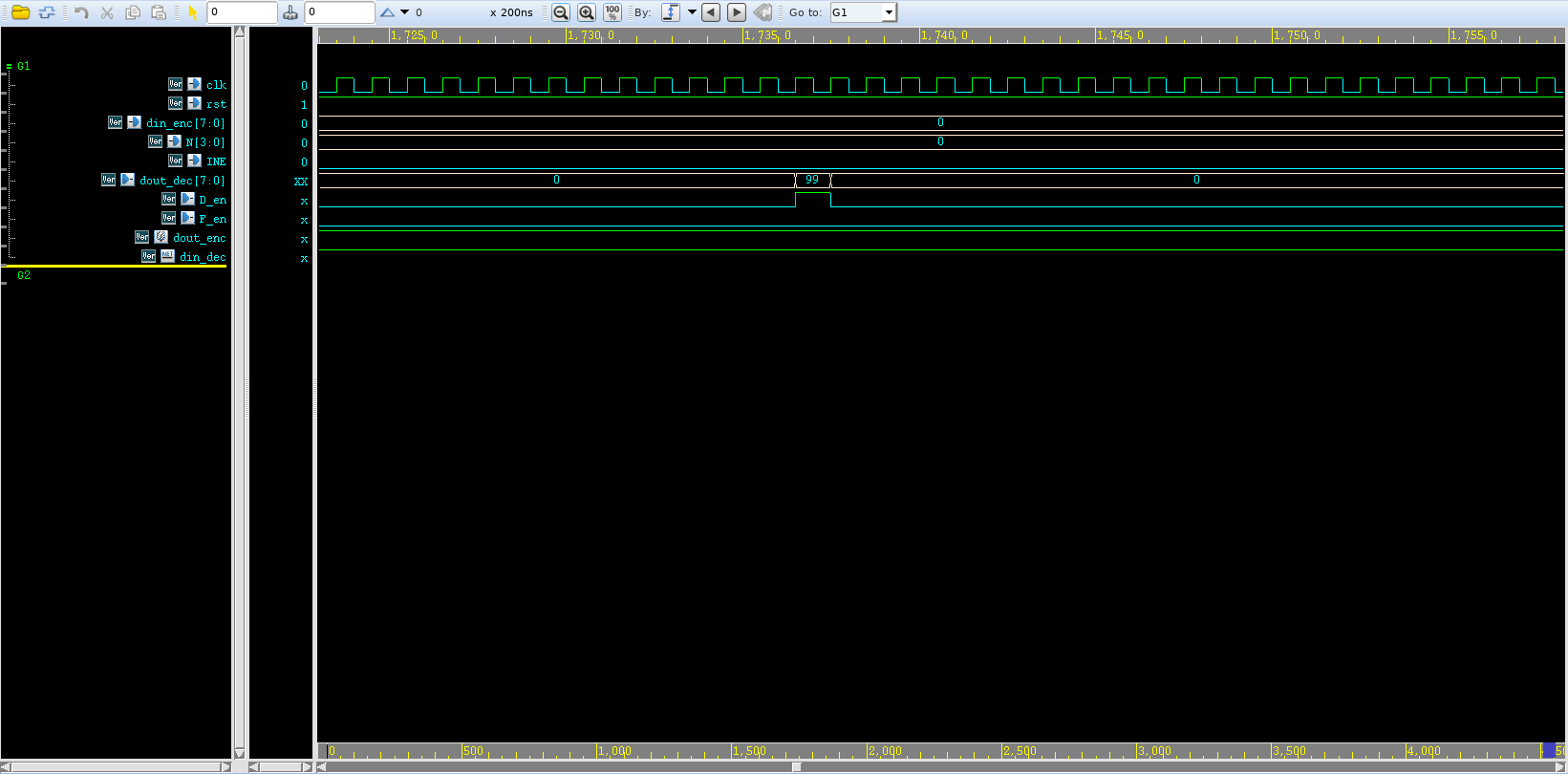

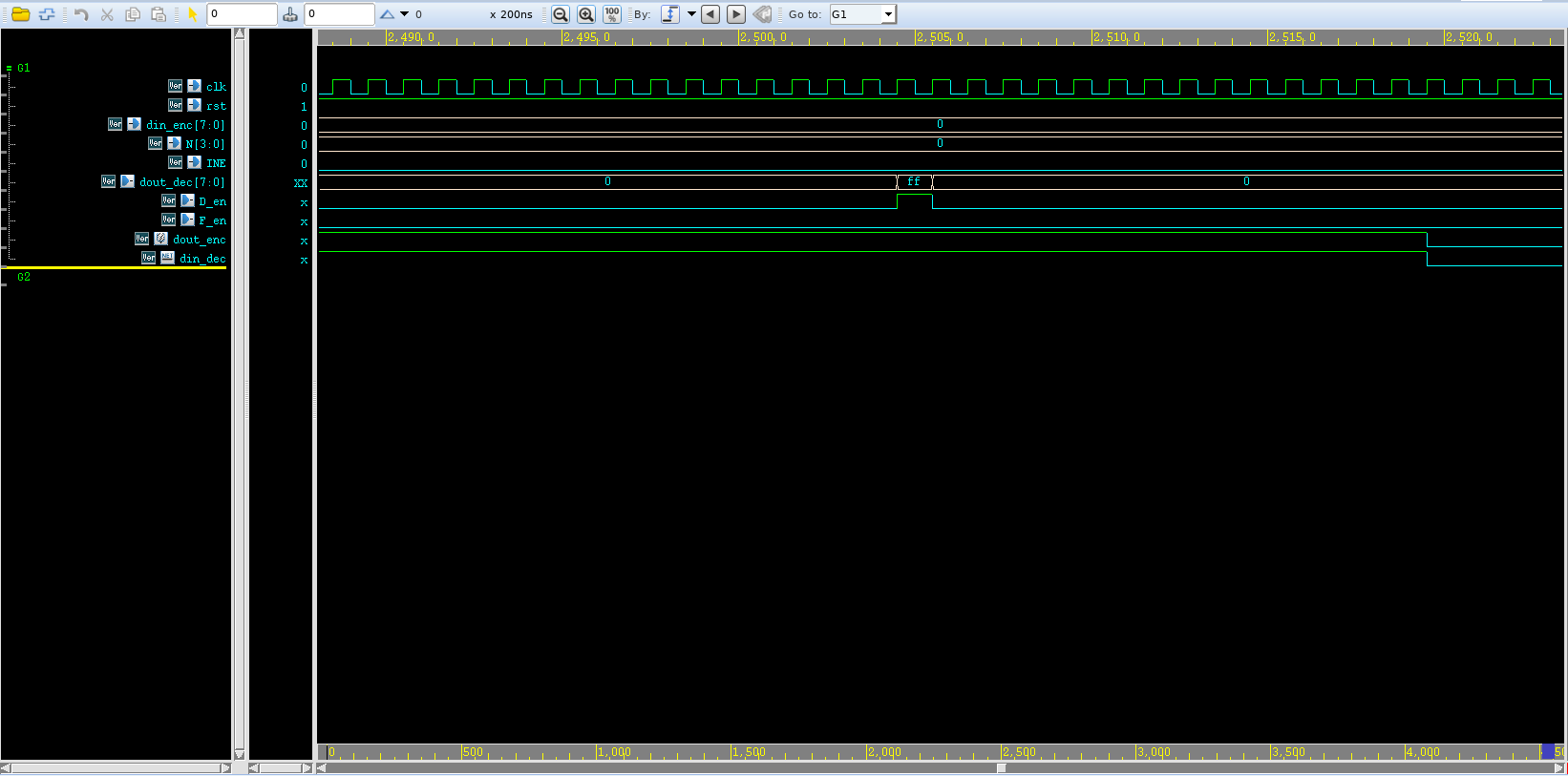

repeat (4500) @ (posedge clk);

$finish;

end

initial begin

$fsdbDumpfile("./verdiFsdb/PCM_ENC_DEC_TEST_5.fsdb");

$fsdbDumpvars(0);

end

endmodule

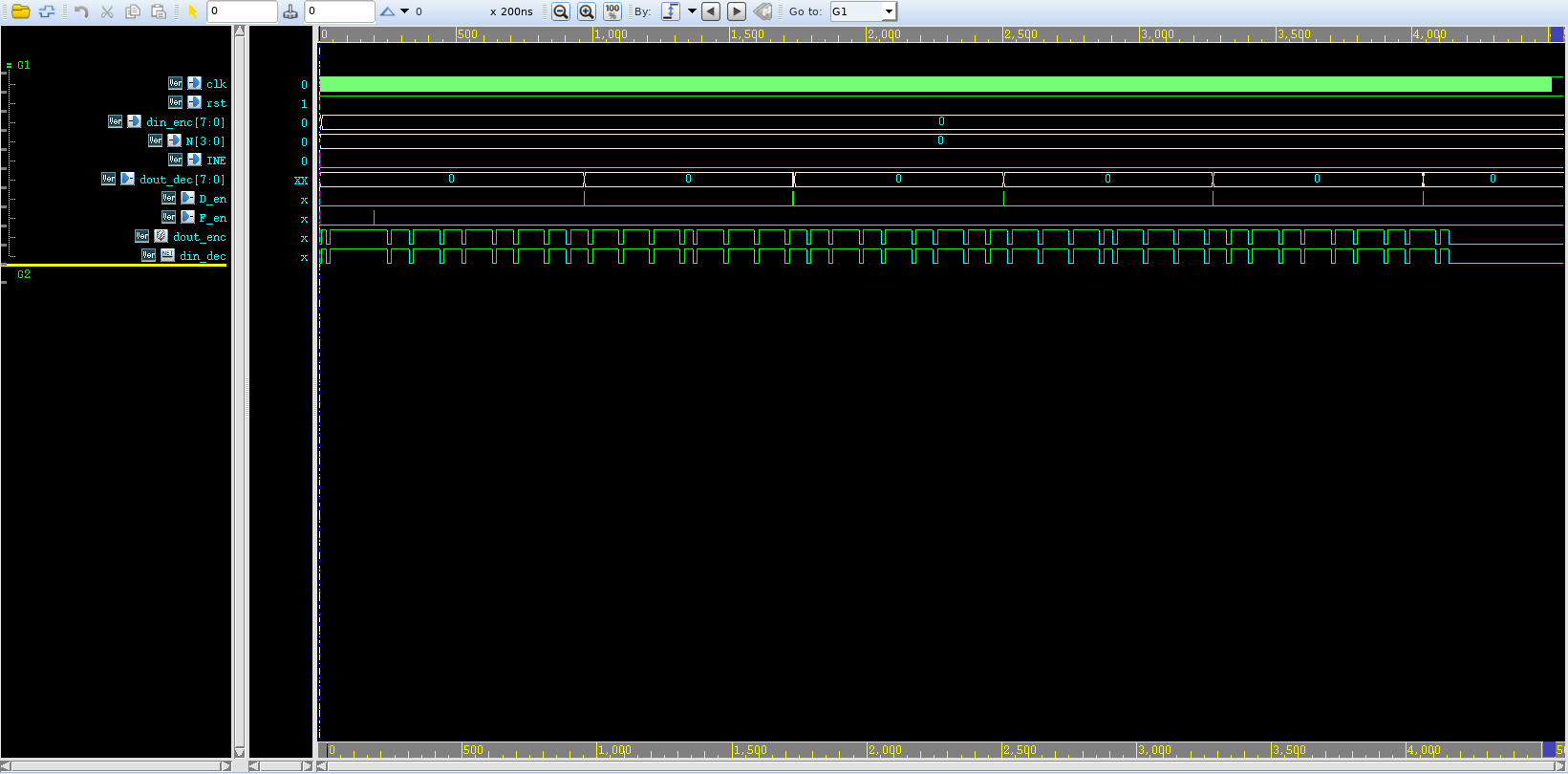

Experiment Result

1359

1359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?