DDR4 Multi Purpose Register (MPR)

我是谁?—— MPR 简介

MRP 其实是物理上真是存在的寄存器,简单理解就是存储 0/1 的器件。所以啊,它设计时,是独立于 cell 存在的器件,使用它不经过 cell。

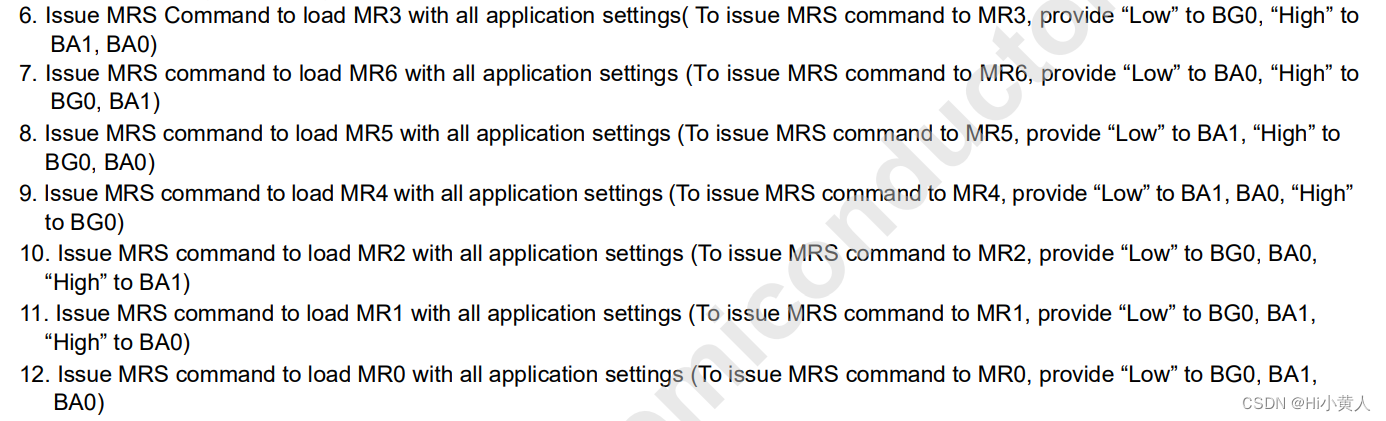

MPR 是内存初始化过程中最靠前的动作,在加载完 MRx (MR0 / MR1 / MR2… / MR6,见图1) 的配置之后,就是进行 MPR 的初始化。

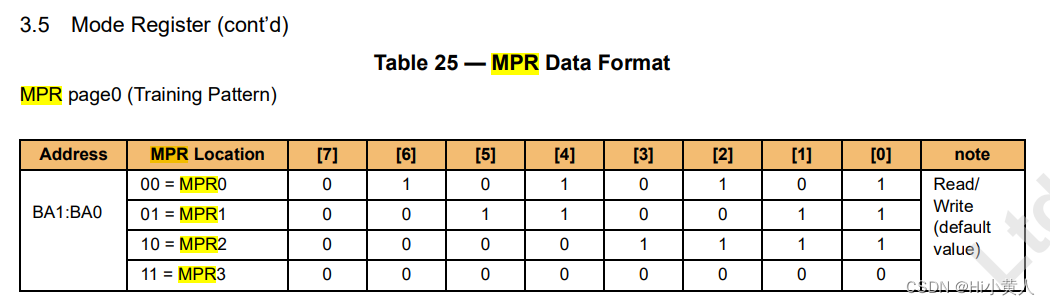

MPR 读取时,需要选取读取的位置 (page & location,见图 2).

MPR 有 4 个 page,page0 是内存原厂在设计时,按照 JEDEC 定义的规范设计好的值,page1/2 是需要根据其它 MRx 的配置设置的值,page3 一般是给 DRAM 原厂使用的,不必在意。一般的 CPU 厂商,都是根据 page0 进行 training 的。page1/2 如果不是在 DRAM 原厂工作,就不用去了解了。

Location 呢,只是存储的数据顺序不同而已

MPR 其存在的目的:Read 时,需要将 DQ 的判定 High/Low 的电压设定在一个理想的值,MPR操作时,读取的数据从寄存器给出,可以避免 cell 问题导致读取数据错误,MPR 就是进行 Read 时 DQ 数据线的 training,确保后续的读写可以正常进行。

图 1:MRx 的加载顺序为 MR3 / 6 / 5 / 4 / 2 / 1 / 0 (From JESD79 - 4C)

图 2:下图为 page0 / location 0 ~ 3,[0-7] 表示 burst 的数据顺序,比如 location 0 的数据burst 形式为 1/0/1/0/1/0/1/0

怎么使用我 —— MPR 设置

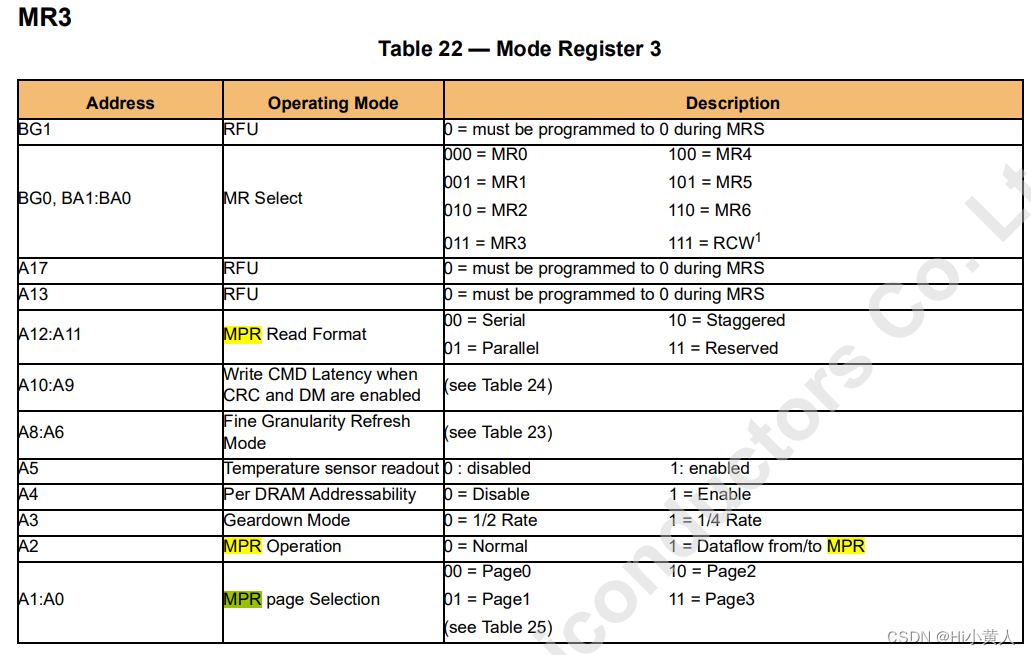

MPR 可以通过 MR3 [A2] 进行 开启 (set to 1, dataflow from/to MPR) 或 关闭 (0, Normal 即 disable).

利用 MR3 [A1:A0] 选择 MPR 的 page

图 3:

暴躁的我写不下去了,今天先这样,拜拜!

923

923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?