定义

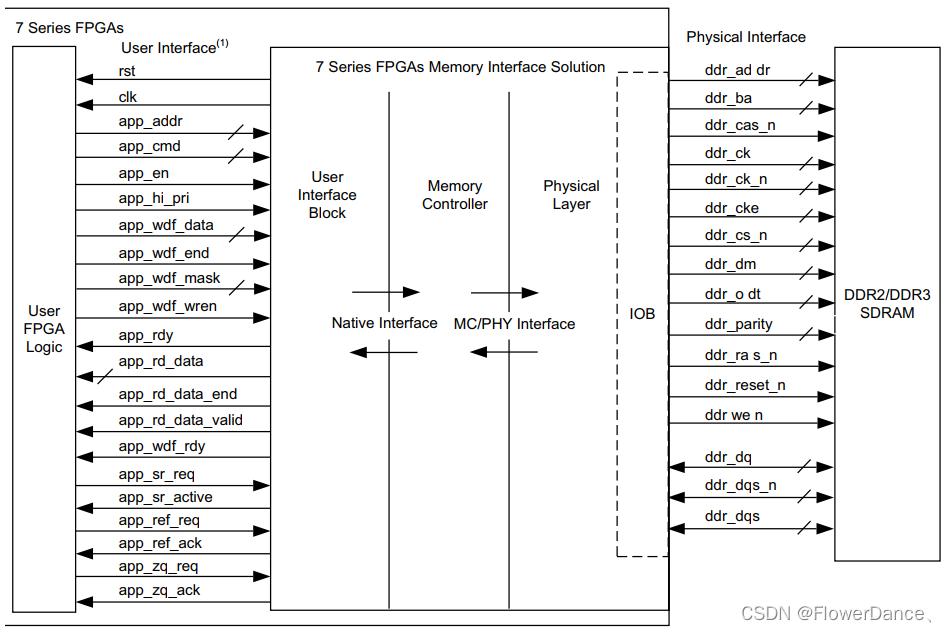

MIG IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的控制流程,下图是 7 系列的 MIG IP 核结构框图。 MIG IP 核对外分出了两组接口。左侧是用户接口,就是用户( FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。右侧为 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。这一侧用户只负责分配正确的管脚,其他不用关心。表中标明的信号的方向是以 MIG IP 核作为参照的。

用户接口

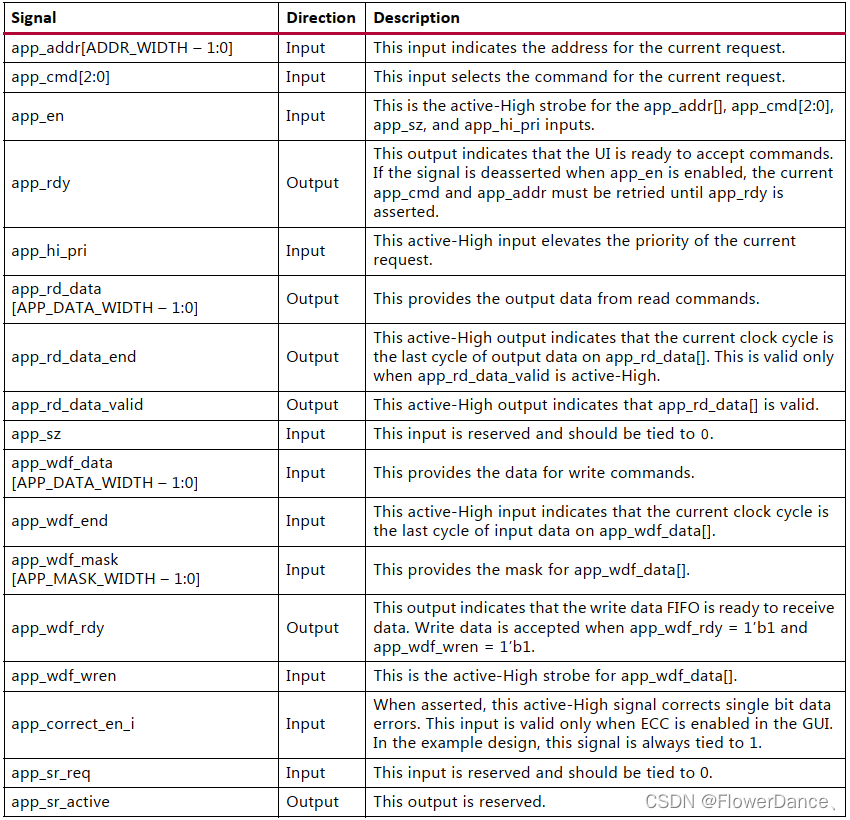

| 信号名 | 方向 | 端口说明 |

|---|---|---|

| ui_clk | output | 用户时钟,由MIG IP核输出,必须是DRAM时钟的四分之一 |

| ui_clk_sync_rst | output | 复位,由MIG IP核提供,高电平有效 |

| app_addr[ADDR_WIDTH–1:0] | input | 用户地址输入,这是MIG IP核根据具体的物理芯片,整合给用户使用的地址空间,这个地址和芯片的地址是对应的,地址的位宽ADDR_WIDTH等于BANK位宽+ ROW位宽 + COL位宽 |

| app_cmd[2:0] | input | 读写控制命令。读: 001;写: 000。其他值保留 |

| app_en | input | MIG IP核命令写入使能,高有效。写命令时需要拉高该信号 |

| app_rdy | output | 表示UI已经准备好接收命令,高电平有效。如果当app_en使能时,该信号未拉高,那么当前的app_amd和app_addr信号必须保持直到app_rdy拉高 |

| app_hi_pri | input | 表明当前请求具有高优先级 |

| app_rd_data[APP_DATA_WIDTH–1:0] | output | 该信号用于用户读取IP核发来的数据,位宽同样设置为128。 |

| app_rd_data_end | output | 高电平有效,表明当前时钟周期是app_rd_data输出数据的最后一个周期。只有当app_rd_data拉高时该信号才有效 |

| app_rd_data_valid | output | 读数据有效信号,高电平有效。 |

| app_wdf_data[APP_DATA_WIDTH-1:0] | input | 该信号为用户写数据输入 |

| app_wdf_end | input | 当前时钟是突发写过程的最后一个时钟,高电平有效。 |

| app_wdf_mask[APP_MASK_WIDTH-1:0] | input | 为app_wdf_data提供掩码 |

| app_wdf_rdy | output | MIG IP核数据接收准备完成,高电平有效。写数据只有当app_wdf_rdy和app_wdf_wren同时拉高时才会被接收 |

| app_wdf_wren | input | MIG IP核数据写使能,高电平有效。写数据时需要拉高该信号。 |

| init_calib_complete | output | 高电平有效,表明校准完成 |

| app_sz | input | 此输入是保留的,应绑定到0。 |

| app_correct_en_i | input | 当拉高时,该有效的高信号校正单比特数据错误。只有当在GUI中启用ECC时,此输入才有效。在示例设计中,该信号总是与1绑定。 |

| app_sr_req | input | 该信号被保留并且应绑定到0 |

| app_sr_active | output | 被保留 |

| app_ref_req | input | 刷新命令请求,高电平有效。请求向DRAM发送刷新命令 |

| app_ref_ack | output | 高电平有效,刷新请求应答信号,表明Memory Controller已经将刷新命令发送给了PHY interface |

| app_zq_req | input | 高电平有效,表明请求向DRAM发出ZQ校准命令 |

| app_zq_ack | output | 高电平有效,表明Memory Controller已经将ZQ校准命令发送给了PHY interface |

| app_ecc_multiple_err[7:0] | output | 当ECC使能时有效 |

| app_ecc_single_err[7:0] | output | 当ECC使能时有效 |

时序图

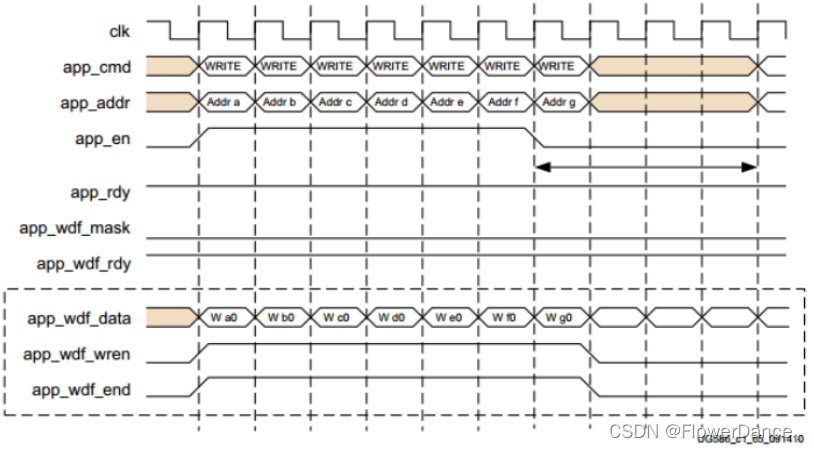

写指令时序

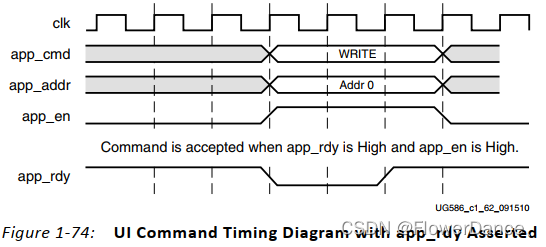

如下图所示。首先检查 app_rdy,为高则表明此时 IP 核命令接收处于准备好状态,可以接收用户命令,在当前时钟拉高 app_en,同时发送命令( app_cmd)和地址( app_addr),此时命令和地址被写入。

当用户逻辑app_en信号拉高并且来自UI的app_rdy信号拉高时,指令被接收并且被UI写进FIFO中。当app_rdy拉低时,指令被UI忽视(即指令无效),用户逻辑需要保持app_en为高电平伴随着有效的指令和地址直到app_rdy被拉高。(app_en和app_rdy需要进行握手,指令才有效)

写数据时序

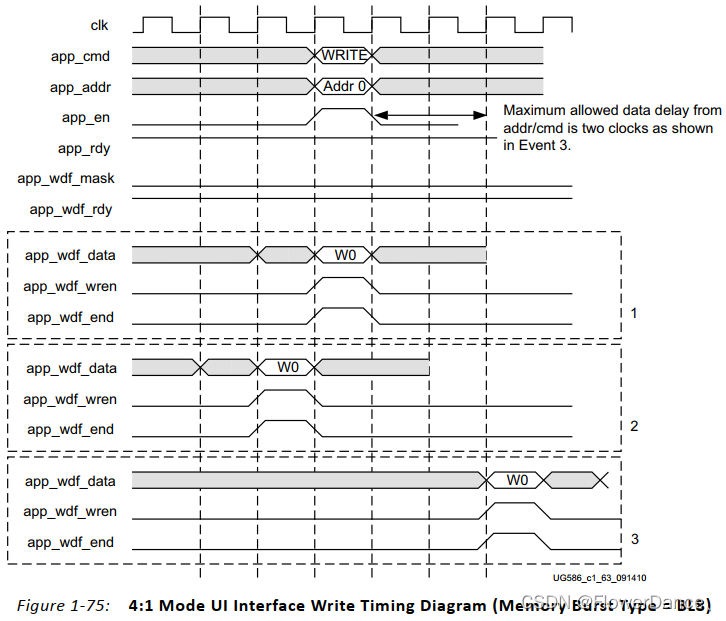

如上图所示,写数据有三种情形均可以正确写入:

(1)写数据时序和写命令时序发生在同一拍;

(2)写数据时序比写命令时序提前一拍;

(3)写数据时序比写命令时序至多延迟晚两拍;

写数据总结:首先需要检查app_wdf_rdy,该信号为高表示此时IP核可以接收数据。在当前时钟拉高写使能( app_wdf_wren),给出写数据

(app_wdf_data)。这样加上发起的写命令操作就可以成功向 IP 核写数据。这里有一个信号 app_wdf_mask,它是用来屏蔽写入数据的,该

信号为高则屏蔽相应的字节, 该信号为 0 默认不屏蔽任何字节。

DDR3 的读或者写操作都可以分为背靠背和非背靠背两种情形。背靠背,即读或者写每个时钟都连续进行,中间没有间隙。

非背靠背写则是非连续的读写。对于背靠背写,其实也有三种情形,唯一点不同的是,它没有最大延迟限制,如下图所示。

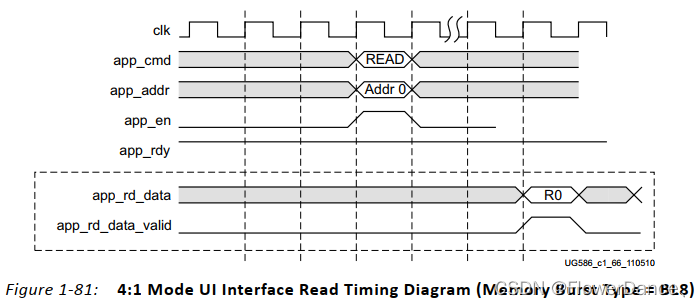

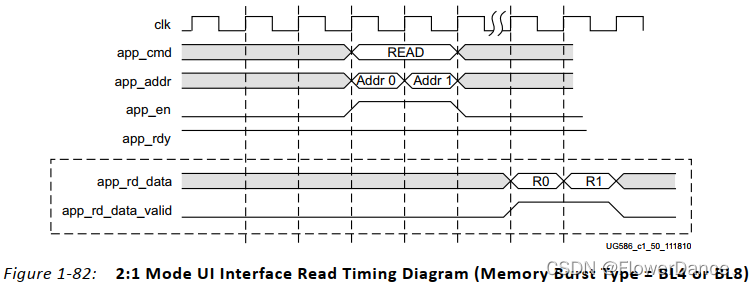

读数据时序

读时序比较简单,发出读命令后,用户只需等待数据有效信号( app_rd_data_valid)拉高, 为高表明此时数据总线上的数据是有效的返回数据

需要注意的是,在发出读命令后,有效读数据要晚若干周期才出现在数据总线上。

这里还需要注意一点,在连续读的时候,读到的数据顺序跟请求的命令/地址是相对应的。通常使用DDR3 的时候,为了最大限度地提高 DDR3

效能,充分利用突发写的特点,非背靠背很少用,而更多地采用背靠背操作。

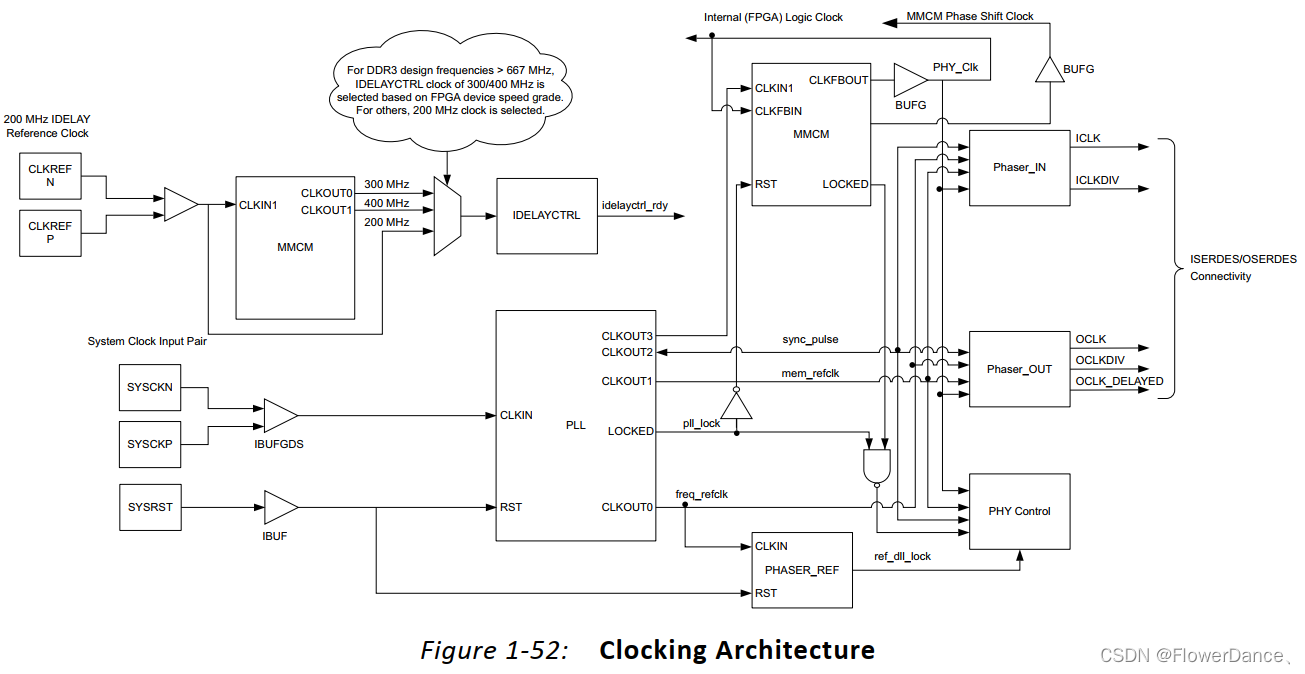

MIG IP内部的时钟架构

- Internal(FPGA)logic clock

内部FPGA逻辑由全局时钟资源以DDR2或DDR3 SDRAM时钟频率的一半或四分之一频率计时,这取决于在MIG工具中选择的4:1或2:1模式。该PLL还输出高速DDR2或DDR3内存时钟。 - Write Path(output)I/O logic

数据和控制的输出路径的时钟由PHASER_OUT提供 - Read path (input)and delay I/O logic

输入读取数据路径的时钟由PHASER_IN提供 - IDELAY reference clock(200 MHZ)

需要始终提供200 MHz ref_clk,然后MIG使用额外的MMCM创建适当的IDELAYCTRL频率

配置MIG IP核参数说明(NATIVE)

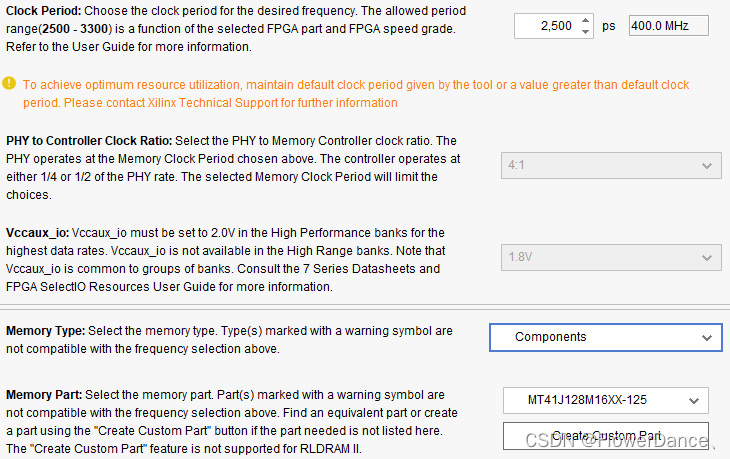

Control Options

1.Clock Period:DDR3 的工作频率,这个参数的范围和 FPGA 的芯片类型以及具体类型的速度等级有关。注意这个时钟是 MIGIP 核产生,并输出给 DDR3 物理芯片使用的,它关系到 DDR3 芯片具体的运行带宽。

2.PHY to Controller Clock Ratio:DDR3 物理芯片运行时钟和用户接口的时钟(ui_clk)之比,一般有 4:1 和 2:1 两个选项。一般来说高速传输的场合选择 4:1,要求低延时的场合选择 2:1。这里还要指出,当 DDR3 时钟选择选择了 350M 到最高的 400M,比例默认只为 4:1,低于 350M 才有 4:1 和 2:1 两个选项。

同时这个比例会影响到ui接口的数据位宽;2:1时:ui位宽是物理层位宽的4倍(164=64);4:1时:ui位宽是物理层位宽的8倍(168=128)。

3.VCCAUX_IO:这是 FPGA 高性能 bank( High Performance bank)的供电电压。它的设置取决于 MIG控制器运行的周期/频率。当用户让控制器工作在最快频率的时候,系统会默认为 1.8V,当然在 1.8V 下用户可以运行低一点的频率。

4.Memory Type: DDR3 储存器类型选择。

5.Memory Part: DDR3 芯片的具体型号。

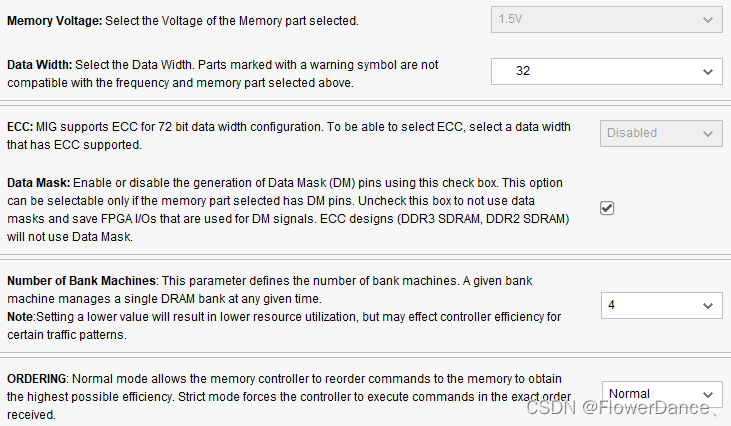

6.Memory Voltage:是 DDR3 芯片的电压选择

7.Data Width:数据位宽选择

8.ECC: ECC 校验使能,数据位宽为 72 位的时候才能使用。

9.Data Mask:数据屏蔽管脚使能。勾选它才会产生屏蔽信号

10.Number of Bank Machines: Bank Machine 的数量是用来对具体的每个或某几个来单独控制的,选择多了控制效率就会高,相应的占用的资源也多,平均一个 Bank Machine 控制两个 BANK

11.ORDERING:该信号用来决定 MIG 控制器是否可以对它收到的指令进行重新排序,选择 Normal 则允许, Strict 则禁止,选择Normal会获得更高效率。

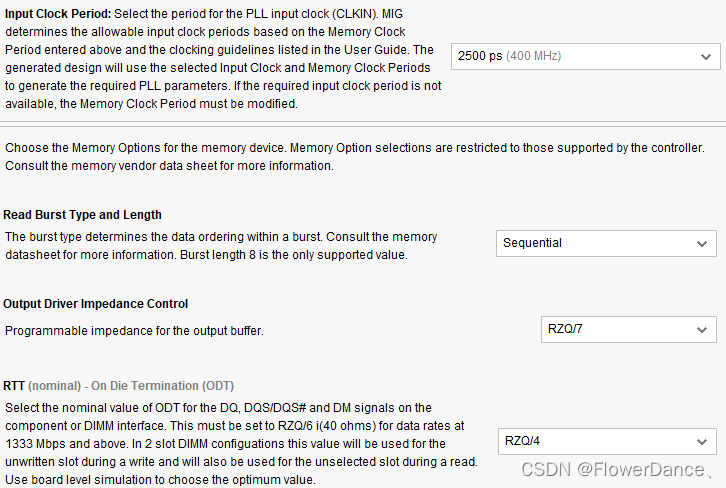

Memory Options

1.Input Clock Period:输入系统时钟频率设置, 这个时钟是提供给 MIG IP 的时钟,IP核内部会自己调用pll和MMCM 来产生自己的工作时钟,这里配置没有啥特别要求。如 MIG IP 内部时钟的结构图所示,可以看到 MIG IP 里面有一个时钟锁相环,系统时钟是这个时钟锁相环的输入时钟,锁相环会根据这里的输入时钟自动产生 MIG IP 内部各种所需的时钟。所以这里的时钟频率的设置没有固定的要求,下拉框中的各种频率值都可以选择。这里考虑到 MIG IP 输入还需要一个 200M 的 IDELAY Reference Clock 时钟,为了将两个时钟共用一个输入时钟,将这里的系统时钟周期(Input Clock Period)配置选择为 5000ps(200MHz)。

2.Read Burst Type and Length: 突发类型选择,突发类型有顺序突发和交叉突发两种

3.Output Driver Impdance Control: 输出阻抗控制。RZQ=240Ω。举个例子,如果RZQ/6被选择,那么输出驱动阻抗是40欧姆。

4.RTT: 终结电阻,可进行动态控制。

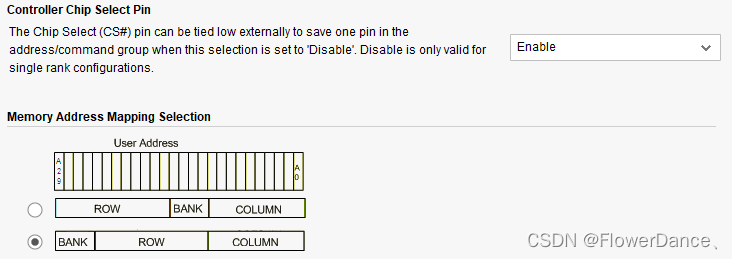

5.Controller Chip Select Pin: 片选管脚引出使能。本实验选择 enable,表示把片选信号 cs#引出来,由外部控制。实际开发板的DDR3 的 CS 信号有连接到 FPGA 管脚,所以这里需要使用该引脚。如果硬件上 DDR3管脚未连接到 FPGA,那么这里就可以设置为 Disable。

6.BANK_ROW_COLUMN: 寻址方式选择。 BANK-ROW-COLUMN 的形式,这是一种最常规的 DDR3 寻址方式,即要指定某个地址,先指定 bank,再指定行,最后指定列,这样就确定了一个具体地址。 一般来说这样寻址方式有利于降低功耗, 但是读写性能( 效率) 上不如“ ROW_BANK_COLUMN”。

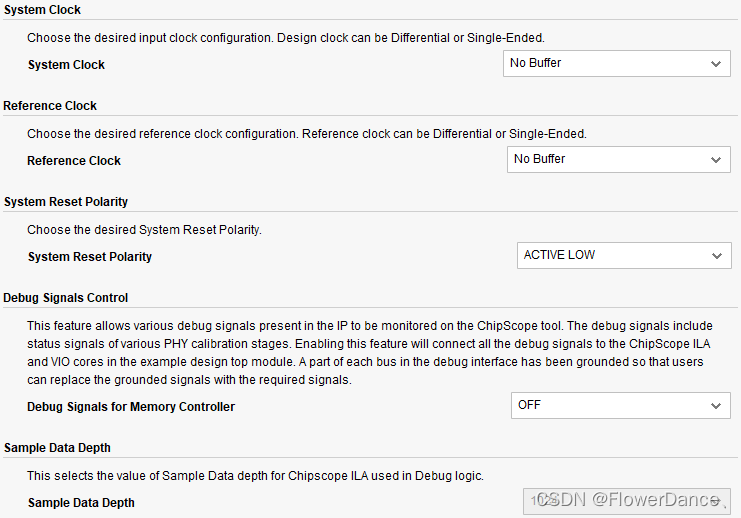

FPGA Options

1.System Clock:该时钟可以是外部晶振(差分、单端)或者是PLL输出的时钟。这里的系统 200M 时钟由 FPGA 内部提供,不由管脚输入,选择 No Buffer,如果实际硬件管脚有提供 200MHz 时钟,也可以选择 Differential(差分输入)或 Signal-Ended(单端输入)。

2.Reference Clock:是设置MIG的参考时钟,这个时钟频率是固定的,如果工作频率>666MHz ,参考时钟固定为300MHz/400MHz,其他工作频率固定为200MHz,这里设置时钟的属性,可以是外部晶振(差分、单端)或者是PLL输出的时钟,PLL输出时配置GBUFF,选择No Buffer。注:如果system clock的频率在199-201MHz之间,这里会出现一个use system clock 的选项,意思就是用系统时钟作为参考时钟。

该时钟需要频率为 200MHz 时钟,由于在前面配置中将系统时钟设置为 200MHz,所以可以选择 Use System Clock,这样就可以将两个输入时钟合并一个共用的 200MH 输入。如果前面的系统时钟设置的不是 200MHz 这里配置选项就没有“ Use System Clock”可选,只能由管脚端口输入时钟或者 FPGA 内部产生这个 200MHz 时钟。

3.System Reset Polarity: 复位有效电平选择。

4.Debug Signals Control:该选项用于控制 MIG IP 核是否把一些调试信号引出来,它会自动添加到 ILA,这些信号包括一些 DDR3 芯片的校准状态信息。

5.Sample Data Depth: 采样深度选择。当“ Debug Signals Control”选择“OFF”时,所有采样深度是不可选的。

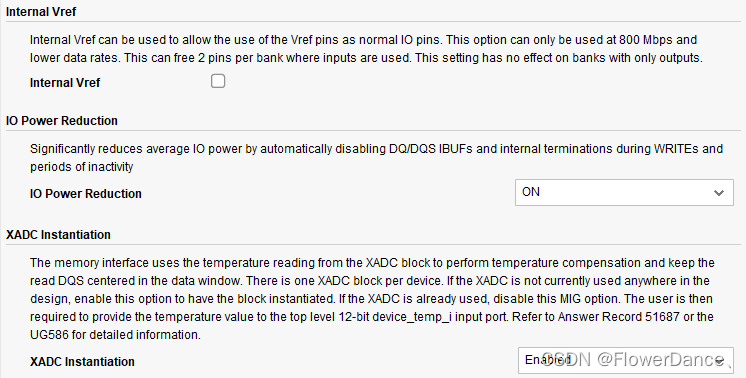

6.Internal Vref: 内部参考管脚,表示将某些参考管脚当成普通的输入管脚来用。由于开发板的 IO 资源较为紧张,因此这里需要选择“ON”,把参考管脚当做普通的输入管脚来用。

7.IO Power Reduction: IO 管脚节省功耗设置。本实验选择“ ON”,即开启。

8.XADC Instantiation: XADC 模块例化。使用 MIG IP 核运行的时候需要进行温度补偿,可以直接选择XADC 模块的温度数据引到 MIG IP 核来使用,否则需要额外提供温度数据,所以本实验选择“ Enable”。

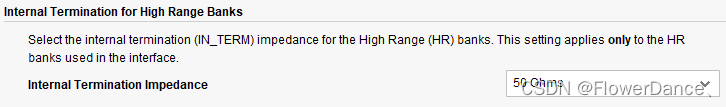

Extended FPGA Options

默认即可

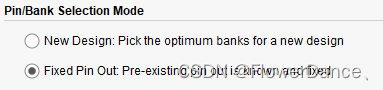

IO Planning Options

一般选第二个。如果当前仅仅是仿真,可以先选择 New Design。要进行上板测试的,则选择“ Fixed Pin Out: Preexisting pin out is known and fixed”。

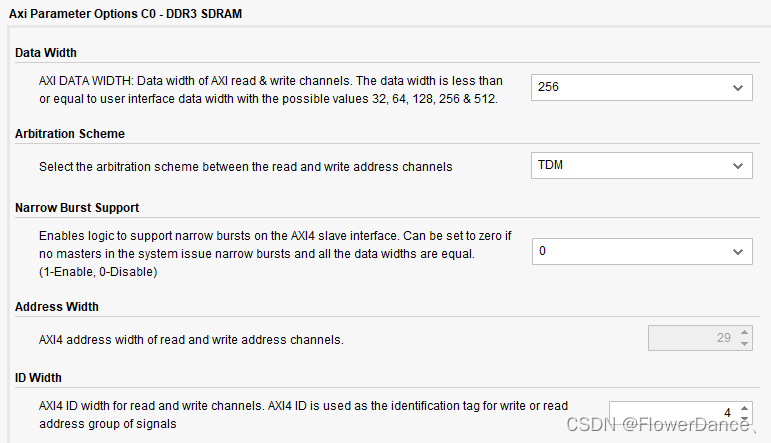

特别的如果选用了axi4接口

1.DATA WIDTH:AXI接口的数据位宽。AXI 总线的数据位宽和前面设置的内存数据线宽(DATA WIDTH)以及用户时钟比例(PHY to Controller Clock Ratio)有关,其最大值满足如下关系:

例如,Clock Ratio=4:1,DATA WIDTH=32,那么一个ui_clk时钟过程中DDR传输了8组数据,对应数据量为2 * 4 * 32 =256,因此AXI总线的数据位宽最大256。

2.Arbitration Scheme:DDR 控制器的仲裁机制,由于 AXI 接口读写通道是独立的,读写各有自己的地址通道,而储存器控制器只有一个地址总线,同一时刻只能进行读或写,这样就存在读/写优先级的问题,这里设置 TDM( Time Division Multiplexing),该设置读写优先级相同,读写交替进行。

-

Time Division Multiplexing (TDM)

读取和写入地址通道的优先级相同。总线对读取和写入地址通道的授予在每个时钟周期交替。AXI master的读取或写入请求不影响仲裁优先级。 -

Round-Robin

读取和写入地址通道的优先级相同。总线对读取和写入通道的授予取决于 AXI master 授予的最后一次服务请求。 -

Read Priority (RD_PRI_REG)

读取和写入地址通道的优先级相同。当发生以下情况之一时,将处理来自写入地址通道的请求:- 没有来自读取地址通道的挂起请求

- Read starve 限制达到 256。仅在突发结束时检查它

- Read wait 限制达到16

- 写QOS为非零。仅在突发结束时检查它。

读取地址通道的请求以类似的方法处理。

-

Read Priority with Starve Limit (RD_PRI_REG_STARVE_LIMIT)

读取地址通道始终具有优先级。当没有来自读取地址通道的挂起请求或达到 Read starve 限制时,将处理来自写入地址通道的请求。 -

Write Priority (WRITE_PRIORITY, WRITE_PRIORITY_REG)

写入地址通道始终具有优先级。当没有来自写入地址通道的挂起请求时,将处理来自读取地址通道的请求。仲裁输出以WRITE_PRIORITY_REG模式进行注册。

3.Narrow Burst Support:窄突发支持。不选此项可以让AXI4总线去掉用于AXI narrow burst的logic,从而节省资源并改善时序。XPS(Xilinx Platform Studio) 通常根据连接的 AXI master的已知行为自动计算是否可以禁用窄突发支持。

4.Address Width:可以理解为DDR3存储位宽,软件会根据之前的参数配置进行计算。

5.ID Width:AXI 读/写通道的 ID 宽度。XPS 会自动设置地址宽度和 ID 宽度设置。

参考

正点原子达芬奇Pro之FPGA开发指南

Xilinx UG586官方文档

小梅哥Xilinx FPGA 开发板自学教程

https://www.cnblogs.com/liushuhe1990/articles/14925861.html

https://zhuanlan.zhihu.com/p/501725127

4415

4415

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?