关键词:

TC3XX 用户手册;TC3XX Interrupt Router;TC397 用户手册;TC397 中断控制器;

简介:

本篇为英飞凌 TC3XX 用户手册第 16 章翻译 - Interrupt Router (IR)

手册适用于 TC3XX(包括 TC397)芯片

官方架构手册下载链接:

AURIX™ TC3xx User Manual Part-1 - Infineon Technologies

AURIX™ TC3xx User Manual Part-2 - Infineon Technologies

目录

16.7.3.SRBx 寄存器的权限保护 - ACCEN_SRBx

服务请求广播寄存器 SRB 的权限保护 - ACCEN_SRBx0/1

16.8.2.内核复位寄存器 - KRST1/0、KRSTCLR

INT_ECRx 和 SRCy[15:0] 写入权限控制寄存器 0 - ACCEN_CONFIG0

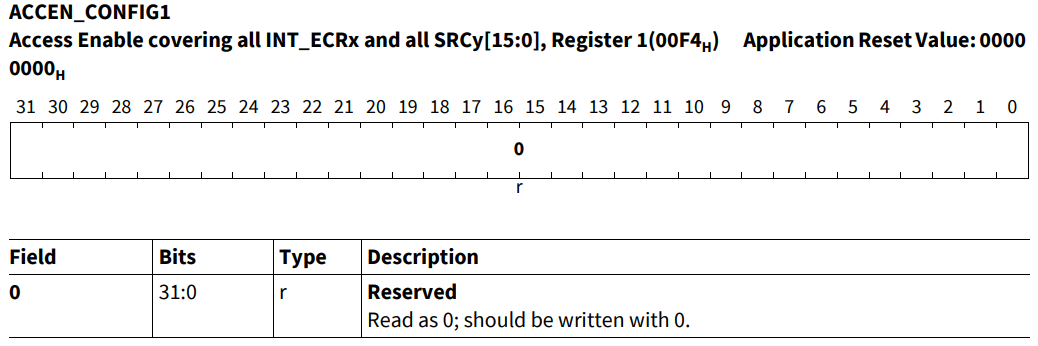

INT_ECRx 和 SRCy[15:0] 写入权限控制寄存器 1 - ACCEN_CONFIG1

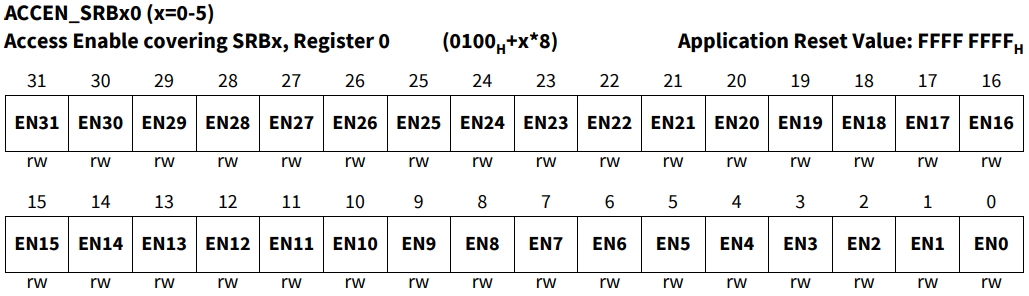

SRBx 写入权限控制寄存器 0 - ACCEN_SRBx0

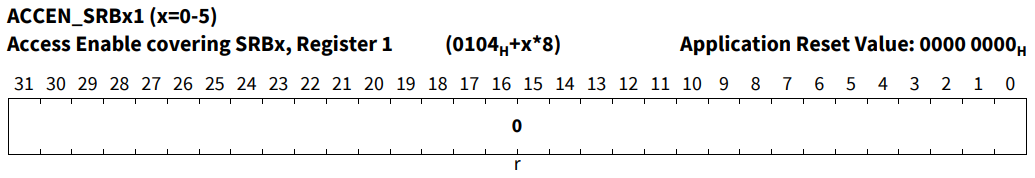

SRBx 写入权限控制寄存器 1 - ACCEN_SRBx1

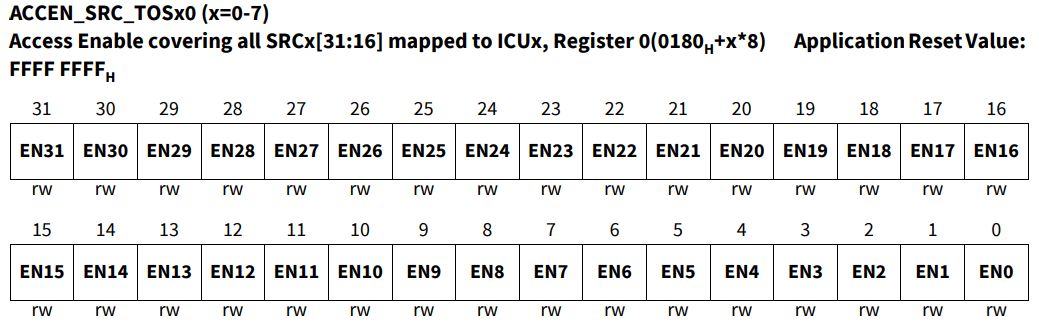

SRCx[31:16] 的写入权限控制寄存器 0 - ACCEN_SRC_TOSx0

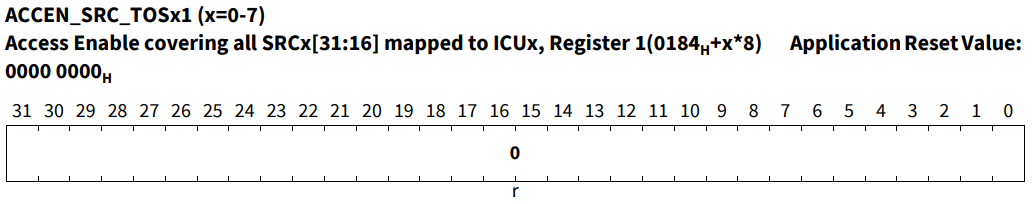

SRCx[31:16] 的写入权限控制寄存器 1 - ACCEN_SRC_TOSx1

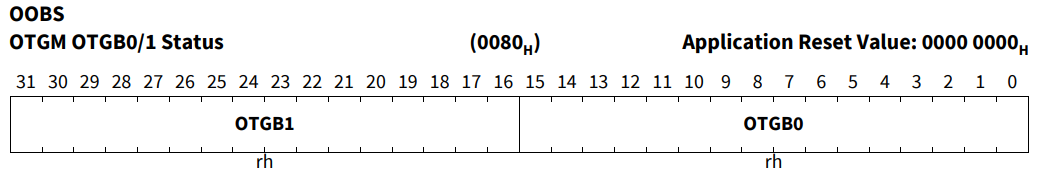

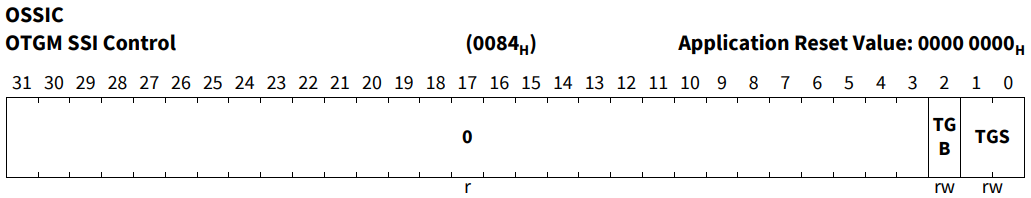

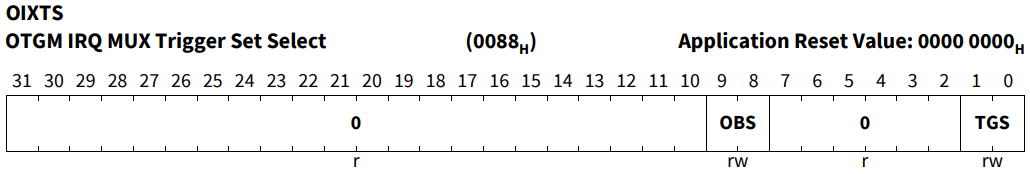

OTGM IRQ 复用 Trigger Set 选择寄存器 - OIXTS

OTGM IRQ 复用 Missing IRQ 选择寄存器 - OIXMS

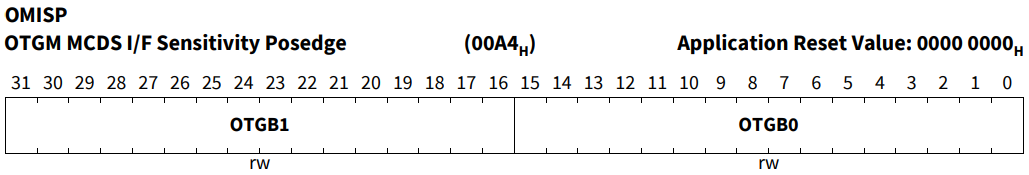

OTGM MCDS I/F 上升沿控制寄存器 - OMISP

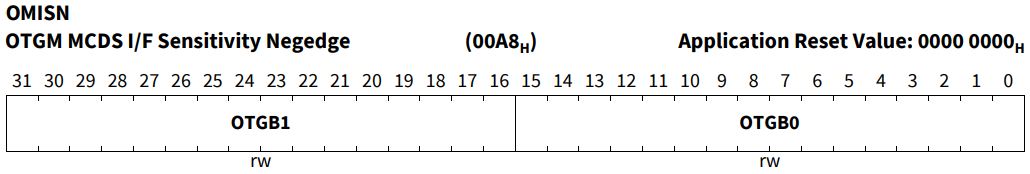

OTGM MCDS I/F 下降沿控制寄存器 - OMISN

本章介绍中断控制器模块,该模块负责调度外部/内部中断源和软件产生的中断(此处称为 Service Request)

中断服务请求的对象可能为 CPU 或者 DMA(此处称为 Service Provider)

文档内容适用于 TC3xx 并包含以下内容:

-

中断系统结构

-

中断系统配置

-

中断控制器的相关操作

16.1.功能列表

中断控制器模块的主要功能:

-

最大支持 1024 个服务请求的中断系统

-

每个 ICU(Interrupt Control Unit)支持最大 255 个等级的服务请求优先级

-

最大支持 8 个 ICU

-

每个 CPU/DMA 都有一个专用的 ICU

-

低延迟:从接收到中断请求到发送给 Service Provider 仅需 3~4 个时钟信号

-

每个外设中断都有一个专用的服务请求节点(Service Request Node,SRN)

-

每个 SRN 都有一个 8 位可编程的优先级编号

-

每个 SRN 都可以被映射至 ICU 或 Service Provider

-

当 Service Provider 应答中断后,硬件会自动清空 SRN

-

中断系统支持完整性检查(ECC)

-

每个 CPU 拥有 8 个可用于软件中断的通用服务请求(General Purpose Service Requests,GPSR)(未分配给外设或外部中断源)

-

服务请求广播寄存器(Service Request Broadcast Registers,SRB)可以同时向多个 Service Provider 发送通用服务请求信号(软件中断)

-

可以根据优先级屏蔽服务请求(对于 CPU 及其内部相关的控制寄存器)

-

外部中断可配置滤波模式和触发模式(例如下降沿、上升沿、高/低电平触发),运行时也可以进行配置

-

CPU 唤醒:若 CPU 为 IDLE 状态且服务请求是发送给 CPU 的,则通知 System Control Units(SCU)唤醒 CPU

16.2. 与TC2xx的差异

下面的功能在 TC3xx 中有所变化

-

General Purpose Service Request Group:每组 SRN 的数量由 4 提升至 8

-

Broadcast Register:广播寄存器的位,映射为新的 GPSR SRN 编号

-

Broadcast Register:每个广播寄存器现在都有一个专用的 ACCEN 寄存器

-

SRCx:引入 SRCx[31:0] 的访问保护(每个 TOS/ICU 都有一个 ACCEN 寄存器)

-

SRC.ECC:ECC 由 6 位修改为 5 位

-

SRC.TOS:TOS 修改为 3 位

-

SRC 偏移及索引方案:SRC 映射至 1024 个 32 位的节点,索引编号 0~1023 等于 SRC 的 32 位偏移量

-

若检测到服务请求被发送给了保留不用的 TOS,则会向 SMU 发送警告信号

-

重新制定了 SRC 寄存器与中断控制器地址的映射关系

16.3.概览

CPU 和 DMA 均可以提供中断服务,因此将中断请求称为服务请求

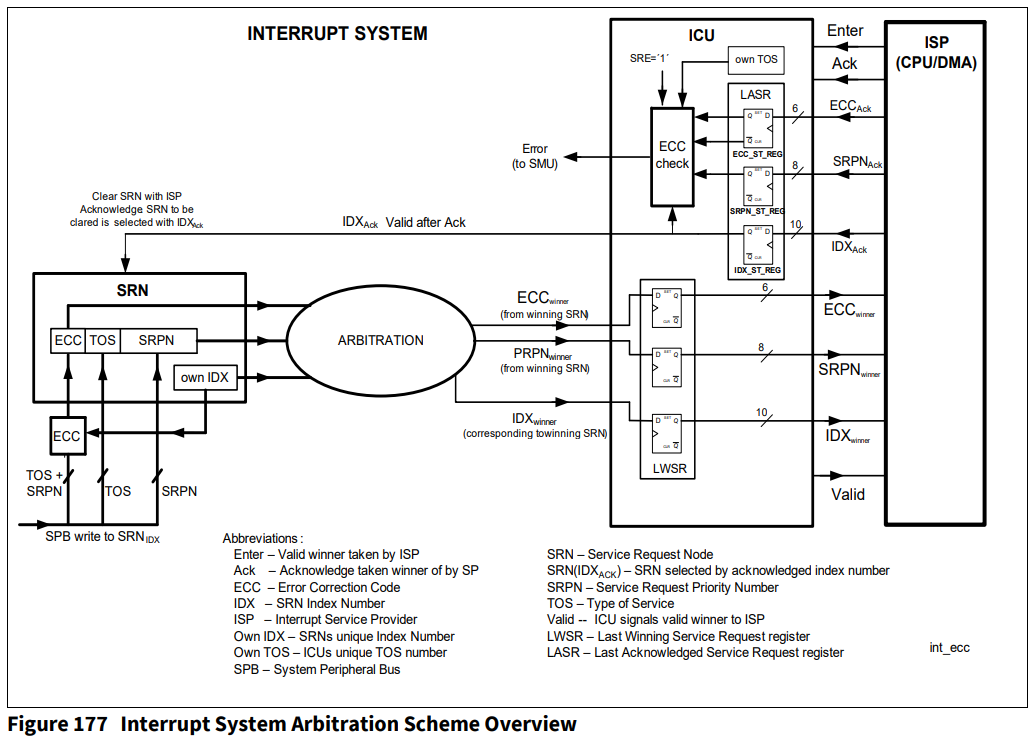

中断控制器模块中实现的中断系统包含服务请求节点 SRN、中断控制单元 ICU 以及为软件开发提供的额外功能

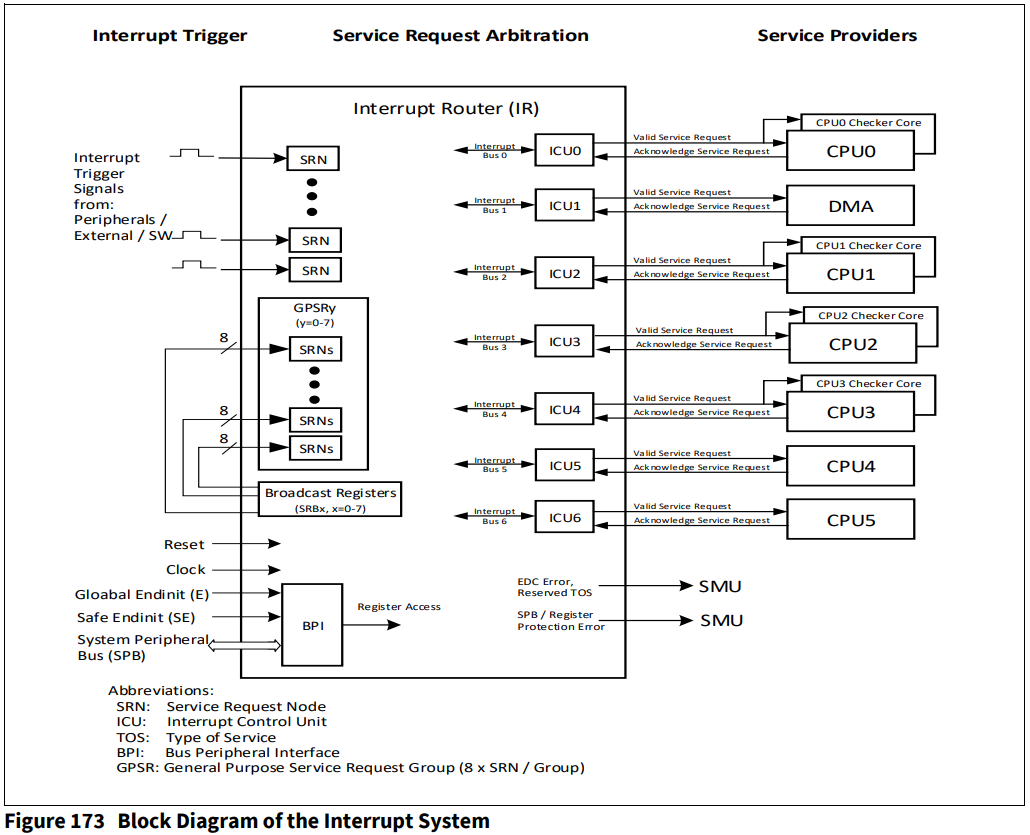

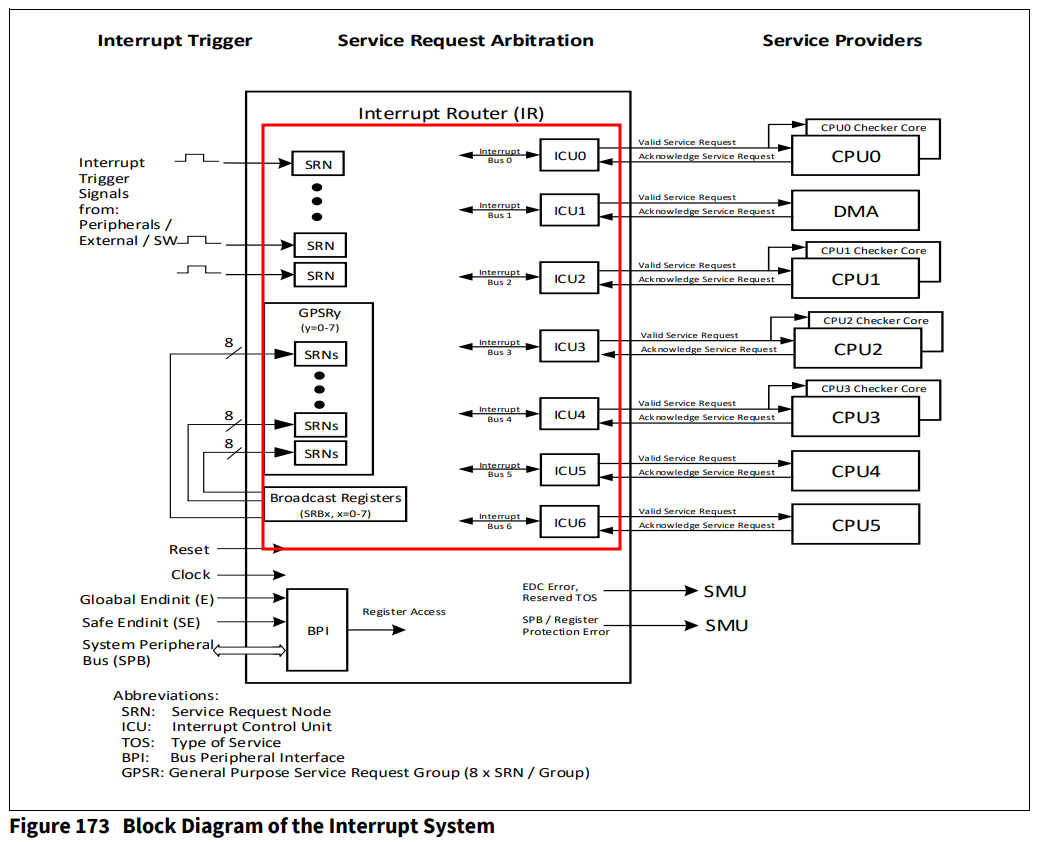

如图 173 所示,中断控制器模块中,每个可以产生服务请求的模块,均与一个或多个服务请求节点连接,中断控制器模块中也包含多个通用的服务请求节点供软件触发中断请求

每个 SRN 均包含一个用于配置服务请求的服务请求控制寄存器 SRC(Service Request Control),该寄存器用于配置优先级、中断请求与 Service Provider 的映射关系等

每个 SRN 都与中断控制器模块中的所有 ICU 连接,其中 SRN 控制寄存器的设置定义了目标 Service Provider 和服务请求的优先级

ICU 负责中断仲裁(处理多个中断的竞争),每个 ICU 连接至一个 Service Provider,ICU 提供仲裁胜出的 SRN,Service Provider 向 ICU 发出信号说明何时处理哪个服务请求

16.4. 服务请求节点

中断控制器模块中的每个服务请求节点 SRN 都包含一个服务请求控制寄存器 SRC 以及接口逻辑,用于连接外部中断源和中断控制器内部的仲裁总线

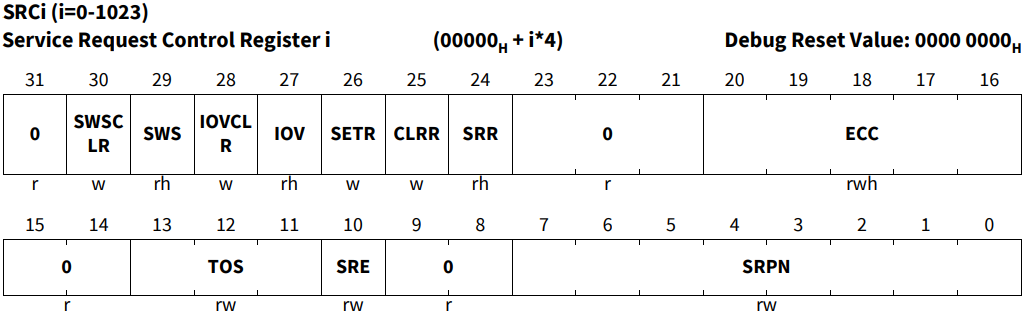

16.4.1.服务请求控制寄存器

中断控制器模块内的每个服务请求控制寄存器都有相同的格式,包括如下部分:

-

SRE:使能/禁用信息

-

SETR/CLRR:服务请求设置位和清除位

-

SWS:指示是否是软件发起的服务请求

-

SRPN:服务请求优先级

-

TOS:服务请求的目标 Service Provider

-

SRR:服务请求状态位

-

SMU:向安全管理单元(Safety Management Unit)发出完整性错误信号

-

IOV:中断溢出位

SRN 可以由中断源通过硬件激活,也可以由软件通过 Software-Initiated 服务,请求对应的控制位进行设置或复位

16.4.1.1.服务请求控制寄存器的通用格式

本章介绍服务请求控制寄存器(Service Request Control Registers,SRC)

注意:一些模块在此之上还有一些额外的中断相关控制寄存器(如中断状态、设置/清除/使能寄存器),这些寄存器在这些模块自身的章节中会进行介绍

服务请求控制寄存器 - SRC

-

SRPN:Service Request Priority Number,SRPN 位定义了对同一个 Service Provider(SRC.TOS 配置相同)发起的服务请求的优先级

-

00H:服务请求为最低优先级

-

FFH:服务请求为最高优先级

-

注意:如果 Service Provider 为 CPU 则最低优先级为 01,不会响应优先级为 00 的服务请求,如果 Service Provider 为 DMA 则优先级为 00 的服务请求将触发通道 0,对于 DMA 而言 SRPN 不能大于 DMA 的最大通道数量

-

-

SRE:Service Request Enable,服务请求使能

-

0B:禁用服务请求

-

1B:使能服务请求

-

-

TOS:Type of Service Control,将服务请求映射至对应的服务供应商

-

注意:若平台没有 DMA 或 CPU,则不使用这些位并将其视作保留位

-

对于中断服务供应商小于 4 的平台,TOS 位需要减少 1~2 位

-

000B:CPU0 service is initiated

-

001B:DMA service is initiated

-

010B:CPU1 service is initiated

-

011B:CPU2 service is initiated

-

100B:CPU3 service is initiated

-

101B:CPU4 service is initiated

-

110B:CPU5 service is initiated

-

Others,Reserved (no action)

-

-

ECC:Error Correction Code,SRN 在以下情况更新 ECC

-

Write or Read-Modify-Write SRC[31:0]

-

Write to SRC[15:0] (16-bit write)

-

Write to SRC[15:8] or write to SRC[7:0] (byte write)

-

更多信息查看 16.4.1.9 章节

-

注意:当前平台 ECC 仅用于错误检测,检测到的错误会报告给 SMU,但不会自动纠正

-

-

SRR:Service Request Flag,当前服务请求的状态

-

0B:没有需要处理的服务请求

-

1B:服务请求待处理

-

-

CLRR:Request Clear Bit,用于清除 SRR

-

0B:无操作

-

1B:清除 SRR,不保存 CLRR 的值,读取返回 0,与 SETR 并发时不执行任何操作

-

-

SETR:Request Set Bit,用于设置 SRR

-

0B:无操作

-

1B:设置 SRR 和 SWS,不保存 SETR 的值,读取返回 0,与 CLRR 并发时不执行任何操作

-

-

IOV:Interrupt Trigger Overflow Bit,若当前 SRN 中有待处理的中断请求,但中断源或 SETR 有新的服务请求则会设置 IOV

-

0B:未检测到中断溢出

-

1B:检测到中断溢出

-

-

IOVCLR:Interrupt Trigger Overflow Clear Bit,用于清除中断溢出位 IOV

-

0B:无操作

-

1B:清除 IOV,不会存储该位的值,读取该位总会返回 0

-

-

SWS:SW Sticky Bit,使用 SETR 设置 SRR 位时也会设置该软件粘滞位,通过 SWSCLR 可以清除该位,直接向该位写值会被忽略

-

0B:没有通过 SETR 设置的中断

-

1B:存在通过 SETR 设置的中断

-

-

SWSCLR:SW Sticky Clear Bit,用于复位 SWS

-

0B:无操作

-

1B:清除 SWS,不会存储该位的值,读取该位的值只会返回 0

-

16.4.1.2.修改 SRN 配置

SRN 默认为禁用状态,如果需要使用 SRN 节点,需要对其进行配置,并通过设置 SRC.SRE = 1 启用该节点

配置 SRN 节点,需要设置该节点的中断请求对象 SRC.TOS,以及中断请求优先级 SRC.SRPN

SRN 节点启用后,若需要修改 TOS 或 SRPN,则需要按照如下顺序进行:

-

禁用 SRN 节点(设置 SRC.SRE = 0)

-

检查 SRN 节点是否禁用(回读 SRN.SRE 确保其为 0)

-

检查 LWSRx 寄存器(上次胜出的服务请求 Last Winning Service Request):

-

如果 LWSRx.STAT = 0 或者 LWSRx.ECC 与原来的 SRC 节点不同,则可继续进行下一步操作

-

如果 LWSRx.STAT = 1 并且 LWSRx.SRPN 以及 LWSRx.ECC 等于原来 SRC 中的值,则需要再次检查 LWSRx 寄存器

-

-

修改 SRC.TOS 和 SRC.SRPN

-

使能该 SRC 节点(设置 SRC.SRE = 1)

如果需要重新配置的 SRN 节点在禁用时处于待处理状态(Pending),则表示该 SRN 节点的中断请求已经过中断仲裁,并已提交给服务供应商(CPU 或 DMA),这种情况下,经过重新配置的 SRN 节点应该在 LWSRx 轮询算法结束后再进行使能,确保之前的中断请求不会再次产生

如果 SRN 在被禁用前已经被 CPU 或 DMA 接收(已跳转至该中断向量,但尚未执行具体的中断服务程序),则无法确定应该在何时查询该节点的状态信息,如果服务供应商为 DMA,则中断接收和中断应答在同一个 Cycle 内完成

上面 LWSRx 寄存器中的 x 表示对应的 TOS,例如,TOS = 0 对应 LWSR0,TOS = 1 对应 LWSR1 等等

16.4.1.3.SRC 寄存器的权限控制

SRC 寄存器受片上总线 Master TAG ID 写入保护,通过中断控制器的 ACCEN_CONFIG 和 ACCEN_TOSx 寄存器控制写入保护

SRC 寄存器第的访问保护

-

SRC 寄存器的第 16~31 位受 ACCEN_TOSx (x = SRC.TOS)寄存器保护

-

SRC 寄存器的第 0~15 位受 ACCEN_CONFIG 寄存器保护

SRC 寄存器的写保护被拆分成如上两部分,因此,可以为所有的 SRC 配置不同的保护策略,这些权限控制寄存器在运行时可能会被相关的软件任务视作正常应用的一部分(如软件中断)

违反保护写入 SRC

如果直接将 32-bit 的值写入 SRC 寄存器,则只有不受 ACCEN 寄存器保护的部分才会被写入:

-

违反 ACCEN_TOSx 和 ACCEN_CONFIG 的保护:任何值都无法写入 SRC 寄存器,同时向安全管理模块 SMU 发送警告信息

-

违反 ACCEN_TOSx 的保护:只有不受 ACCEN_CONFIG 保护的 0~15 位会写入 SRC 寄存器,同时向安全管理模块 SMU 发送警告信息

-

违反 ACCEN_CONFIG 的保护:只有不受 ACCEN_TOSx 保护的 16~31 位会写入 SRC 寄存器,同时向安全管理模块 SMU 发送警告信息

SRC 0~15 位的保护措施

SRC 寄存器的 0~15 位受 ACCEN_CONFIG 寄存器的保护

仅当片上总线的 Master TAG ID 与 ACCEN_CONFIG 中定义的值一致时,才允许其写入 SRC 寄存器

注意:修改 SRC.TOS、SRC.SRE、SRC.SRPN(这些位均位于 SRC 寄存器的 0~15 位范围)会间接修改 SRC.ECC

使用示例

SRC 中的相关位具有如下特性:

-

可以在启动时进行配置

-

在运行时为静态 Static

-

不会被不安全的软件任务修改

ACCEN_CONFIG 允许具有特定 TAG ID 的模块重新配置 SRC 寄存器,例如 CPUx.DMI Safe TAG ID

SRC 16~31 位的保护措施

SRC 寄存器的 16~31 位受 ACCEN_SRC_TOSx 寄存器的保护,两者的对应关系如下:

-

SRCx.TOS = 0:SRC 寄存器受 ACCEN_SRC_TOS0 的写保护

-

SRCx.TOS = 1:SRC 寄存器受 ACCEN_SRC_TOS1 的写保护

-

SRCx.TOS = 2:SRC 寄存器受 ACCEN_SRC_TOS2 的写保护

-

...

注意:保留未使用的 TOS 编号没有对应的 ACCEN_SRC_TOSx 寄存器,这种情况下,该 SRC 寄存器始终可以写入,如果该 SRC 产生了中断请求,则会因为 TOS 错误而向安全管理模块 SMU 发送警告信息

使用示例

SRC 寄存器的 16~31 位包含控制信息,这些控制信息可用于:

-

设置中断请求(软件中断请求)

-

清除中断请求

-

清除中断溢出位或软件粘滞位

-

通过 SRC.ECC 字段检查 ECC 错误

如果没有这些控制信息,则任何外设或任务都可以向任意 CPU 发送/清除中断请求,这会导致混乱

通过使用这些控制信息,可以对每个软件中断任务进行封装,使其针对于特定的 CPU 或 DMA,同时,当这些中断任务出现错误时,CPU 可以正确识别

示例:所有映射至 CPU0(TOS = 0) 的 SRN 节点均受 ACCEN_SRC_TOS0 的写保护,因此,仅当总线的 TAG ID 与 ACCEN_SRC_TOS0 寄存器中定义的值一样时,才允许该总线设置或清除这些 SRN 的中断请求,比如,ACCEN_SRC_TOS0 可以配置为仅允许 CPU0 自身相关的任务才允许设置软件中断,这样做确保其他 CPU 或者 DMA 无法通过中断影响 CPU0 的执行

注意:访问保护会忽略错误的写入请求,并向 SMU 发送警告信息,但是不会产生其他的中断或 Trap

16.4.1.4.请求设置/清除位 - SETR/CLRR

SETR 和 CLRR 位允许软件设置或清除中断请求位 SRR:

-

向 SETR 写 1 会将 SRR 置 1

-

向 CLRR 写 1 会将 SRR 置 0

-

同时向 SETR 和 CLRR 写 1,SRR 不会改变

-

SETR 和 CLRR 不会保存写入值(会自动恢复为 0)

-

向这两位写 0 无效

-

读取这两位只会返回 0

16.4.1.5.使能位 - SRE

使能 SRE 位(Service Request Enable)会将中断交给对应的 Service Provider 进行中断仲裁,该位不会影响中断请求标志位 SRR

中断请求标志位 SRR 可由硬件或软件设置(通过 SETR),其状态不受中断使能位 SRE 影响

这种方式使得硬件或软件(通过 POLL)可以自动处理中断请求

SRE = 1

如果SRE = 1,挂起的中断请求会被发送给对应的 Service Provider 进行中断仲裁

当该中断请求被应答后,硬件会自动将 SRR 置 0

因为硬件会控制中断请求标志位 SRR,因此软件不应该修改该位以免产生无法预料的行为

SRE = 0

如果 SRE = 0,则挂起的中断请求不会发送给对应的 Service Provider

软件可以轮询中断请求标志位 SRR 以检查是否存在挂起的中断请求

中断请求应答后(ACK),软件必须向 CLRR 写 1 复位 SRR

注意:本章节中,Active Source(活动源)指的是,对于一个 SRN 节点,其对应 SRC 寄存器的 SRE 位为 1(允许响应该节点的中断请求)

16.4.1.6.服务请求标志 - SRR

SRR 置 1 表示当前存在挂起的中断请求

硬件可以直接修改 SRR 位,软件可以通过操作 SETR 或 CLRR 位间接修改 SRR 位,软件直接向 SRR 位写值无效

不管 SRE 位的状态如何,硬件和软件都可以设置 SRR 位,但是,仅当 SRE 位为 1 时,设置 SRR 位才会将中断请求发送给中断控制器

当 SRE 为 1 时,设置 SRR = 1 会将中断请求发送给中断控制器进行中断仲裁

当 SRE 为 0 时,中断控制器会忽略该节点的中断请求(不会进行中断仲裁)

当 CPU 或 DMA 接收并应答该节点的中断请求后,硬件会自动复位 SRR(设置 SRR = 0)

软件可以轮询 SRR 位以确认该中断请求是否挂起,这种情况下,SRR 必须由软件向 CLRR 写 1 清除

注意:清除 SRN 节点的中断请求标志 SRR、使能 SRN 节点的中断必须分两步执行,首先通过 SRC.CLRR 清除 SRR,然后再使能(设置 SRC.SRE = 1)

16.4.1.7.请求对象控制 - TOS

Type of Service - TOS

每个 TriCore CPU 以及 DMA 均可以视作一个中断服务供应商(Interrupt Service Provider,ISP)

中断请求节点可以通过 TOS 位映射至对应的 ISP

通过 TOS 位可以将中断请求映射至:

-

中断服务供应商(CPUx、DMA)

-

中断控制器内部的中断路由(通过 Interrupt Control Unit (ICU) 间接映射至 ISP,TOS = 0 对应 ICU0,TOS = 1 对应 ICU1,...)

-

ACCEN_SRC_TOSx 写保护寄存器(TOS = 0 对应 ACCEN_SRC_TOS0,...)

注意:

-

SRN 节点的 SRE = 1,但未配置 TOS,如果软件或硬件触发了该节点的中断请求,则会向 SMU 发送警告,且不会进行下一步的操作

-

SRN 节点的 SRE = 1,但 TOS 为保留值,如果软件或硬件触发了该节点的中断请求,则会向 SMU 发送警告,且不会进行下一步的操作

16.4.1.8.服务请求优先级 - SRPN

服务请求优先级编号 SRPN(Service Request Priority Number)定义了服务请求的优先级,用于中断仲裁

对于每个映射至同一服务供应商的 SRN 节点(TOS 相同):

-

SRPN 编号可以唯一

-

SRPN 编号可以不唯一(组成中断优先级组,该组的所有中断节点拥有相同的优先级)

-

同一中断优先级组中的中断请求无法确定先后顺序

-

SRN 的 SRE 为 0 时,SRPN 可以随意配置

服务供应商为 CPU

服务请求通过中断向量表与 CPU 关联,中断向量表按照优先级排序,这与其他架构的 CPU 不同,其他架构一般按照中断源进行排序

TriCore 允许单个外设存在多个优先级,即单个外设可以触发不同优先级的多个中断

注意:对 CPU 而言,优先级 0000 具有特殊意义,CPU 不会响应 SRPN 为 0000 的中断请求,因此该节点的 SRR 不会被清除,同时,其不会阻塞中断控制器继续进行中断仲裁

注意:TriCore 可以灵活配置中断向量表,使其按照 8 字节或 32 字节对齐,具体参考手册 CPU 章节

服务供应商为 DMA

服务请求与服务请求优先级编号 SRPN 和 DMA 通道编号相关联:SRPN = x 触发 DMA 的通道 x

仅当 SRPN 与 DMA 通道编号对应时,才会触发 DMA 中断,如果 SRPN 大于 DMA 的最大通道编号,则不会触发 DMA 通道中断,该中断请求会被视为其他类型的 DMA 中断请求

示例:

-

DMA 拥有 16 个通道,则 SRPN = 0x0 会触发 DMA CH0,SRPN = 0x7 会触发 DMA CH7,所有 SRPN > 0x0F 的中断请求会被视为其他类型的中断请求,不会触发 DMA 通道

-

对于 64 通道的 DMA,SRPN = 0x0 会触发 DMA CH0,SRPN = 0x17 会触发 DMA CH23,SRPN = 0x3F 会触发 DMA CH64,所有 SRPN > 0x3F 的中断请求会被视为其他类型的中断请求,不会触发 DMA 通道

-

当 SRC 配置错误(TOS、SRPN、SRE 错误)而触发不存在的 DMA 通道时,ICU EDC(ICU Error Detection)会捕获该错误,并在 DMA 返回错误信息后,将所有信息反馈给 ICU

16.4.1.9.ECC 编码 - ECC

SRC.ECC 在以下情况发生改变:

-

写/读改写 SRC 寄存器的 0~31 位(32-bit 写入)

-

写入 SRC 寄存器的 0~15 位(16-bit 写入)

-

写入 SRC 寄存器的 8~15 位或写入 SRC 寄存器的 0~7 位(8-bit 写入)

使用 32-bit 写入或读改写方式操作 SRC 寄存器时,ECC 会根据写入值进行更新,直接写入 ECC 字段的部分会被忽略

ECC 基于 SRC.SRPN、SRC.TOS、SRC.SRE 以及内部的 10-bit 标签索引进行编码

仅当 CPU/DMA 接收该节点的中断请求时,才会对该节点进行一次 ECC 检查

可以通过以下方式插入 ECC 错误,检查 ECC Check 是否可以正常工作:

-

写入 SRC 寄存器的 16~23 位(8-bit 写入)

-

写入 SRC 寄存器的 16-31 位(16-bit 写入)

注意:目前 ECC 仅用于错误检查,检测到错误时会向 SMU 发送警告信息,但不会自动纠正 ECC 的值

ECC 编码方式

中断控制器通过 ECC 检测错误,ECC 编码采用 Hsiao 22_5 编码,具备双重错误检测的能力(Double Error Detection,DED):

// VHDL

GEN_ENC22_5:

if (word_width_g/(nb_mems_g*ecc_granularity_g)) = 22 and (nb_check_bits_g = 5)

generate cmr22_5:

for i in 0 to nb_check_bits_g - 1

generate

CODE_MATRIX_ROWS(i) <= code_rows_22_5(i);

end generate;

end generate;

----------------------------------------------------------------------------------

// VHDL

type rows_22_5_t is array (4 downto 0) of std_ulogic_vector(21 downto 0);

constant code_rows_22_5 : rows_22_5_t : = ("0001001011001011011011",

"0010010101010101101101",

"0100100110100110110110",

"1000111000111000111111",

"1111000000111111000111");16.4.1.10.中断触发溢出位 - IOV

当以下条件均满足时设置 IOV = 1:

-

当前节点的中断请求为挂起状态

-

该节点再次产生中断请求

16.4.1.11.中断触发溢出清除位 - IOVCLR

向 IOVCLR 写 1 可清除中断溢出位 IOV

16.4.1.12.软件粘滞位 - SWS

当 SETR 被设置为 1 时,自动将 SWS 置 1

16.4.1.13.软件粘滞清除位 - SWSCLR

向 SWSCLR 写 1 可清除软件粘滞位 SWS

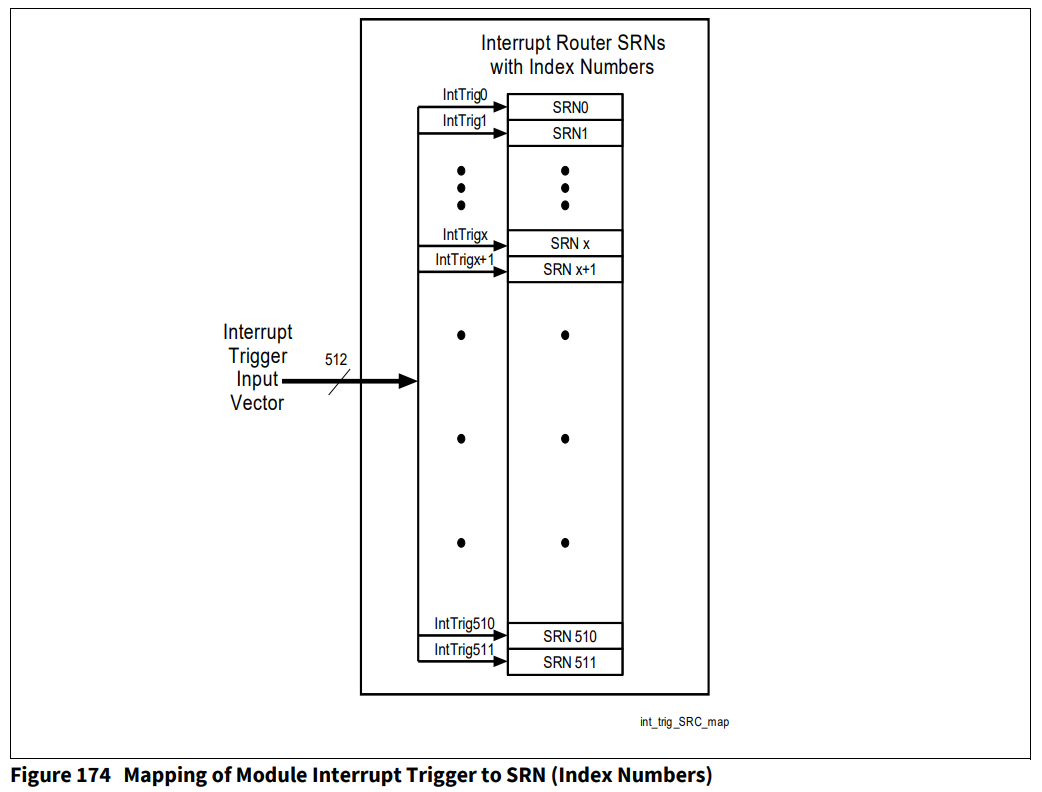

16.5.中断请求与 SRN 的映射关系

所有模块的中断请求均会映射至中断控制器中的 SRN 节点,各模块的每个中断请求在中断控制器中均有一个对应的 SRN 节点

中断控制器中的 SRN 节点拥有唯一的索引编号,中断控制器本身的逻辑不依赖这些索引,只有通过 OTGM 观察 SRN 节点时才会用到这些编号

如果服务请求控制寄存器 SRC 的地址范围正确,则可以通过偏移量直接计算出每个 SRN 对应的 SRC 寄存器的索引,参考 16.5.1 章节

中断控制器拥有 1024 个中断向量,每个中断向量均对应一个 SRC,因此中断触发意味着对应的 SRN 节点产生了中断

注意:中断触发信号的上升沿有效,参见 16.5.3 章节

16.5.1.SRC 的索引编号

每个服务请求节点 SRN 均有一个对应的 SRC 控制寄存器

整个 Aurix 系列平台,各模块对应的 SRC 寄存器的地址都是相同的

中断控制器中的每个 SRC 寄存器均有唯一的索引编号,其计算方式如下:

-

Index(SRC) = <SRC Address Offset> / 4

例如:SRC_BCU_SPB 寄存器的地址为 0x20,则 Index(SRC_BCU_SPB) = 0x20 / 4 = 8

16.5.2.Debug Reset 相关的中断

出于软件调试的目的,Aurix 设备需要一些仅与 Debug Reset 相关的 SRN,在非 Debug Reset 情况下,这些 SRN 保留其 SRC 寄存器的内容和待处理的服务请求状态(例如,软件复位),结合其他调试方式(例如,程序断点),用户可以调试程序复位及程序复位之后的行为

16.5.3.中断触发信号的时序特征

中断控制器使用系统外设总线 SPB 的时钟,为模块中断/服务请求触发信号,路由至中断控制器的过程提供时钟信息:

-

触发信号必须和 SPB 时钟同步

-

中断控制器对触发信号的边沿敏感(上升沿触发)

-

触发信号的最小高电平时间要大于等于 1 个 SPB 时钟周期

-

相关模块需要维持调试相关的触发信号为高电平,直到该调试中断被处理

16.6.中断控制单元 - ICU

中断控制器中包含多个中断控制单元(Interrupt Control Unit,ICU),每个 ICU 都与一个中断服务供应商(CPU 或 DMA)连接

SRN 节点可以通过 SRC.TOS 映射至一个对应的 ICU,见图 173

中断控制单元 ICU 具有以下功能:

-

根据 SRPN 对映射至同一 ICU 的中断请求进行仲裁

-

将本轮中断仲裁胜出的中断请求提交给对应的服务供应商

-

从服务供应商处获得被接受的中断请求的确认信息(ACK)

-

检查中断请求是否存在错误(ECC 校验)

-

向 SMU 模块发送中断请求完整性警告

-

负责清除已被 CPU 确认接收的中断请求

注意:目前 ECC 编码仅用于错误检查,产生错误时会向 SMU 发送警告信息,但不会自动纠正 ECC

16.6.1.ICU 与 ISP 的接口

ICU 与 ISP 之间的接口受中断控制器的 EDC(Error Detection) 保护,为了保证稳定性,当 ICU 未向 ISP 发送中断请求,或 ISP 尚未发送中断确认信息时,ICU 和 ISP 的输出均为默认值

若产生 Stuck-at-One 错误,且此时的中断信号状态为 VALID,则 CPU 会忽略该中断请求,DMA 对应的通道会被触发,ICU 会检测到该错误,并向 SMU 发送警告信息

若产生 Stuck-at-One 错误,且此时的中断信号状态为 ACKNOWLEDGE,ICU 会使用默认值并进行错误检查

ICU 在没有向 ISP 发送中断请求时(VALID = 0),ICU 的输出信号会设置为如下默认值:

只要 ISP 不向 ICU 发送中断确认信息(ACKNOWLEDGE = 0),ICU 的输出信号会设置为如下默认值:

16.6.2.ICU 控制寄存器

每个 ICU 包含如下几个控制寄存器:

-

Latest Winning Service Request(LWSR)寄存器,该寄存器保存了上次中断仲裁胜出的中断请求的相关信息

-

Last Acknowledged Service Request(LASR)寄存器,该寄存器保存了上次 ISP 发送确认信息的中断请求的相关信息

-

Error Capture 寄存器,当 ICU 检测到 ECC 错误时,该寄存器保存了上次 ISP 发送确认信息的中断请求的相关信息

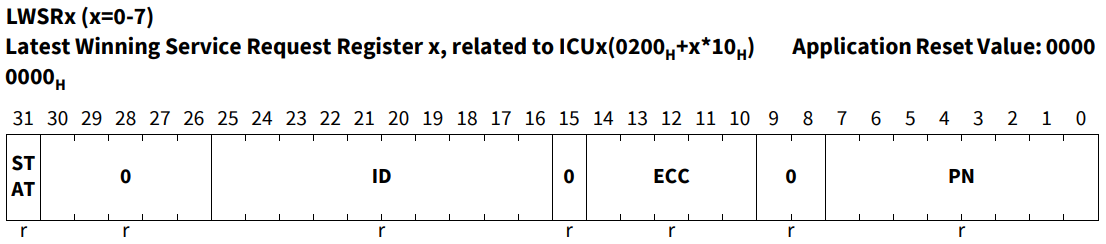

16.6.2.1.LWSR 寄存器

Latest Winning Service Request 寄存器 LWSRx,其中的 x 对应 ICUx(ICU0、ICU1、...)

中断仲裁结束后,LWSR 寄存器会保存胜出的中断请求的相关信息,并将其提供给 ISP

-

PN:Latest Winner Priority Number,中断仲裁结束后,将胜出的中断请求的优先级保存在 PN 字段中,该字段仅当 STAT = 1 时有效;

-

ECC:Latest Winner ECC,中断仲裁结束后,保存胜出的中断请求的 ECC 编码,该字段仅当 STAT = 1 时有效;

-

注意:目前平台实现的 ECC 校验只能用于检测错误(向 SMU 发送警告信息),无法自动纠错;

-

-

ID:Latest Winner Index Number,中断仲裁结束后,保存胜出的中断请求的 SRN 编号,该字段仅当 STAT = 1 时有效;

-

STAT:LWSR Register Status,该位用于标记 PN、ECC 和 ID 字段是否有效,若该中断请求仍然为 Pending 待处理状态,则 STAT = 1,表示这些字段仍然有效,若其对应 ICU 的中断仲裁尚未执行完毕,或者没有需要处理的中断请求,则硬件会自动将该位置 0;

-

0B:LWSR 寄存器中的各字段无效;

-

1B:LWSR 寄存器中的各字段有效;

-

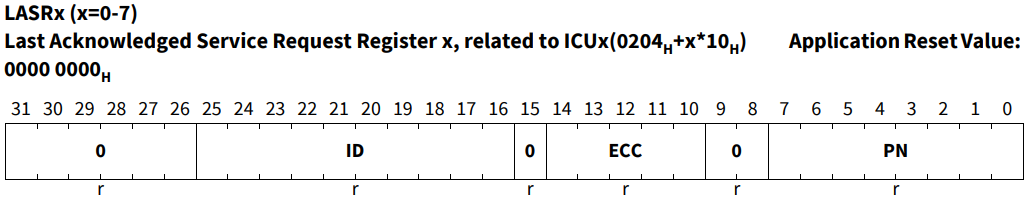

16.6.2.2.LASR 寄存器

Latest Winning Service Request 寄存器 LASRx,其中的 x 对应 ICUx(ICU0、ICU1、...)

中断仲裁结束后,胜出的中断请求会被提交给对应的服务供应商进行处理,服务供应商接受该中断请求后,会设置 LASR 寄存器,即返回确认信息

-

PN:Last Acknowledged Service Request Priority Number,服务供应商接受中断请求后,将该中断请求的优先级保存在 PN 字段中;

-

ECC:Last Acknowledged Interrupt ECC,服务供应商接受中断请求后,保存该中断请求的 ECC 编码;

-

注意:目前平台实现的 ECC 校验只能用于检测错误(向 SMU 发送警告信息),无法自动纠错;

-

-

ID:Last Acknowledged Interrupt SRN ID,服务供应商接受中断请求后,保存该中断请求的 SRN 编号(即 LWSR 寄存器中的 ID 字段);

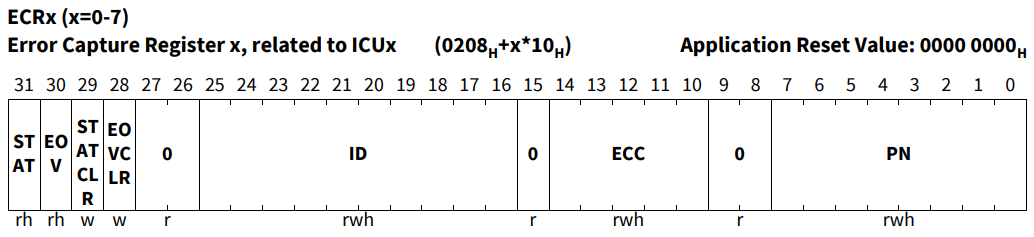

16.6.2.3.ECR 寄存器

Error Capture 寄存器 ECR,其中的 x 对应 ICUx(ICU0、ICU1、...)

在检测到 ECC 错误时,错误捕获寄存器 (ECRx) 会保存该中断请求的相关信息,其检测的是 LASR 寄存器中的 ECC 字段,ECR 寄存器中的内容总是为上一次检测到错误时所保存的相关信息,用户可以通过软件直接清除 PN、ECC 以及 ID 字段

错误状态位 STAT 可用于检查是否存在 ECC 错误,错误溢出位 EOV 可用于检查是否遗漏了错误的中断请求

如果用户需要通过软件清除 ECR.EOV,则需要和 ECR.STAT 一起清除,如果清除的同时产生了新的错误,尽管此时的 ECR.STAT 为 0,但硬件还是会将 ECR.EOV 置 1

注意:目前平台实现的 ECC 校验只能用于检测错误(向 SMU 发送警告信息),无法自动纠错;

-

PN:Service Request Priority Number,检测到 ECC 错误时,保存该中断请求的优先级 SRPN,该位可以通过软件修改;

-

ECC:Service Request ECC,检测到 ECC 错误时,保存该中断请求的 ECC 编码,该位可以通过软件修改:

-

通过修改 SRC 寄存器的 16~23 位进行修改(8-bit 写入);

-

通过修改 SRC 寄存器的 16~31 位进行修改(16-bit 写入);

-

-

ID:Service Request Node ID,检测到 ECC 错误时,保存该中断请求的 SRN 编号,该位可以通过软件修改;

-

EOVCLR:Error Overflow Clear Bit,该位用于清除错误溢出位 EOV,EOV 位必须和 STAT 位一起清除:

-

0B:不进行任何操作;

-

1B:清除 EOV 位,该位的值不会保存(硬件自动复位),读取该位只会返回 0,若写入 EOVCLR 位的同时,EOV 位被置 1,则不会进行任何操作;

-

-

STATCLR:Error Status Clear Bit,该位用于清除错误状态位 STAT:

-

0B:不进行任何操作;

-

1B:清除 STAT 位,该位的值不会保存(硬件自动复位),读取该位只会返回 0,若写入 STATCLR 位的同时,STAT 位被置 1,则不会进行任何操作;

-

-

EOV:Error Overflow Bit,当 ECR.STAT = 1(已检测到错误的中断请求)时,再次出现错误的中断请求(错误溢出),则将该位置 1:

-

0B:未检测到错误溢出;

-

1B:检测到错误溢出;

-

-

STAT:Error Status Bit,当 ICU 检测到 ECC 错误时,会设置 STAT 位:

-

0B:未检测到 ECC 错误;

-

1B:检测到 ECC 错误;

-

16.7.通用服务请求和服务请求广播

中断控制器提供了多组通用服务请求(General Purpose Service Request,GPSR),同时提供了一种机制,该机制允许软件同时触发 GPSR 组内的多个中断请求,通用服务请求仅用于软件中断,因为这些中断请求与硬件没有直接的映射关系

16.7.1.通用服务请求 - GPSRxy

中断控制器提供了多个通用服务请求组:

-

每个通用服务请求组包含 8 个服务请求节点(SRN);

-

通用服务请求标记为 SRC_GPSRxy,其中 x 为组编号,y 为该节点在该组内的索引,y 的范围为 0~7;

-

GPSR 仅用于软件触发中断请求;

-

如果需要触发 GPSR 内节点的中断请求,需要向对应的 SRC_GPSRxy.SETR 写 1,或者向对应的服务请求广播寄存器 SRBxy 写 1;

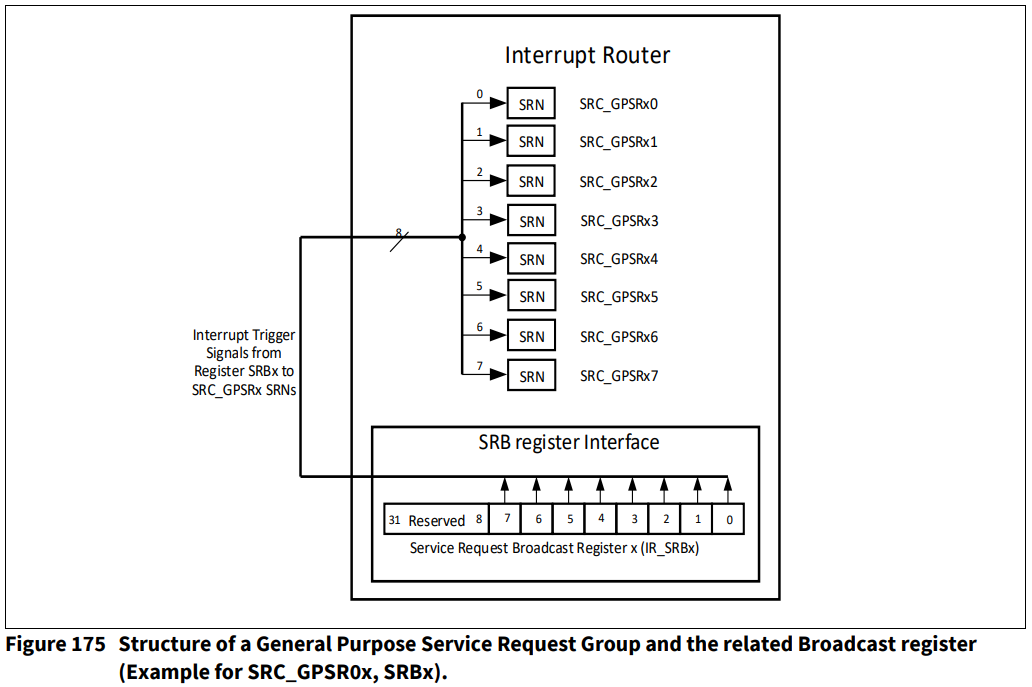

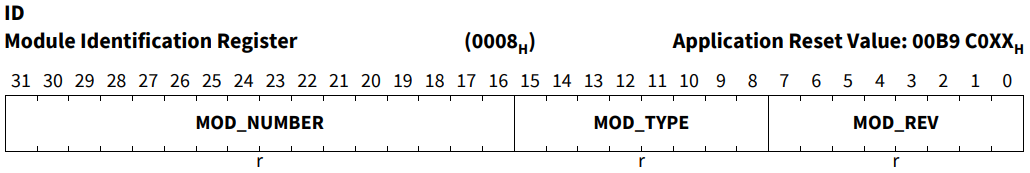

16.7.2.服务请求广播寄存器 - SRBx

服务请求广播寄存器 SRBx 可以将中断请求同时发送给多个服务供应商(CPU or DMA)

每个通用服务请求组 GPSRxy 均有一个对应的服务请求广播寄存器 SRBx

服务请求广播寄存器 SRBx 可以同时触发 GPSRxy 内的多个中断请求,参考图 175

-

读取服务请求广播寄存器只会返回 0;

-

向 SRBx 寄存器的第 y 位(y 的范围为 0~7) 写 1 触发 GPSRxy 的中断请求;

-

向 SRBxy 寄存器的第 6~31 写 1 不会执行任何操作;

16.7.3.SRBx 寄存器的权限保护 - ACCEN_SRBx

SRBx 寄存器受 ACCEN_SRBx0 和 ACCEN_SRBx1 的写入保护:

-

每个 SRBx 寄存器均有一个对应的 ACCEN_SRBx 寄存器(两者 x 的编号相同);

-

ACCEN_SRBx 可以进行配置,允许具有指定 TAG ID 的总线,对 SRBx 寄存器执行写入操作;

-

如果违反 ACCEN_SRBx 的保护,则本次写入操作会被忽略,并且向 SMU 发送警告信息,除此以外不会执行其他操作;

使用示例:当总线试图写入 SRBx 寄存器,以触发 GPSRx 内的多个中断请求时,会检查该总线的 TAG ID 是否和 ACCEN_SRBx 中设置的一致

16.8.系统寄存器

中断控制器不支持时钟控制寄存器 CLC、片上调试寄存器 OCS 以及内核复位寄存器 KRSTx

中断控制器支持多组权限控制寄存器 ACCEN

-

INT_ACCENx:支持通过 ACCEN、 ACCEN_CONFIG0/1、ACCEN_SRBx0/1、ACCEN_SRC_TOSx0/1 寄存器控制读写权限;

-

INT_CLC:中断控制器不支持时钟控制寄存器 CLC;

-

INT_KRSTx:中断控制器不支持内核复位寄存器 KRSTx;

-

OCS:中断控制器不支持片上调试寄存器 OCS(OCDS Control and Status);

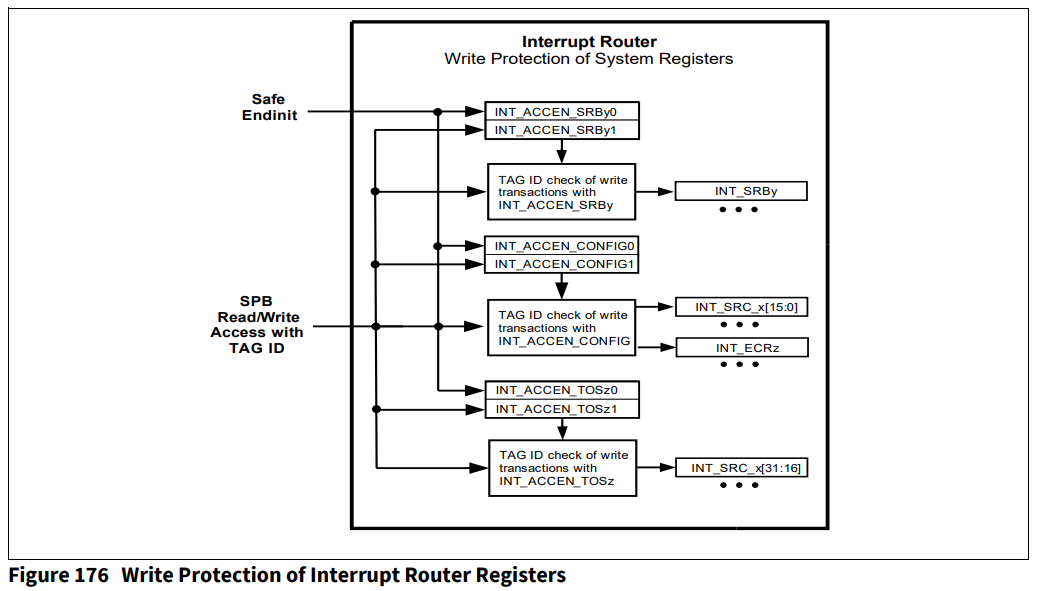

16.8.1.中断控制器的写入权限保护

中断控制器提供基于 TAG ID 的写入权限保护

连接至片上总线的模块直接或间接拥有一个 TAG ID 用于识别这些设备(参考片上总线系统章节)

中断控制器为控制器寄存器提供了三类 ACCEN 权限控制寄存器,见图 176

服务请求广播寄存器 SRB 的权限保护 - ACCEN_SRBx0/1

中断控制器提供了一组或多组通用服务请求组 GPSRxy:

-

x 为通用服务请求组的编号(GPSRx);

-

y 为该组内服务请求节点的编号(y 的范围为 0~7,即每个组包含 8 个服务请求节点 SRN);

对于每个 GPSRx 组,均有一个对应的服务请求广播寄存器 SRBx,用于同时触发该组内的多个服务请求节点,更多信息参考 16.7.3 小节

控制寄存器的权限保护 - ACCEN_CONFIG0/1

ACCEN_CONFIG 寄存器为以下寄存器提供权限保护:

-

SRCx 寄存器的第 0~15 位,这些位包含了 TOS、SRPN、SRE 三个字段,更多信息参考 16.4.1.3 小节;

-

ECRx 即所有的 ICU 错误捕获寄存器;

SRC 寄存器的权限保护 - ACCEN_SRC_TOSy

ACCEN_SRC_TOSy 为 SRC 寄存器的第 16~31 位提供写入权限保护,更多信息参考 16.4.1.3 小节

16.8.2.内核复位寄存器 - KRST1/0、KRSTCLR

中断控制器模块没有内核复位的相关寄存器(KRST1、KRST0、KRSTCLR)

注意:中断控制器不支持模块内核复位

16.8.3.时钟控制寄存器 - CLC

中断控制器模块没有时钟控制寄存器 CLC

注意:中断控制器不支持时钟控制寄存器,因此无法通过 CLC 禁用该模块的时钟信号

16.8.4.OCDS 控制和状态寄存器 - OCS

中断控制器模块没有片上调试系统控制和状态寄存器 OCS

注意:中断控制器不支持片上调试系统

16.9.中断仲裁流程

中断控制器内部的每个 ICU 均有自己的中断总线,SRN 节点通过 SRC.TOS 位和 ICU/中断总线 进行映射,通过该映射关系,ICU 可以将 SRN 节点产生的中断请求提交给对应的服务供应商

当中断源产生中断请求时,其对应的中断控制总线开始执行中断仲裁流程,与其对应的 ICU 将提供上一轮中断仲裁胜出的中断请求信息

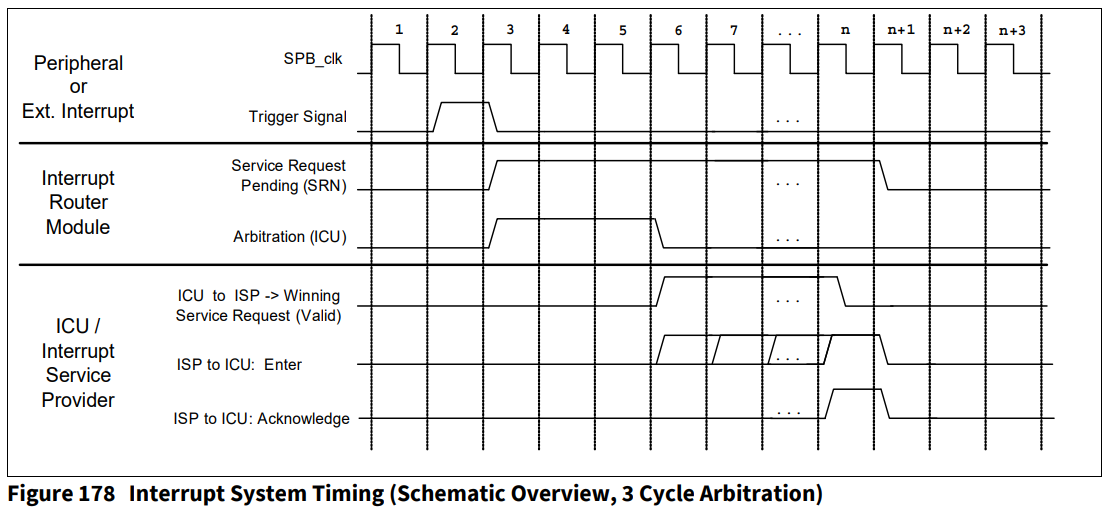

中断仲裁耗费 3~4 个系统外设总线(SPB)时钟周期,并将优先级 SRPN 最高的中断请求设置为挂起状态,确切的编号在模块实现章节中进行介绍

中断请求节点通过 SRC.TOS 映射至对应的中断总线,中断仲裁过程中,中断总线比较该总线上所有中断请求的优先级 SRC.SRPN,并将优先级最高的视为本轮中断仲裁胜出的中断请求,该中断请求节点中的相关信息(SRPN、ECC 以及该 SRN 节点的编号)会被中断总线提交给 ICU,ICU 再将这些信息提供给对应的服务供应商,ICU 从服务供应商处获得确认信息时会进行 ECC 校验(ECC 编码由该 SRN 节点原来的 ECC 值、SRPN、SRN 索引、SRE 位(假定为 1)以及 ICU 的 TOS 编号计算获得)

中断控制器模块在检测到错误时,会向 SMU 发送警告信息(设置 SMU 寄存器中的一个标志位,该标志位用于指示所有 SRN 和 ICU 是否产生错误)

16.9.1.中断仲裁的时钟周期

中断控制器可以配置以下参数:

-

能够支持的服务请求数量(服务请求节点的个数,最大为 1024);

-

SRPN 字段的大小(最大长度为 8-bit);

-

能够支持的服务供应商(中断控制单元 ICU 的个数);

-

每一轮中断仲裁所需的时钟周期(3~4 个 SPB 时钟周期);

中断控制器模块的特性在模块实现章节中进行介绍

图 178 中,中断仲裁消耗 3 个时钟周期,其对应的中断时序如下:

-

Cycle 1:ICU 没有收到挂起的中断请求(因此不会进行中断仲裁);

-

Cycle 2:某个模块通过向中断控制器中对应的 SRN 节点发送 Pulse 触发中断请求;

-

Cycle 3~5:对该 ICU 中所有的中断请求(除了上一轮中胜出的中断请求)进行中断仲裁;

-

Cycle 6:ICU 将获胜的中断请求的相关信息(SRPN、ECC、SRN 索引)提交给服务供应商(CPU/DMA);

-

Cycle 7~(n-1):当有 SRN 节点再次发送中断请求时,ICU 会再次进行中断仲裁,并将该轮中 SRPN 最大的中断请求暂存在 ICU 中;

-

Cycle 6~(n-1):服务供应商获得胜出的 SRN 的相关信息(准备开始执行中断);

-

Cycle n:服务供应商发送确认信息(已被接收 SRN 节点的 SRPN、ECC、SRN 索引),同时 ICU 将自身状态设置为没有可用的有效请求;

-

Cycle (n+1):ICU 会对应答信息进行 ECC 校验,如果检测到 ECC 错误则会向 SMU 发送警告信息,硬件会清除 ICU 中已确认的中断请求的 SRN 编号;

-

Cycle (n+2):如果 ICU 中至少存在一个待处理的中断请求,则 ICU 会开始新一轮的中断仲裁;

16.9.2.中断请求 Valid

ICU 将本轮中断仲裁胜出的中断请求发送给 ISP(向 ISP 发送 Valid 信号),直到收到 ISP 发送的 Enter 信号,才会将本轮中断仲裁视为已完成

16.9.3.中断请求 Enter

服务供应商向 ICU 发出 Enter 信号,表示中断请求已被接收,开始准备处理该中断请求(执行中断服务程序),无论是否存在 Acknowledge 信号,ISP 都可以清除 Enter 信号

当中断服务程序开始执行后,ISP 会向 ICU 发送 Acknowledge 信号,ICU 收到该信号后会清除对应的 SRN

如果执行中断服务程序前,CPU 出现异常或者进入 Trap,则 ISP 不会向 ICU 发送 Acknowledge 信号,ICU 不会清除对应的 SRN

16.9.4.中断请求 Acknowledge

ISP 开始执行中断服务程序后,会向 ICU 发送 Acknowledge 信号,与此同时,ISP 会将该中断请求的相关信息(SRPN、ECC、SRN 索引)返回给 ICU

在同一时钟周期内,ISP 发送 Acknowledge 信号,且 ICU 会将状态设置为没有可用的中断请求(ICU 不会向 ISP 提供仲裁胜出的中断请求),这种机制可以确保 ICU 在复位 SRN 节点前,不会重复向 ISP 提交已经 Acknowledge 的中断请求

16.9.5.ECC 错误处理

ICU 通过服务供应商的 Acknowledge 信号和 ICU 自身的 TOS 编号,对收到的信息进行错误检测,ICU 会默认 SRE 为 1,SRN 节点中的 ECC 编码由 SRC.SRPN、SRC.TOS、SRC.SRE 以及 SRN 节点的索引计算获得

ICU 每次收到 ISP 发送的 Acknowledge 信号时,都会进行错误检查,检查的内容包括 TOS、SRPN、SRN 索引、ECC,ICU 自身的 TOS 值、SRE 位(假定为 1)

如果 ICUx 检测到 ECC 错误,会进行如下操作:

-

ICUx 将出现 ECC 错误的中断请求节点的 SRPN、ECC 编码以及该节点的索引保存在 ECRx 寄存器中,同时将 ECRx.STAT 位置 1,如果该位已经被置 1,则会将 ECRx.EOV 位置 1;

-

ICU 通过中断控制器向安全管理模块 SMU 发送警告信息,SMU 根据设置决定是否将该错误信息提交给 CPU 处理;

-

ICUx 清除该 SRN 节点的中断请求;

-

CPU 接收到错误信息后,检查 ECRx.STAT 确定产生错误的 ICU,从中获取出错 SRN 节点的相关信息,同时,向 ECRx.STATCLR 写 1 清除 ECRx.STAT,CPU 通过读取 ECRx.EOV 确定是否产生了多个错误;

16.10.中断系统的使用

以下小节提供了 CPU/DMA 与 ICU 之间接口的简要说明

注意:中断控制器中所有 ICU 模块的基本功能相同

16.10.1.CPU 与 ICU 之间的接口

每个 CPU 在中断控制器中均有一个对应的 ICU,CPU 与 ICU 之间的接口由一个寄存器构成,CPU 从该寄存器中获取中断请求的具体信息(SRPN、ECC、SRN 索引),当 CPU 向 ICU 发送确认信息时,会将这些信息返回给 ICU,参考 16.4.1.8 小节

CPU 与 ICU 之间的接口包括 CPU 的中断控制寄存器 ICR,该寄存器中保存了如下信息:

-

CPU 的当前优先级 CCPN;

-

全局中断使能位 IE;

-

当前挂起中断请求的优先级 PIPN;

更多与 CPU-ICU 接口相关的信息可以参考 CPU 相关章节

16.10.2.DMA 与 ICU 之间的接口

每个 DMA 在中断控制器中均有一个对应的 ICU,DMA 接收到 ICU 发送的中断信息后,会触发对应的 DMA 通道,并立即向 ICU 发送确认信息,同时,ICU 会清除该中断请求对应的 SRN 节点的相关信息

DMA 与 ICU 之间的接口由一组寄存器构成,DMA 从这些寄存器中获取中断请求的具体信息(SRPN、ECC、SRN 索引),DMA 会在下一个时钟周期将这些信息返回给 ICU,同时向 ICU 发送确认信息,参考 16.4.1.8 小节

DMA 通道的优先级方案与 SRPN 采取的方案相同:

-

DMA 中优先级最低的通道:CH0;

-

中断控制器中优先级最低的中断请求:SRPN = 0;

16.10.3.软件中断源

任何服务请求节点均可以用于触发软件中断,软件可以通过将 SRN 对应的 SRC.SRR 位置 1 触发该节点的中断请求,因此,软件可以触发中断请求,这些中断请求的处理逻辑和硬件中断请求的处理逻辑一致

当 SRN 节点的 SRR 位被置 1 后,无法区分该中断请求是由软件发起的还是由硬件发起的,因此,软件应该使用未被硬件占用的 SRN 节点以及 SRPN 值

中断控制器为每个 CPU 提供了多组通用服务请求节点(GPSR),这些 SRN 节点支持软件中断,每个 CPU 拥有一个 GPSR 组,该 GPSR 组内包含 8 个 SRN 节点,这些节点不与内部或外部硬件中断源连接,且仅用于触发软件中断,这些 SRN 节点称为通用服务请求 SRN 节点SRC_GPSRxy(x 为组编号,y 为该组内 SRN 节点的编号)

除此以外,任何未使用的 SRN 节点均可以用于触发软件中断

16.10.4.外部中断源

中断控制器拥有 8 个保留的 SRN 节点(Int_SCUSRC[7:0])用于处理外部中断,可以产生中断请求的外部 GPIO 端口的输入设置(电平、触发沿等配置)由外部请求单元 ERU(External Request Unit)控制,ERU 模块的功能在 SCU 模块对应的章节中进行介绍

16.11.使用示例

本节介绍中断控制器和 OTGS 的使用示例

16.11.1.中断服务的使用示例

本小节介绍如何组织 TriCore 的中断向量表

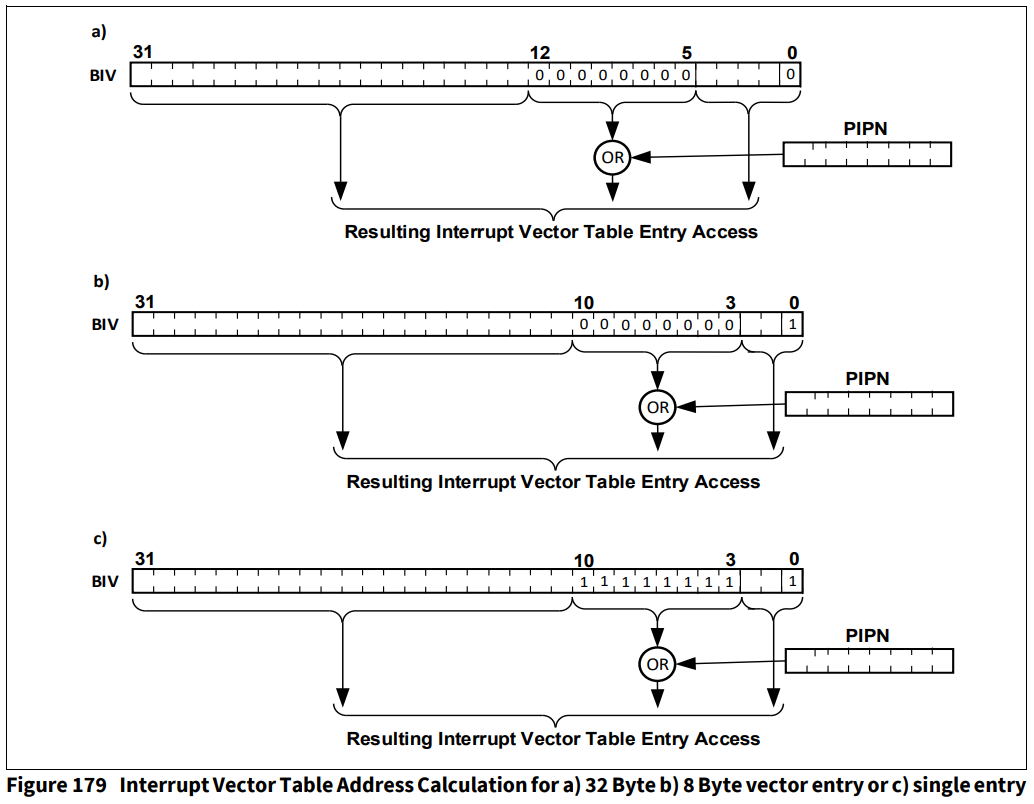

TriCore 架构接受中断请求后,会从 BIV 寄存器中获取中断向量表的起始地址,并结合该中断请求的优先级(PIPN),计算出对应中断向量的地址,TriCore TC1.6P 和 TC1.6E 架构允许配置中断向量表中的节点是占用 32 字节(图 179.a)还是 8 字节(图 179.b),极端情况下,可以通过屏蔽 PIPN 使中断向量表仅包含一个节点(图179.c)

如果配置中断向量节点的大小为 32 字节,那么简易的中断服务程序可以直接存储到该节点中(在中断向量中存储所有中断服务程序的代码),中断服务程序甚至可以占用多个向量节点(参考架构手册中的描述),如果向量表存储在代码段中,就可以实现快速响应中断

如果配置中断向量节点的大小为 8 字节,则中断向量表仅能存储一条 CALL 指令和一条 RET 指令

TriCore 编译器支持通过关键字或函数生成中断向量表

如果 BIV 寄存器屏蔽了 PIPN 字段,则可以生成最小的中断向量表(中断向量表仅包含一个中断向量),所有中断向量的地址均相同,例如:

__mtcr(BIV,0x80000001 | 0xFF<<3); // move to core register BIV这种配置使所有中断共享一个中断向量入口,然后再通过函数指针引导至特定的中断服务程序执行,这种方式可以实现快速切换中断服务程序

中断相关初始化的步骤

-

Line 1:定义中断向量 ISR 指针数组,最大支持 255 个中断向量;

-

Line 2:定义一个指向中断向量指针数组起始位置的指针;

-

Line 3:执行函数 interruptHandlerInstall(),该函数载入数组中的中断服务程序(通过中断优先级和中断节点的地址);

-

Line 4:存储数组中 ISR 的地址;

-

Line 5~6:路由至对应的中断服务程序,在中断产生后立即调用;

-

Line 7:中断服务程序执行完毕后,提供返回指令;

中断相关初始化的步骤 - C 代码示例

void (*isr_pointer_array[256])(void);

void (**isr)(void) = isr_pointer_array;

void interruptHandlerInstall(long int SRprio, long int addr)

{

*isr_pointer_array[SRprio]=addr;

}

void interruptHandler(void)

{

isr[__mfcr(ICR) & 0xFF]();

asm (" rfe"); // return from event

} 中断向量的入口地址存储在一个数组中,而不是将其编码至指令中,函数 interruptHandlerInstall() 负责组织中断向量表中的中断向量(在各个模块对应的中断处理程序中查看其具体用法,例如,STM 章节的使用示例)

这种生成中断向量表的方式有时更加灵活(相较于 8 字节中断节点长度的用法),并且不需要编译器进行特定的支持

注意:系统允许产生中断前,必须允许全局中断(ICR.IE = 1),中断控制寄存器 ICR 的中断使能位 IE 控制是否允许 CPU 处理中断,大多数编译器都支持通过 __enable()(或相似指令)设置 ICR.IE(更多信息可参考架构手册)

16.12.模块实现

16.12.1.中断控制器的特性

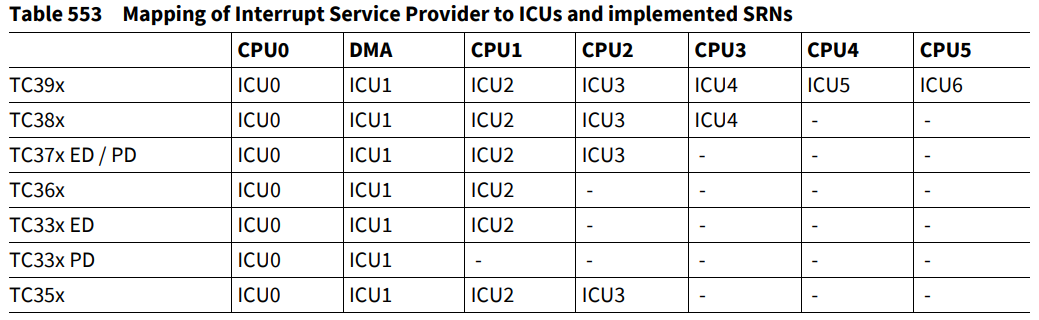

表 553 展示了 TC3XX 不同平台中,中断控制器的特性

相邻的 ICU 对(如 ICU0 和 ICU1、ICU2 和 ICU3、...)可以实现一起执行中断仲裁(将两个 ICU 中的中断请求放在一起进行仲裁)

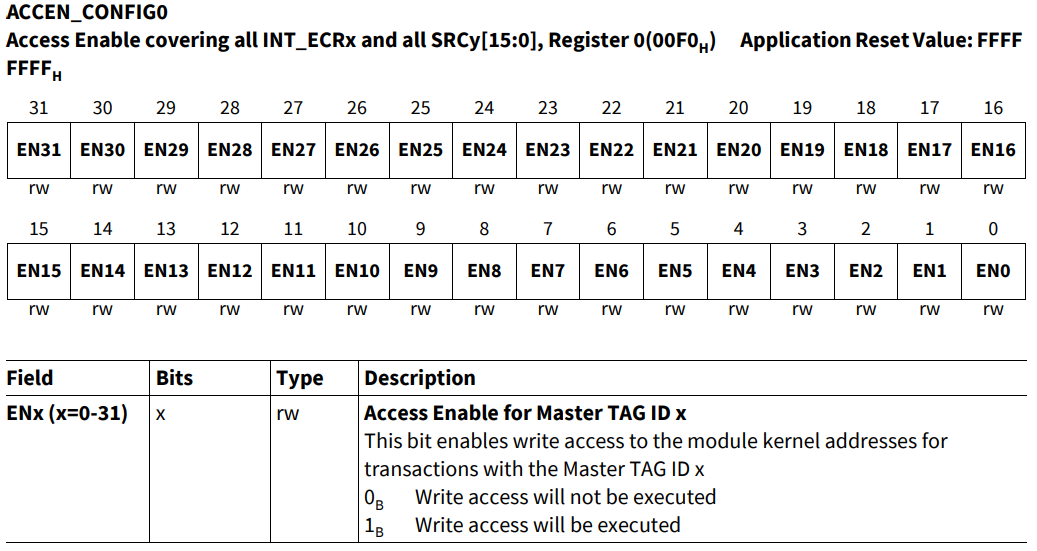

16.13.中断控制器相关的寄存器

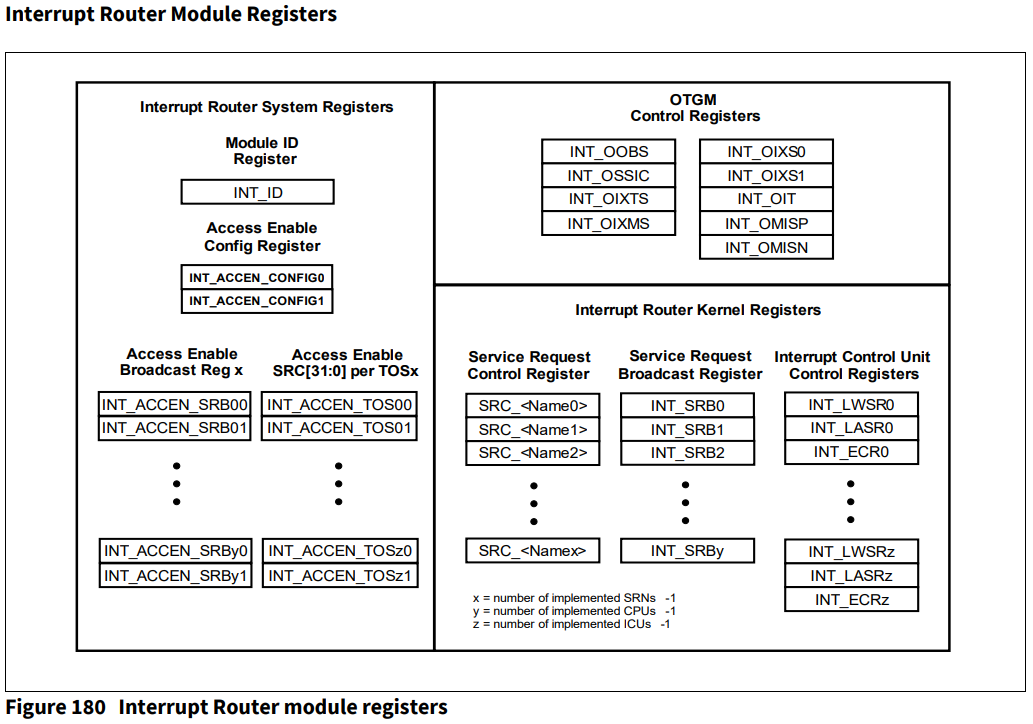

图 180 展示了与中断控制器相关的所有寄存器

中断控制器分配了两组寄存器地址:

-

2 * 256 字节的地址空间,包含中断控制器的所有系统寄存器、ICU 控制寄存器以及 OTGM 寄存器;

-

8K 字节的地址空间,包含了所有的服务请求控制寄存器 SRC;

权限控制寄存器缩写列表

-

P0 对应 ACCEN_SRBx:控制对应 SRBx 寄存器的写入权限,服务请求广播寄存器 SRB 及其对应的 ACCEN_SRB 寄存器的数量,与 CPU 核心的数量相等;

-

P1 对应 ACCEN_CONFIG:控制所有 SRCx 寄存器第 0~15 位的写入权限,以及 ICUx 错误捕获寄存器 ECRx 的写入权限;

-

P2 对应 ACCEN_SRC_TOSx:控制所有 SRCx 寄存器第 16~31 位的写入权限,每个 ICU 均有一个对应的 ACCEN_SRC_TOS 寄存器;

注意:如果写入寄存器时违反了写入权限(例如,通过 SPB 总线写入受 Px/ACCEN 保护的寄存器,但是该 SPB 总线的 TAG ID 并未被对应的 Px/ACCEN 寄存器所允许),则本次写入无效,并且会向 SMU 发送警告信息,除此以外不会执行其他操作(如产生错误、中断、Trap 等)

16.13.1.系统和控制寄存器

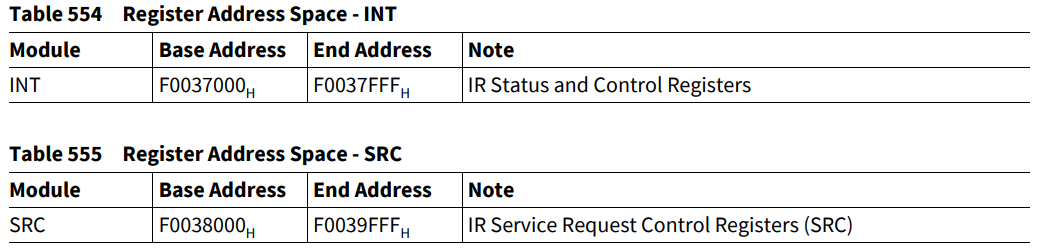

模块标识寄存器 - ID

中断控制器模块标识寄存器

-

MOD_REV:Module Revision Number,该字段定义了模块的版本编号,版本编号的起始值为 0x01(第一版);

-

MOD_TYPE:Module Type,该字段设置为 0xC0,表示该模块为 32-bit 的模块;

-

MOD_NUMBER:Module Number Value,该字段定义了模块的标识编号(ID),中断控制器的 ID 为 0x009B;

服务请求广播寄存器 x - SRBx

中断服务请求广播寄存器可用于同时触发一个通用服务请求组内的多个中断请求

-

TRIGi(i = 0~7):General Purpose Service Request Trigger i,读取该位只会返回 0:

-

0B:不执行任何操作;

-

1B:触发 GPSRx 内第 i 个 SRN 节点的服务请求;

-

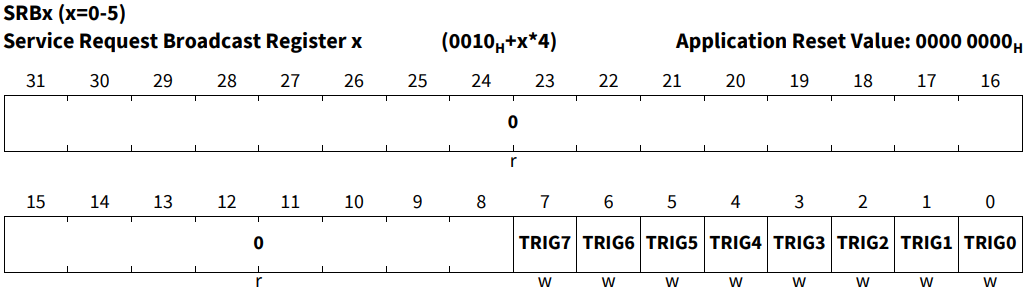

INT_ECRx 和 SRCy[15:0] 写入权限控制寄存器 0 - ACCEN_CONFIG0

TAG ID 的范围 000000B ~ 011111B,定义该范围内,哪些 TAG ID 被允许执行 SRC[15:0] 和 ECR 寄存器的写入操作(更多信息请参考 16.8.1 小节)

-

ENx(x = 0~31):Access Enable for Master TAG ID x,允许具有 TAG IDx 的设备执行写入操作:

-

0B:不允许写入;

-

1B:允许写入;

-

INT_ECRx 和 SRCy[15:0] 写入权限控制寄存器 1 - ACCEN_CONFIG1

TAG ID 的范围 100000B ~ 111111B,定义该范围内,哪些 TAG ID 被允许执行 SRC[15:0] 和 ECR 寄存器的写入操作(更多信息请参考 16.8.1 小节)

TC3XX 平台未使用这些 TAG ID,因此这些寄存器仅可读,向其写值会被忽略

SRBx 写入权限控制寄存器 0 - ACCEN_SRBx0

TAG ID 的范围 000000B ~ 011111B,定义该范围内,哪些 TAG ID 被允许执行 INT_SRBx 寄存器的写入操作(更多信息参考 16.7.3 小节)

-

ENi(i = 0~31):Access Enable for Master TAG ID i,允许具有 TAG IDi 的设备执行写入操作:

-

0B:不允许写入;

-

1B:允许写入;

-

SRBx 写入权限控制寄存器 1 - ACCEN_SRBx1

TAG ID 的范围 100000B ~ 111111B,定义该范围内,哪些 TAG ID 被允许执行 INT_SRBx 寄存器的写入操作(更多信息参考 16.7.3 小节)

TC3XX 平台未使用这些 TAG ID,因此这些寄存器仅可读,向其写值会被忽略

SRCx[31:16] 的写入权限控制寄存器 0 - ACCEN_SRC_TOSx0

TAG ID 的范围 000000B ~ 011111B,定义该范围内,哪些 TAG ID 被允许执行 SRC 寄存器第 15~31 位的写入操作(更多信息参考 16.4.1.3 小节)

注意:这些 SRCx 寄存器对应的 SRN 节点通过 TOSx 进行映射(SRCy.TOS = x)

-

ENi(i = 0~31):Access Enable for Master TAG ID i,允许具有 TAG IDi 的设备执行写入操作:

-

0B:不允许写入;

-

1B:允许写入;

-

SRCx[31:16] 的写入权限控制寄存器 1 - ACCEN_SRC_TOSx1

TAG ID 的范围 100000B ~ 111111B,定义该范围内,哪些 TAG ID 被允许执行 SRC 寄存器第 15~31 位的写入操作(更多信息参考 16.4.1.3 小节)

TC3XX 平台未使用这些 TAG ID,因此这些寄存器仅可读,向其写值会被忽略

16.14.OTGM 寄存器

执行 Debug Reset 和系统复位(且 OCDS 已禁用)操作时,会复位所有的 OTGM 寄存器,若系统复位时 OCDS 为启用状态,则不会进行 OTGM 复位操作

仅当系统为 Supervisor 模式,且 OCDS 以启用时,才可以对 OTGM 执行写入操作,且必须一次性写入全部的 32-bit

16.14.1.状态和控制

OTGM OTGB0/1 状态寄存器 - OOBS

注意:OTGB0/1 寄存器的值只会被采样而不会被捕获(保存),只有 OTGS 寄存器提供了保存捕获值的寄存器

-

OTGB0:Status of OTGB0,OTGB0 的状态;

-

OTGB1:Status of OTGB1,OTGB1 的状态;

OTGM SSI 控制寄存器 - OSSIC

-

TGS:Trigger Set for OTGB0/1,OTGB0/1 的触发集合:

-

00B:无 Trigger Set 输出;

-

01B:Trigger Set TS16_SSI;

-

其他:保留值(未选择 Trigger Set);

-

-

TGB:OTGB0/1 Bus Select,OTGB0/1 总线选择:

-

0B:OTGB0 输出 Trigger Set;

-

1B:OTGB1 输出 Trigger Set;

-

16.14.2.IRQ 复用控制

OTGM IRQ 复用 Trigger Set 选择寄存器 - OIXTS

-

TGS:Trigger Set Select for OTGB0/1 Overlay,OTGB0/1 叠加触发器设置选择:

-

00B:无叠加;

-

01B:Trigger Set TS8_IS;

-

10B:Trigger Set TS8_SPA;

-

其他:保留值(未选择 Trigger Set);

-

-

OBS:Overlay Byte Select,叠加字节选择:

-

00B: OTGB0 [7:0];

-

01B:OTGB0 [15:8];

-

10B:OTGB1 [7:0];

-

11B:OTGB1 [15:8];

-

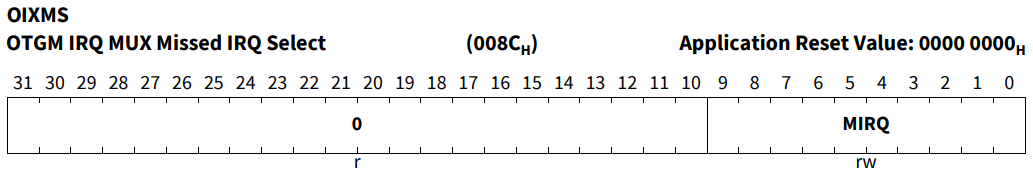

OTGM IRQ 复用 Missing IRQ 选择寄存器 - OIXMS

-

MIRQ:SRN Index for Missed Interrupt Trigger,未触发中断的 SRN 节点索引;

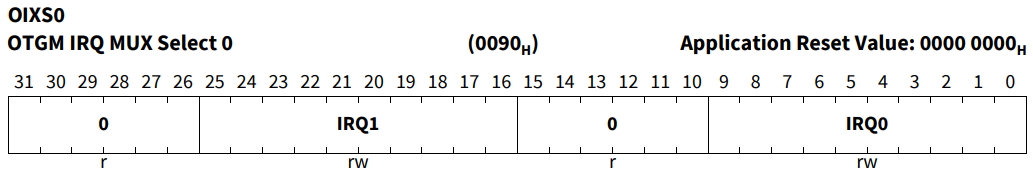

OTGM IRQ 复用选择寄存器 0 - OIXS0

-

IRQ0:SRN Index for Interrupt Trigger 0,中断触发器 0 的 SRN 索引;

-

IRQ1:SRN Index for Interrupt Trigger 1,中断触发器 1 的 SRN 索引;

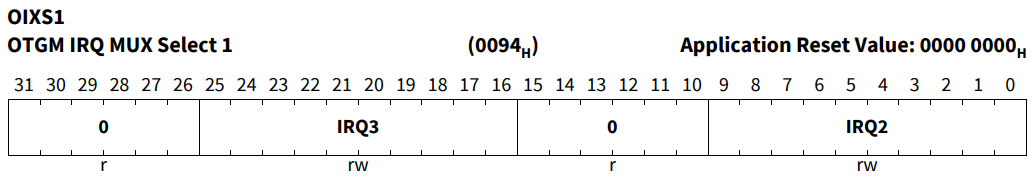

OTGM IRQ 复用选择寄存器 1 - OIXS1

-

IRQ2:SRN Index for Interrupt Trigger 2,中断触发器 2 的 SRN 索引;

-

IRQ3:SRN Index for Interrupt Trigger 3,中断触发器 3 的 SRN 索引;

16.14.3.中断系统的 Trace

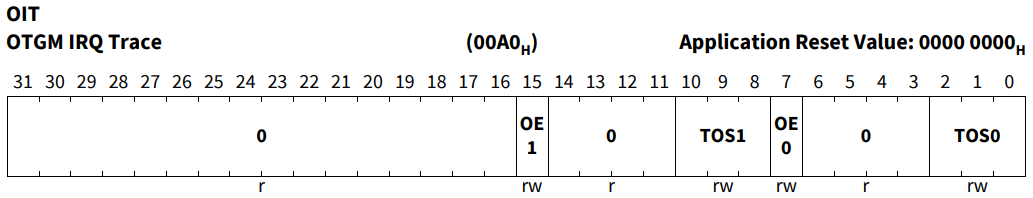

OTGM IRQ Trace

-

TOS0:Type of Service for Observation on OTGB0,OTGB0 需要观察的 CPU/DMA,Trigger Set TS16_SP,ISP 的编码:

-

000B:观测 CPU0;

-

001B:观测 DMA;

-

010B:观测 CPU1;

-

011B:观测 CPU2;

-

100B:观测 CPU3;

-

101B:观测 CPU4;

-

110B:观测 CPU5;

-

其他: 保留值 (无任何操作);

-

-

OE0:Output Enable for OTGB0,使能 OTGB0 的输出:

-

0B:禁用;

-

1B:启用;

-

-

TOS0:Type of Service for Observation on OTGB1,OTGB1 需要观察的 CPU/DMA,Trigger Set TS16_SP,ISP 的编码:

-

000B:观测 CPU0;

-

001B:观测 DMA;

-

010B:观测 CPU1;

-

011B:观测 CPU2;

-

100B:观测 CPU3;

-

101B:观测 CPU4;

-

110B:观测 CPU5;

-

其他: 保留值 (无任何操作);

-

-

OE1:Output Enable for OTGB1,使能 OTGB1 的输出:

-

0B:禁用;

-

1B:启用;

-

16.14.4.MCDS 接口

OTGM MCDS I/F 上升沿控制寄存器 - OMISP

-

OTGB0:Bitwise Posedge Sensitivity for OTGB0,OTGB0 上升沿敏感,如果某位被设置,OTGB 的值将在相关 OTGB0 位的上升沿写入 MCDS;

-

OTGB1:Bitwise Posedge Sensitivity for OTGB1,OTGB1 上升沿敏感,如果某位被设置,OTGB 的值将在相关 OTGB1 位的上升沿写入 MCDS;

OTGM MCDS I/F 下降沿控制寄存器 - OMISN

-

OTGB0:Bitwise Negedge Sensitivity for OTGB0,OTGB0 下降沿敏感,如果某位被设置,OTGB 的值将在相关 OTGB0 位的下降沿写入 MCDS;

-

OTGB1:Bitwise Negedge Sensitivity for OTGB1,OTGB1 下降沿敏感,如果某位被设置,OTGB 的值将在相关 OTGB1 位的下降沿写入 MCDS;

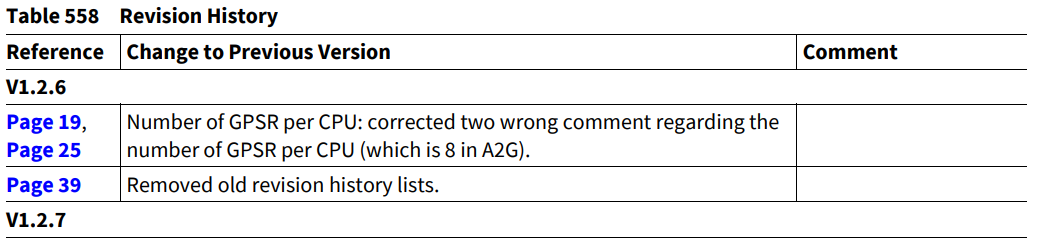

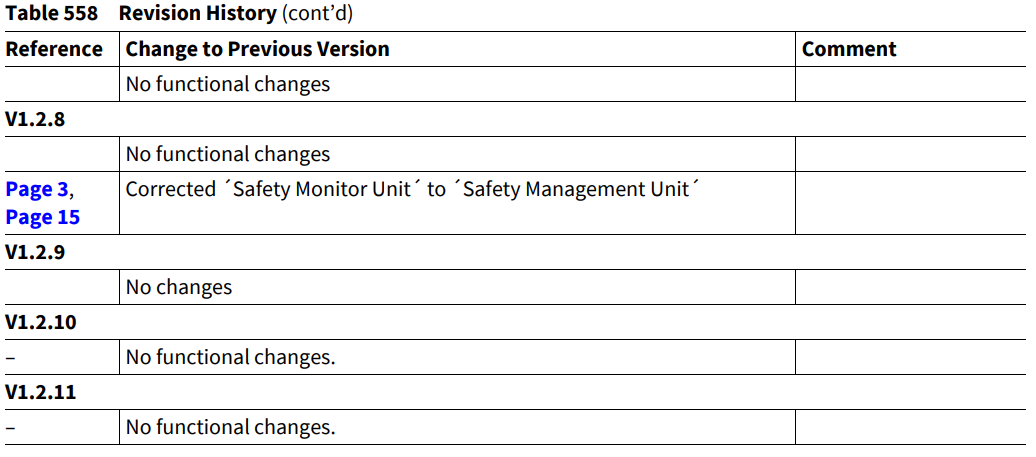

16.15.历史修订记录

6678

6678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?