注:无需移植跳转至生成比特流步骤即可。

一、IP移植

工程所用IP不涉及PS端arm内核,均在PL端,皆可移植至ZCU102。在vivado新建工程中设置好导出xci文件拷贝至对应文件夹(新增zcu102文件夹)即可,脚本运行时会自动添加对应ip

所使用PL端IP为:

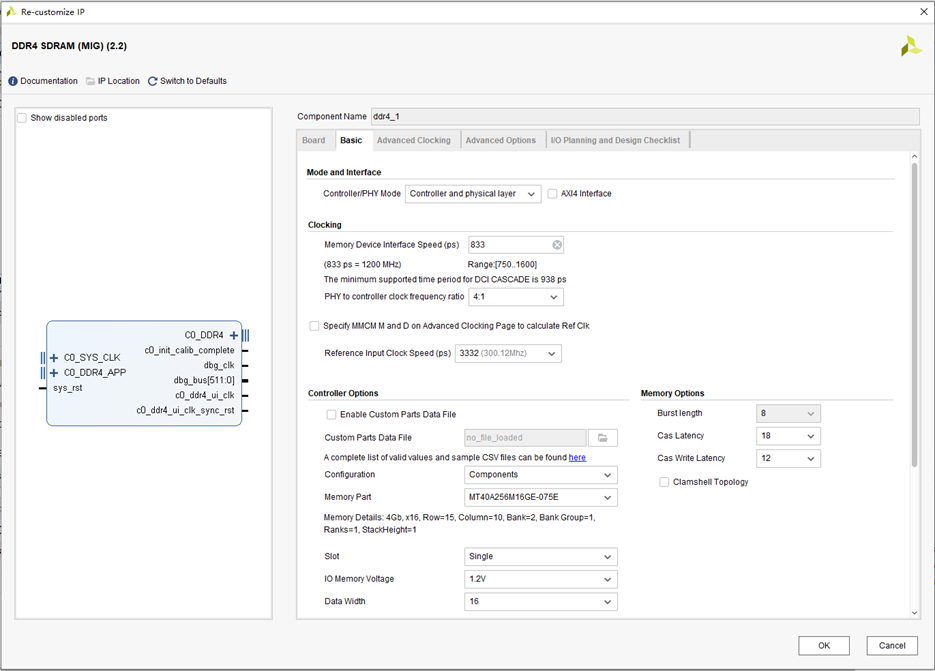

DDR4控制器(拷贝位置piton/design/chipset/mc/xilinx/zcu102/ip_cores/ddr4_0)

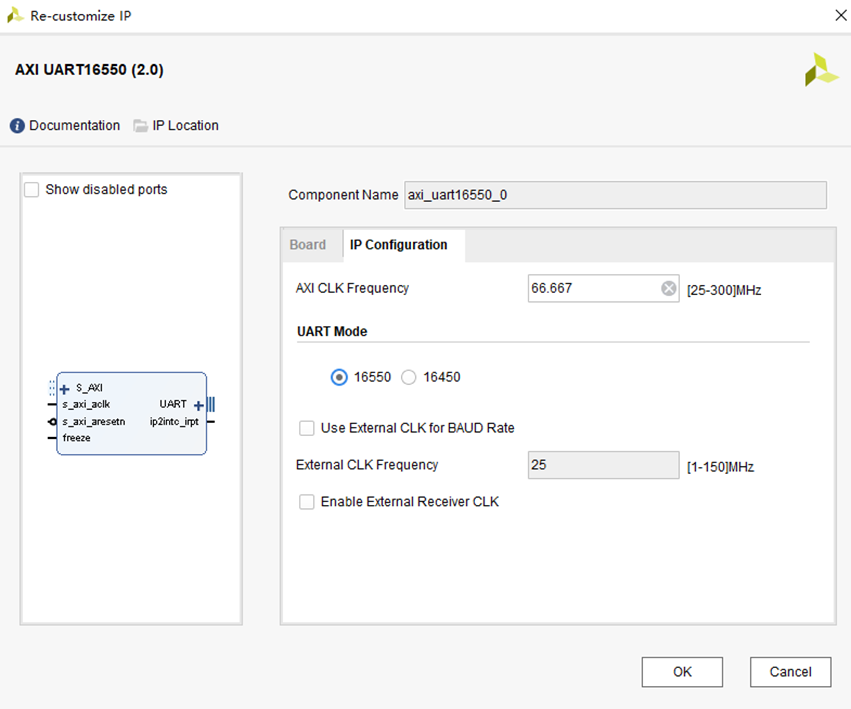

UART16550串口(拷贝位置/piton/design/chipset/io_ctrl/xilinx/zcu102/ip_cores/uart_16550

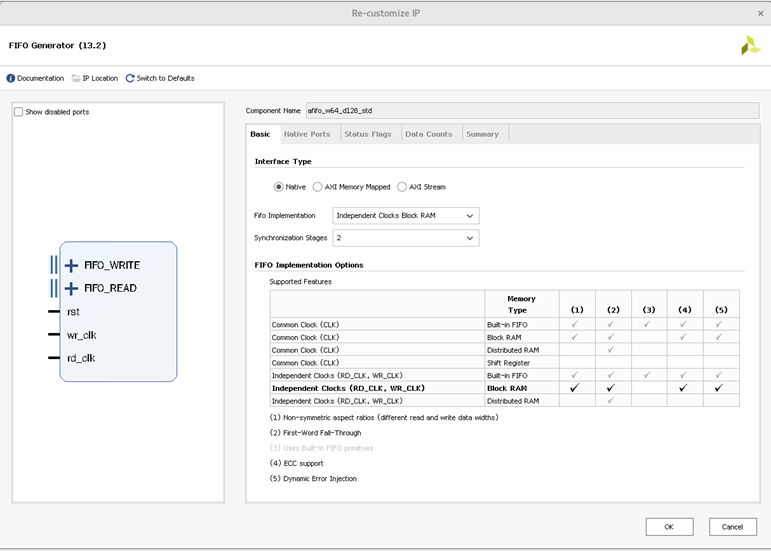

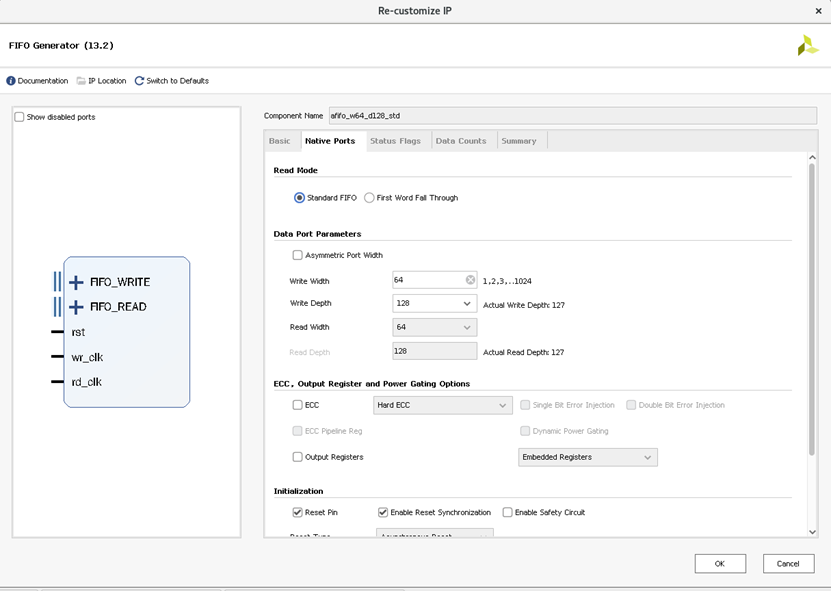

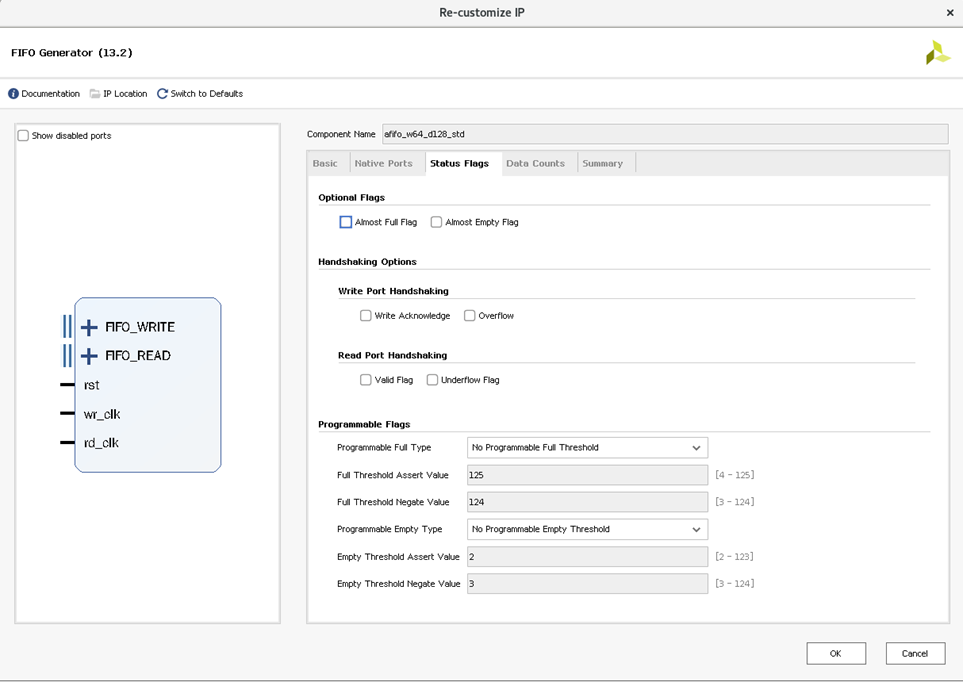

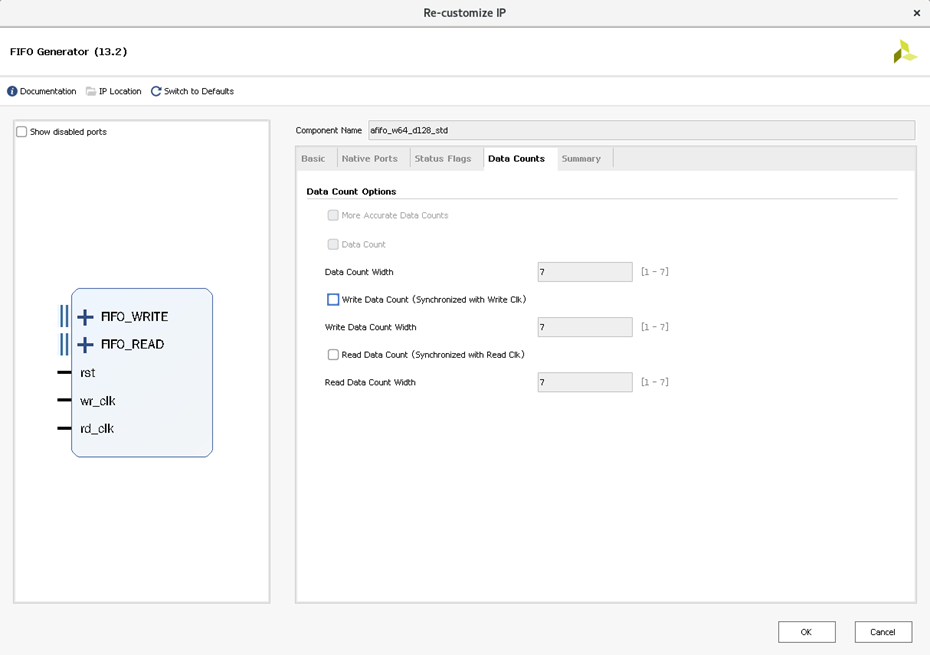

afifo_w64_d128(拷贝位置piton/design/chipset/Xilinx/zcu102/ip_cores/afifo_w64_d128_std)

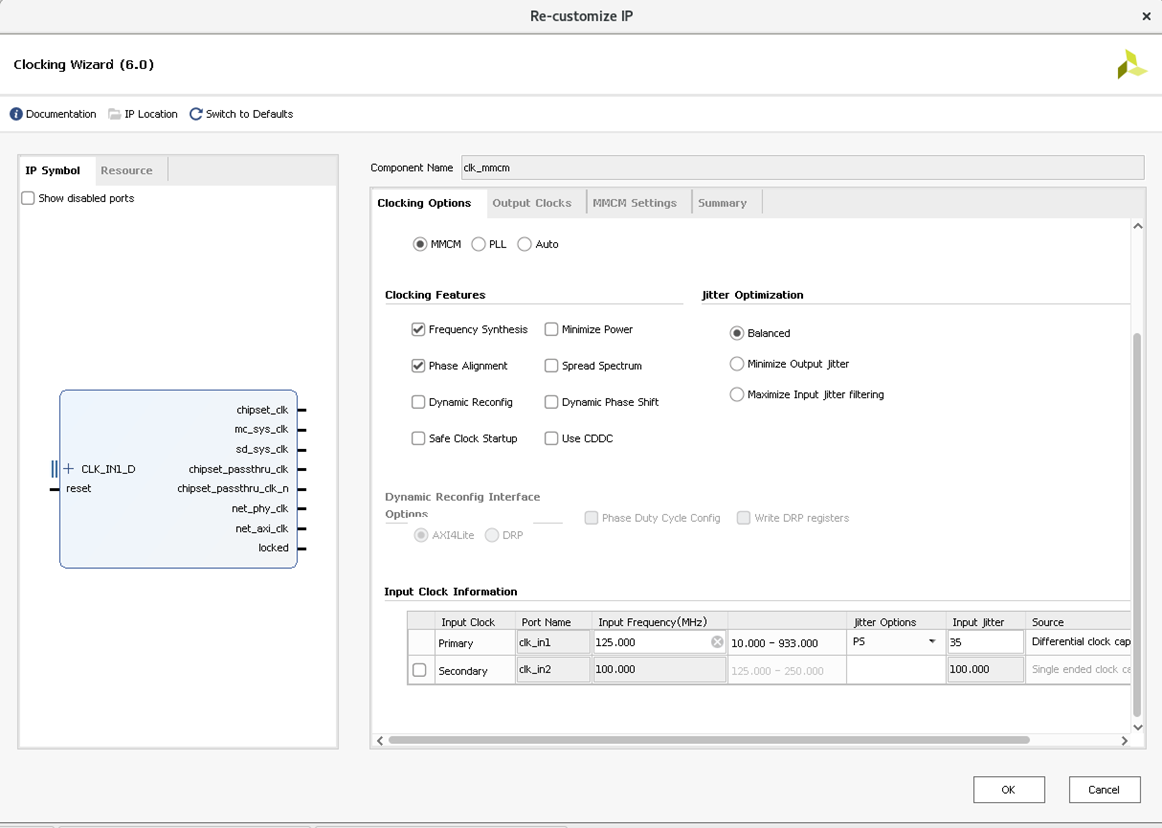

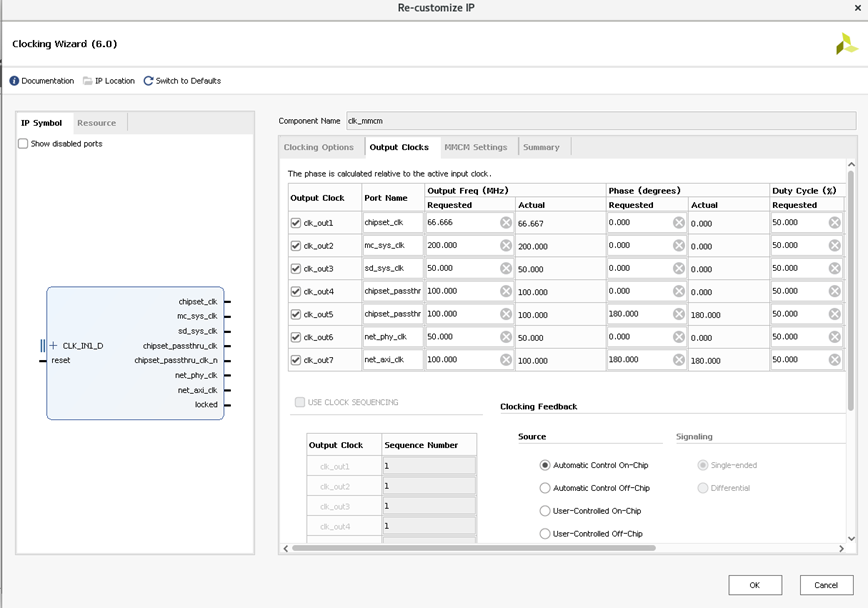

clk_mmcm时钟分频(拷贝位置/piton/design/chipset/xilinx/zcu102/ip_cores/clk_mmcm)

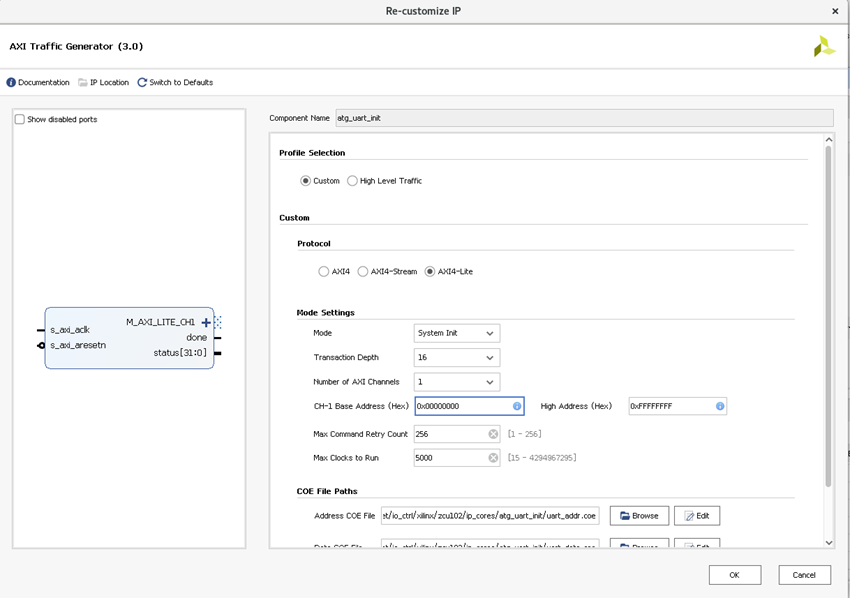

atg_uart_init串口初始化(拷贝位置piton/design/chipset/io_ctrl/xilinx/zcu102/ip_cores/atg_uart_init)

本文档详细记录了将Openpiton RISC-V处理器从Genesys2开发板移植到ZCU102 FPGA的过程,包括IP移植、宏定义修改、内存配置、外设列表更新、脚本调整等步骤,以及最终生成比特流和运行嵌入式程序的流程。

本文档详细记录了将Openpiton RISC-V处理器从Genesys2开发板移植到ZCU102 FPGA的过程,包括IP移植、宏定义修改、内存配置、外设列表更新、脚本调整等步骤,以及最终生成比特流和运行嵌入式程序的流程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

859

859

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?