PAE介绍:

PAE基址以及对36位物理寻址的支持,是在IA32架构的奔腾PRI处理器中采用的,如果想在IA32中实现这个特性通过CPUID指令的特性标志PAE(当CPUID指令源操作数2,EDX位6),CR4中的PAE标志可以开启PAE机制,将物理地址从32位扩展36位,所以需要地址总线增加4个。为了使用这个选项,必须设置如下标志:

1、CR0中的PG标志(开启分页)

2、CR4中的PAE标志(开启PAE)

注:开启PAE时,CR3(PDPR)中20位的页目录基址被27位的页目录指针表基地址所替代,此时CR3叫做PDPTR。

对比:

10-10-12分页寻址地址大小 0-0xFFFF FFFF;

PTT基址0xc0000000,PDT基址=c0000000/100000000×4M+c0000000=c030 0000

2-9-9-12分页寻址大小0-0XFFFF FFFF F

PTT基址0xc0000000,PDT基址=c0000000/100000000×8M+c0000000=C060 0000

2-9-9-12分页:

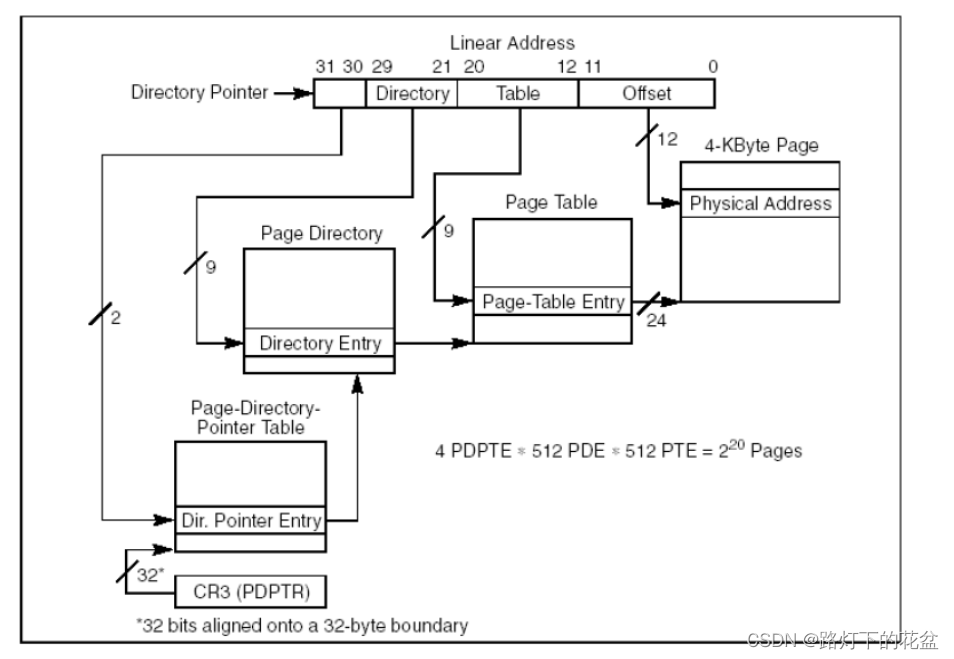

4KB页:

开启PAE机制进行线性地址到4KB页映射时,页目录表指针、页目录和页表的层次结构。这种分页可以寻址达到2^ 20个页,线性地址空间达到2^32字节(4GB)

线性地址分为4部分:

1、页目录指针表项(PDPTT):30-31位,给出了该页目录指针表项在页目录指针表中的偏移量,给出了页目录的基地址;

2、页目录项(PDT):21-29位,给出了在被选中的页目录中的偏移量。被选择的目录项给出了一个页表的基地址;

3、页表项(PTT):12-20位,给出了在被选中的页表中的偏移量,给出了一个页在内存中的基地址;

4、页偏移量:0-11位,给出了页中的偏移量。

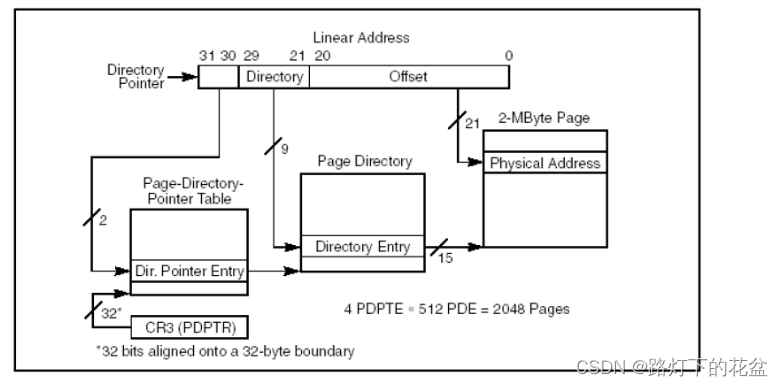

2MB页:

启用PAE且PS位置1时,线性地址分为3部分:

1、页目录指针表项(PDPTT):30-31位,给出了该页目录指针表项在页目录指针表中的偏移量,给出了页目录的基地址;

2、页目录项(PDT):21-29位,给出了在被选中的页目录中的偏移量。被选择的目录项给出了一个页表的基地址;

3、页偏移量:0-20位,给出了页中的偏移量。

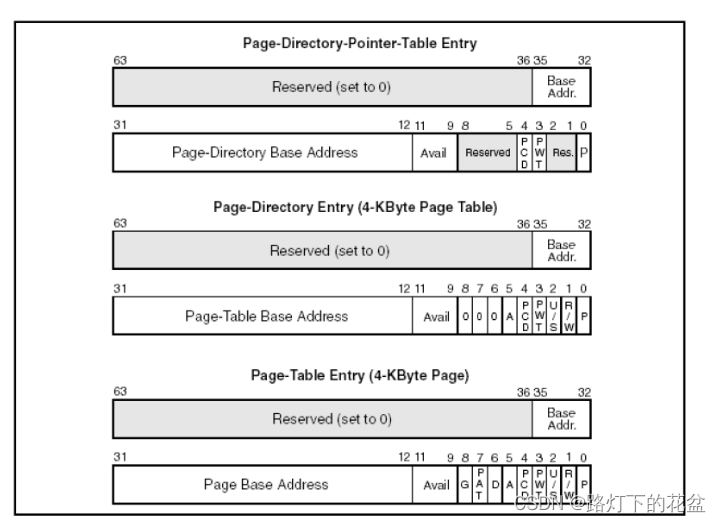

属性:

PDPTE有四项,页目录表基址+PDPTI8等于PDE;

页表基址+PDI9等于PTE;

物理页基址+12位的偏移等于物理地址

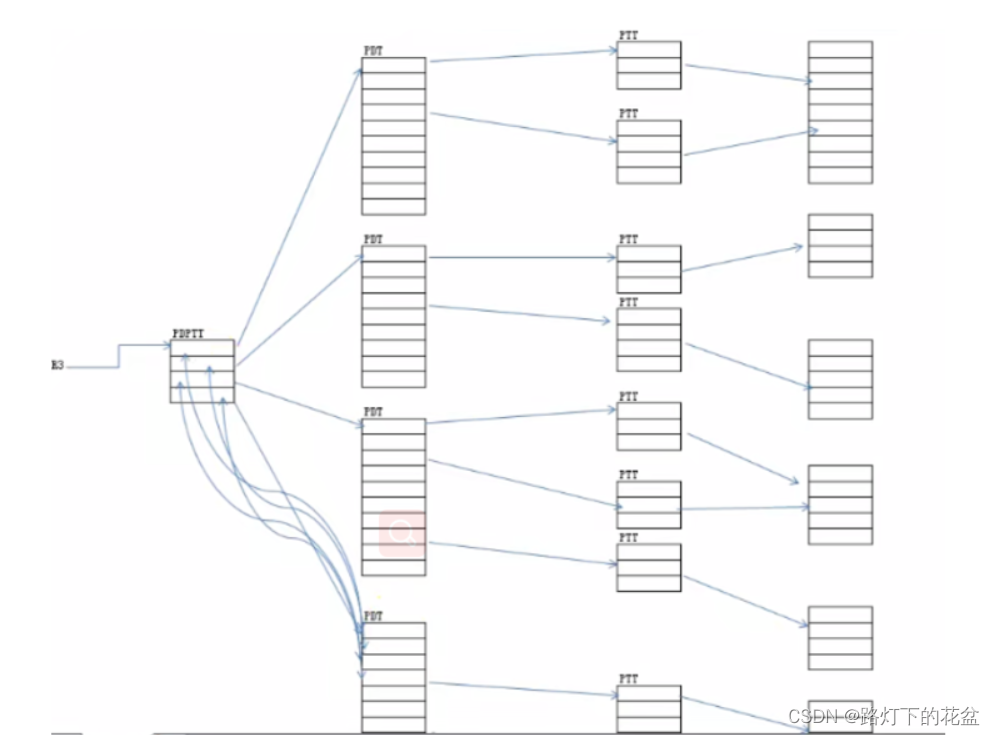

第四个PDT前四项指向PDPTT的四项。

C060 0000指向第一个PDPTE,C060 1000指向第二个,C060 2000 指向第三个,C060 0000指向第四个

地址拆分

#include "stdio.h"

int main(int argc, char* argv[])

{

int a=10;

printf("&a=%p",&a);

getchar();

return 0;

}

//0012FF7C

0000 0000 0001 0010 1111 F7C

00 0 PDPTI=0

0 0000 0000 0 PDI=0

1 0010 1111 12F PTI=12F

kd> !dq 0e5c0340 +0 PDPTE

kd> !dq 25c47000+0 PDE

kd> !dq 259ea000+ 12F*8 PTE

kd> !dq 25d2e000+f7c 物理地址

本文详细介绍了PAE(Physical Address Extension)在IA32架构中的作用,它允许处理器支持36位物理地址,扩展了寻址能力。内容包括如何通过CPUID和CR4标志开启PAE,以及2-9-9-12分页和2MB页两种情况下的线性地址转换。此外,还展示了线性地址的组成部分和实际地址拆分的示例。

本文详细介绍了PAE(Physical Address Extension)在IA32架构中的作用,它允许处理器支持36位物理地址,扩展了寻址能力。内容包括如何通过CPUID和CR4标志开启PAE,以及2-9-9-12分页和2MB页两种情况下的线性地址转换。此外,还展示了线性地址的组成部分和实际地址拆分的示例。

3544

3544

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?