要了解各种输出模式,三极管和MOS管是一个不能跳过的环节,因为输出模式的切换就是依赖于三极管和MOS管的状态。

1、MOS管与三极管

MOS管:

引脚名称:G:gate 栅极;S:source 源极;D:drain 漏极。

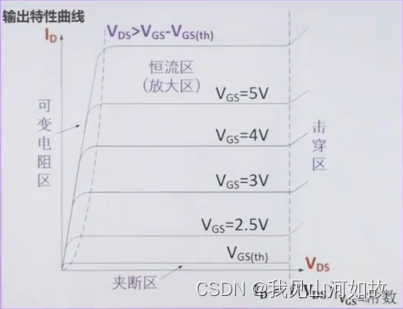

MOS管输出特性曲线

VGS < VGS(th)时,MOS管处于夹断区(截止区):

夹断区在输出特性最下面靠近横坐标的部分,表示MOS管不能导电,处在截止状态。电流ID为0,管子不工作。

VGS≥VGS(th),且VDS>VGS-VGS(th),MOS管进入恒流区:

恒流区在输出特性曲线中间的位置,电流ID基本不随VDS变化,ID的大小主要决定于电压VGS,所以叫做恒流区,也叫饱和区,当MOS用来做放大电路时就是工作在恒流区(饱和区)。

注:MOS管输出特性的恒流区(饱和区),相当于三极管的放大区。

VGS>VGS(th) ,且VDS < VGS - VGS(th),MOS管进入可变电阻区:

可变电阻区在输出特性的最左边,Id随着Vds的增加而上升,两者基本上是线性关系,所以可以看作是一个线性电阻,当VGS不同电阻的阻值就会不同,所以在该区MOS管相当就是一个由VGS控制的可变电阻。

击穿区:

随着VDS增大,PN结承受太大的反向电压而被击穿。

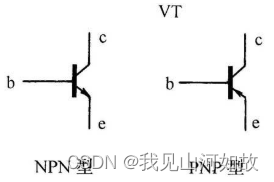

三极管

三极管是两个PN结的叠加,可以是PNP,也可以是NPN,故有三极,分别是发射极e (Emitter)、基极b (Base)和集电极c (Collector);发射区与基区形成的PN结为发射结;集电区与基区形成的PN结为集电结;

NPN三极管:

Vb<Ve (截止状态)

Vc>Vb>Ve(放大状态)

Vb>Ve Vb>Vc (饱和状态)

电流方向:Ice

PNP三级管:

Vb>Ve (截止状态)

Vc<Vb<Ve(放大状态)

Vb<Ve Vb<Vc(饱和状态)

电流方向:

Iec

2、上拉下拉

上拉电阻的作用:

在CMOS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻以降低输入阻抗, 提供泄荷通路。芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限,增强抗干扰能力;提高总线的抗电磁干扰能力,管脚悬空就比较容易接受外界的电磁干扰。

下拉电阻的作用:

提高芯片输入信号的噪声容限:输入端如果是高阻状态,或者高阻抗输入端处于悬空状态,此时需要加上拉或下拉,以免收到随机电平而影响电路工作。

同样如果输出端处于被动状态,需要加上拉或下拉,如输出端仅仅是一个三极管的集电极。从而提高芯片输入信号的噪声容限增强抗干扰能力。

区别:

含义不同;

- 上拉电阻:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平;

- 下拉电阻:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

作用不同:

- 上拉是对器件注入电流;灌电流;当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平;

- 下拉电阻:下拉是从器件输出电流;拉电流;当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平;

- 高阻态:高阻态这是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平。如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

3、开漏输出

常说的与推挽输出相对的就是开漏输出,对于开漏输出和推挽输出的区别最普遍的说法就是开漏输出无法真正输出高电平,即高电平时没有驱动能力,需要借助外部上拉电阻完成对外驱动。下面就从内部结构和原理上说明为什么开漏输出输出高电平时没有驱动能力,以及进一步比较与推挽输出的区别。

首先需要介绍一些开漏输出和开集输出。这两种输出的原理和特性基本是类似的,区别在于一个是使用MOS管,其中的"漏"指的就是MOS管的漏极;另一个使用三极管,其中的"集"指的就是MOS三极管的集电极。这两者其实都是和推挽输出相对应的输出模式,由于使用MOS管的情况较多,很多时候就用"开漏输出"这个词代替了开漏输出和开集输出。

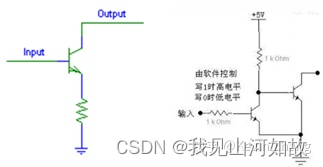

下图所示为开集输出,其原理电路如图所示。

左边为开集输出最基本的电路,当输入为高电平时,NPN三极管导通,Output被拉到GND,输出为低电平;当输入为低电平时,NPN三极管闭合,Output相当于开路(输出高阻)。高电平时输出高阻(高阻、三态以及floating说的都是一个意思),此时对外没有任何的驱动能力。这就是开漏和开集输出最大的特点,如何利用该特点完成各种功能稍后介绍。这个电路虽然完成了开集输出的功能,但是会出现input为高,输出为低;input为低,输出为高的情况。

右边的电路中多使用了一个三极管完成了"反相"。当输入为高电平时,第一个三极管导通,此时第二个三极管的输入端会被拉到GND,于是第二个三极管闭合,输出高阻;当输入为低电平时,第一个三极管闭合,此时第二个三极管的输入端会被上拉电阻拉到高电平,于是第二个三极管导通,输出被拉到GND。这样,这个电路的输入与输出是同相的了。

开漏输出原理与开集输出基本相同,只是将三极管换成了MOS而已。

开漏输出最主要的特性就是高电平没有驱动能力,需要借助外部上拉电阻才能真正输出高电平。

当MOS管闭合时,开漏输出电路输出高电平,且连接着负载时,电流流向是从外部电源,流经上来电阻RPU,流进负载,最后进入GND。

开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

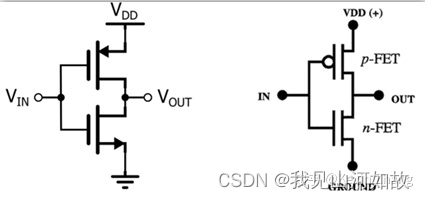

4、推挽输出

推挽输出结构是由两个MOS或者三极管收到互补控制的信号控制,两个管子时钟一个在导通,一个在截止。

推挽输出的最大特点是可以真正能真正的输出高电平和低电平,在两种电平下都具有驱动能力。

但推挽输出的一个缺点是,如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS闭合时;同时另一个输出低电平,即上面的MOS闭合,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。这也是为什么推挽输出不能实现" 线与"的原因。

参考:开漏输出、推挽输出的区别

1861

1861

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?