如果我写的文章对你能有些许帮助,说明我做的事还算有点意义,欢迎留个赞哦~

有问题恳请指出,也欢迎探讨qq815506713

专栏其他文章链接:

从零开始写riscv处理器(零)写在前面

从零开始写riscv处理器(一)指令集

从零开始写riscv处理器(二)简单数据通路

从零开始写riscv处理器(三)全部指令数据通路

从零开始写riscv处理器(四)流水线结构

从零开始写riscv处理器(五)数据冒险:停顿与前递

从零开始写riscv处理器(六)控制冒险:流水线冲刷

从零开始写riscv处理器(七)cache基础

从零开始写riscv处理器(八)cache进阶

-----------------------------分割线-----------------------------

1. 全部指令数据通路

上一篇文章以一个简单的数据通路作为引例,数据通路支持执行R型、BEQ指令、Load/Store型指令,并且你已经知道各指令的通路。现在直接给出补全所有指令的数据通路如下图所示:

2. 同之前的改变

- 主控单元增加了一个输入func3字段,输出多了memop信号,用于Load/Store类型指令加载/存储Word/HalfWord/Byte;

- 主控单元输出增加pc_rs1_sel信号,用去区分跳转地址是imm+pc还是imm+rs1(JAL、JALR);

- 主控单元删去Branch信号,改为由ALU单元直接输出跳转信号jump;

3. 各指令通路

各指令通路如下(有些类型的指令进一步细分了),同样地,暂不考虑控制单元。

R型指令数据通路:

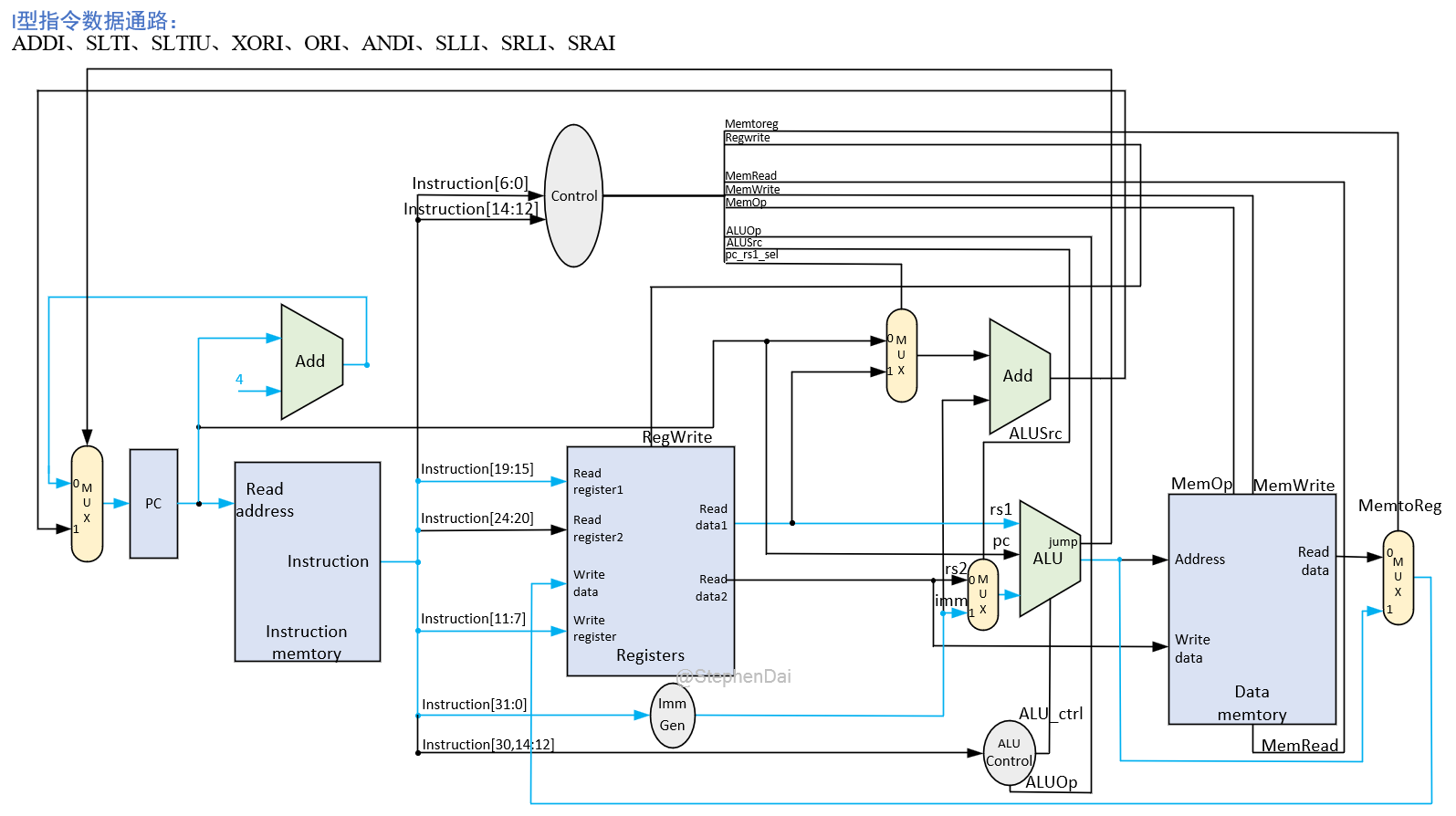

I型指令数据通路:

L型指令数据通路:

S型指令数据通路:

JALR型指令数据通路:

JAL型指令数据通路:

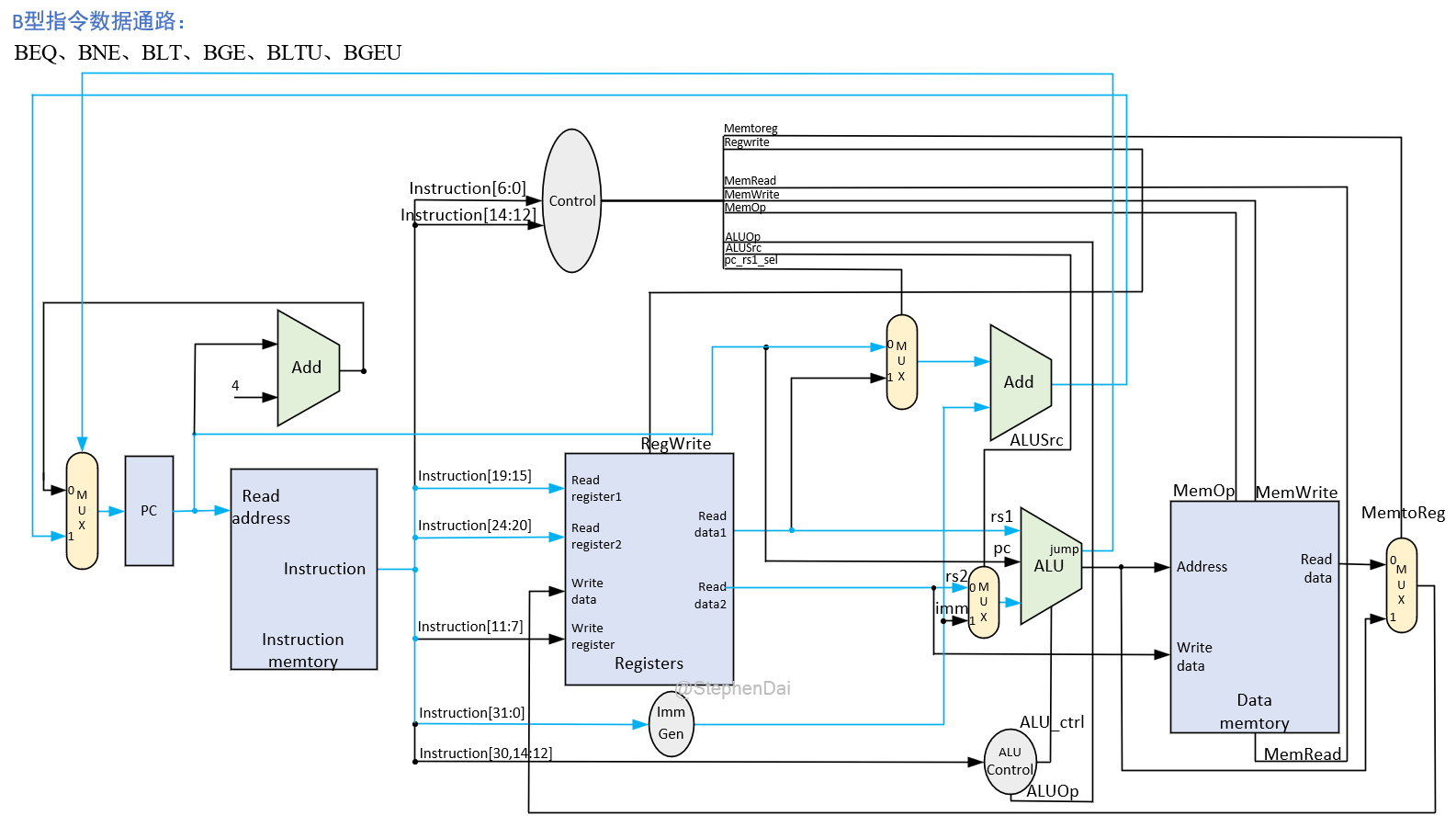

B型指令数据通路:

LUI型指令数据通路:

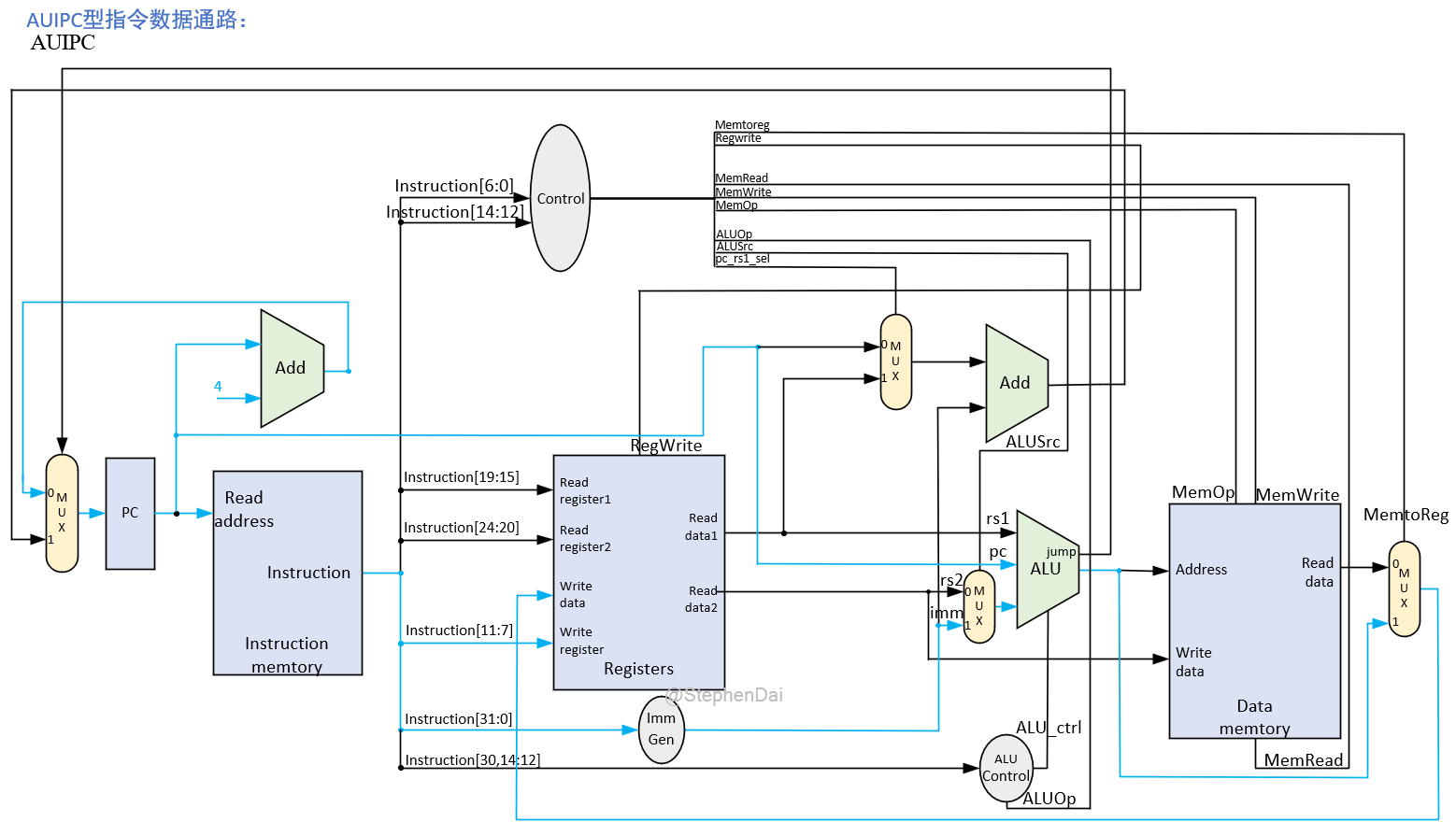

AUIPC型指令数据通路:

1106

1106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?