一、floating point 变量

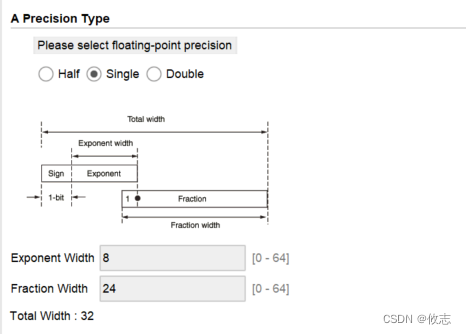

Floating Point 变量是用于表示实数的数据类型,允许包含小数,进行小数运算。浮点数用于处理器处理更高精度数值计算。浮点数的表示采用IEEE 754标准。

1 floating point 变量转换十进制规则

以32bit的 浮点数为例:

第1位表示 符号位

第2-9位表示 指数位

第10-32位表示 小数部分位数

https://tooltt.com/floatconverter/ 这里给出可以进行换算验证的网址。

具体的换算办法,先说

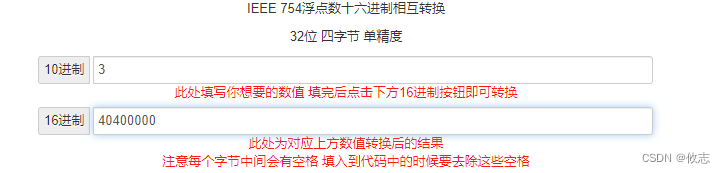

正数:

0 10000000 100_0000_0000_0000_0000_0000 (16进制:40400000)

符号位:0

指数位:10000000

小数位:100_0000_0000_0000_0000_0000

将指数减去偏置127, 10000000-0111_1111=1

2^1 =2 如果减去偏置后是n,那么获得2的n次方

小数:用二进制的计算规则 计算为 0.5。

所以结果是 : 2^1*1.5 =3

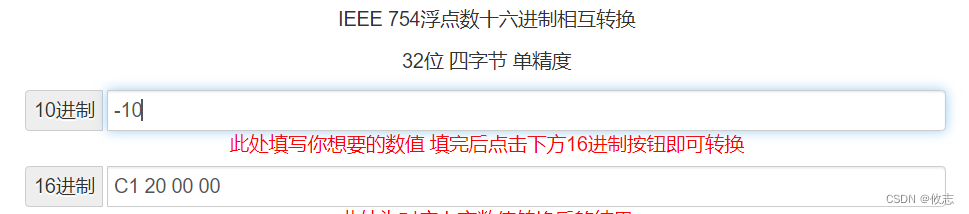

负数:

1 100_0001_0010_0000_0000_0000_0000_0000(C1200000)

符号位:1

指数位:10000010

小数位:010_0000_0000_0000_0000_0000

将指数减去偏置127,10000010-0111_1111=3

2^3 =8

小数:用二进制的计算规则 计算为 0.25。

所以结果是 : 2^3*1.25 =10

符号位为1,所以结果为-10

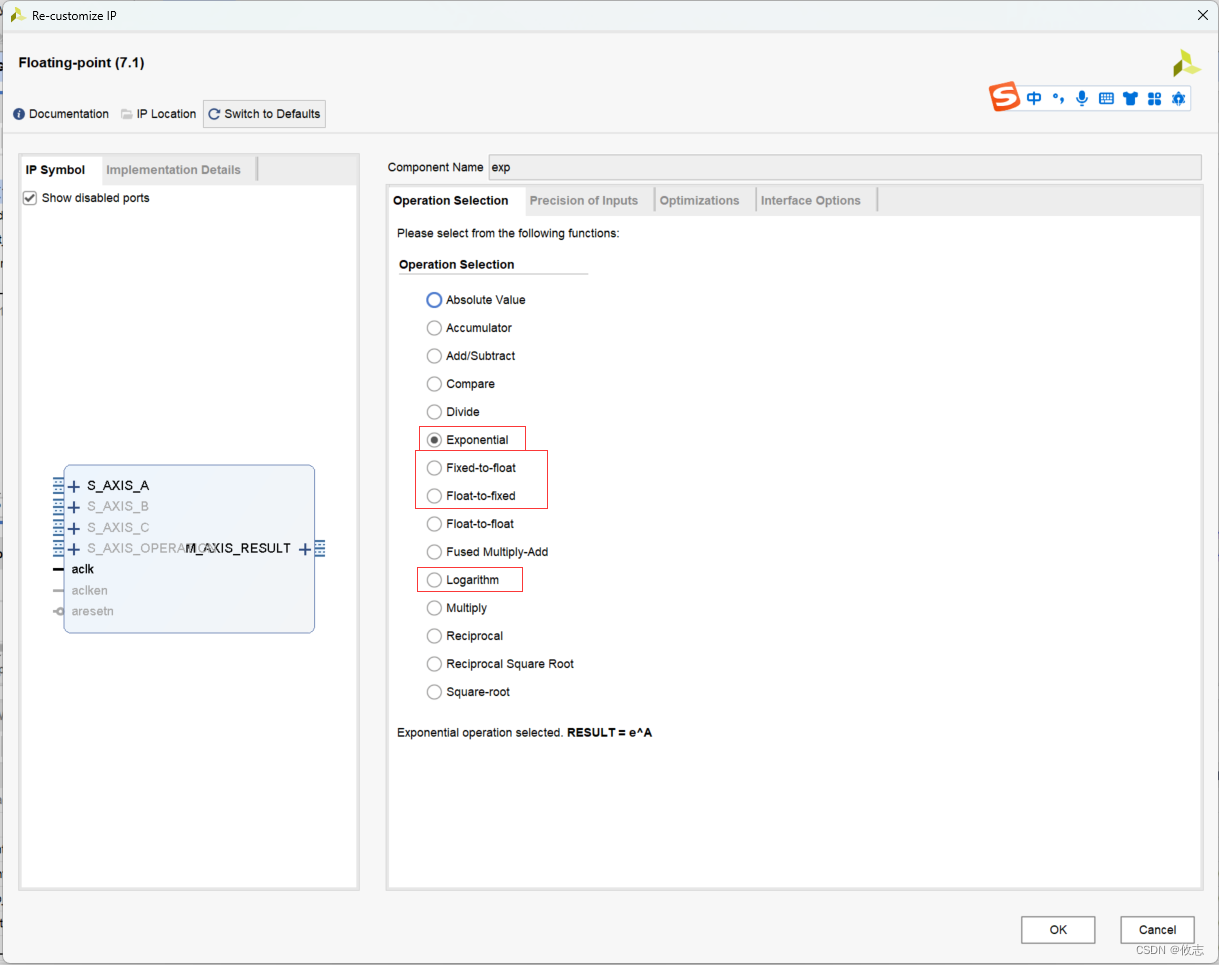

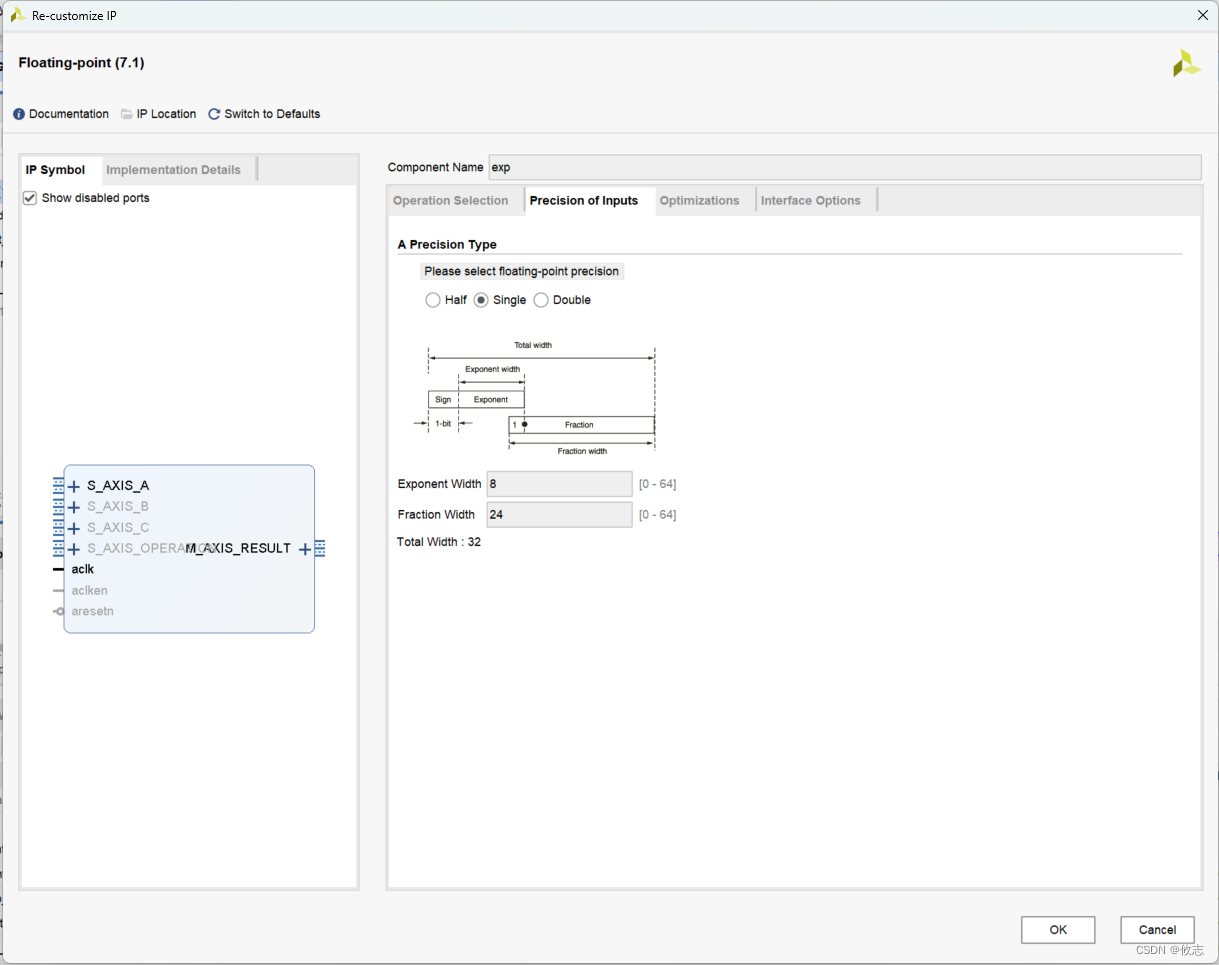

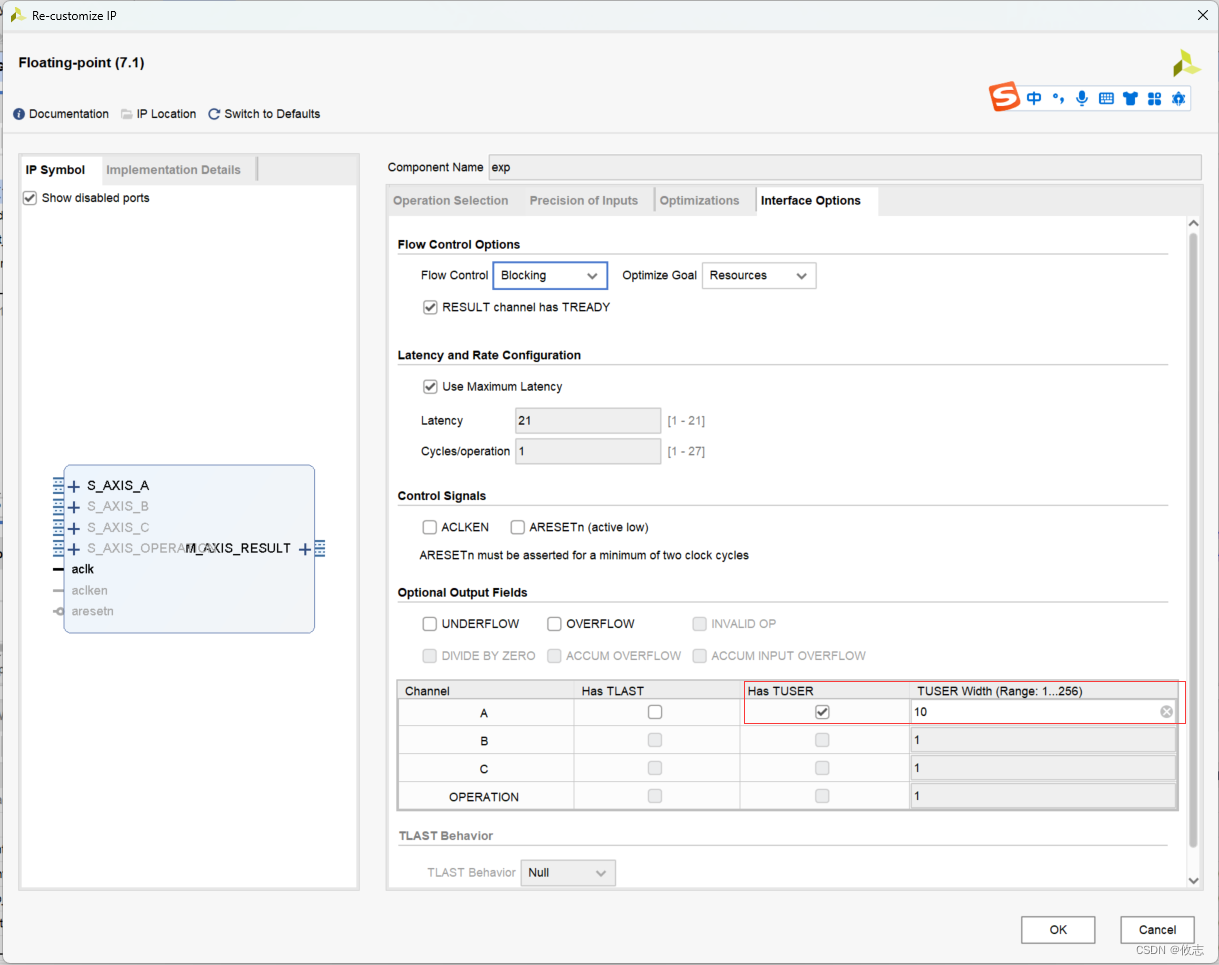

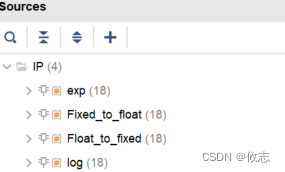

二、Vivado Floating Point IP核配置

这个IP核可意识先浮点数许多种运算,设置

本文以 Fixed to float(定点数转浮点数) Exponential(指数运算) Logarithm(对数运算)Float to fixed(浮点数转定点数) 为例,所有界面都除了选择

除了红色方框内的部分要设置,其余都保持默认,设置TUSER 标出数据的位置为方便大家观察对应位置数据是否计算正确。

三、Verilog代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/01/21 19:59:50

// Design Name:

// Module Name: IP_TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module IP_TEST(

input wire sys_clk ,

input wire rst_n ,

input wire signed [31:0] data ,

input wire data_valid ,

output wire m_axis_result_tvalid,

output wire [31:0] m_axis_result_tdata,

output wire [9:0] m_axis_result_tuser

);

//****************************************Fixed_to_float**********************************//

wire Fixed_to_float_s_axis_a_tready;

reg [9:0] Fixed_to_float_s_axis_a_tuser;

always@(posedge sys_clk or negedge rst_n)

if(!rst_n)

Fixed_to_float_s_axis_a_tuser<='d0;

else if(data_valid)

Fixed_to_float_s_axis_a_tuser<=Fixed_to_float_s_axis_a_tuser+1'b1;

else

Fixed_to_float_s_axis_a_tuser<='d0;

wire Fixed_to_float_axis_result_tvalid ;

wire signed [31:0] Fixed_to_float_axis_result_tdata ;

wire [9:0] Fixed_to_float_axis_result_tuser ;

wire exp_s_axis_a_tready;

Fixed_to_float Fixed_to_float_inst (

.aclk(sys_clk), // input wire aclk

.s_axis_a_tvalid(data_valid), // input wire s_axis_a_tvalid

.s_axis_a_tready(Fixed_to_float_s_axis_a_tready), // output wire s_axis_a_tready

.s_axis_a_tdata(data), // input wire [31 : 0] s_axis_a_tdata

.s_axis_a_tuser(Fixed_to_float_s_axis_a_tuser), // input wire [9 : 0] s_axis_a_tuser

.m_axis_result_tvalid(Fixed_to_float_axis_result_tvalid), // output wire m_axis_result_tvalid

.m_axis_result_tready(exp_s_axis_a_tready), // input wire m_axis_result_tready

.m_axis_result_tdata( Fixed_to_float_axis_result_tdata ), // output wire [31 : 0] m_axis_result_tdata

.m_axis_result_tuser( Fixed_to_float_axis_result_tuser ) // output wire [9 : 0] m_axis_result_tuser

);

//****************************************exp**********************************//

wire exp_axis_result_tvalid;

wire [31:0] exp_axis_result_tdata;

wire [9:0] exp_axis_result_tuser;

wire log_axis_a_tready;

exp exp_inst (

.aclk(sys_clk), // input wire aclk

.s_axis_a_tvalid(Fixed_to_float_axis_result_tvalid), // input wire s_axis_a_tvalid

.s_axis_a_tready(exp_s_axis_a_tready), // output wire s_axis_a_tready

.s_axis_a_tdata(Fixed_to_float_axis_result_tdata), // input wire [31 : 0] s_axis_a_tdata

.s_axis_a_tuser(Fixed_to_float_axis_result_tuser), // input wire [9 : 0] s_axis_a_tuser

.m_axis_result_tvalid(exp_axis_result_tvalid), // output wire m_axis_result_tvalid

.m_axis_result_tready(log_axis_a_tready), // input wire m_axis_result_tready

.m_axis_result_tdata (exp_axis_result_tdata), // output wire [31 : 0] m_axis_result_tdata

.m_axis_result_tuser(exp_axis_result_tuser) // output wire [9 : 0] m_axis_result_tuser

);

//****************************************log**********************************//

wire log_axis_result_tvalid;

wire signed [31:0] log_axis_result_tdata;

wire [9:0] log_axis_result_tuser;

wire Float_to_fixed_s_axis_a_tready;

log log_inst (

.aclk(sys_clk), // input wire aclk

.s_axis_a_tvalid(exp_axis_result_tvalid), // input wire s_axis_a_tvalid

.s_axis_a_tready(log_axis_a_tready), // output wire s_axis_a_tready

.s_axis_a_tdata(exp_axis_result_tdata), // input wire [31 : 0] s_axis_a_tdata

.s_axis_a_tuser(exp_axis_result_tuser), // input wire s_axis_a_tlast

.m_axis_result_tvalid(log_axis_result_tvalid), // output wire m_axis_result_tvalid

.m_axis_result_tready(Float_to_fixed_s_axis_a_tready), // input wire m_axis_result_tready

.m_axis_result_tdata(log_axis_result_tdata), // output wire [31 : 0] m_axis_result_tdata

.m_axis_result_tuser(log_axis_result_tuser) // output wire m_axis_result_tlast

);

//****************************************Float_to_fixed**********************************//

Float_to_fixed Float_to_fixed_inst (

.aclk(sys_clk), // input wire aclk

.s_axis_a_tvalid(log_axis_result_tvalid), // input wire s_axis_a_tvalid

.s_axis_a_tready(Float_to_fixed_s_axis_a_tready), // output wire s_axis_a_tready

.s_axis_a_tdata(log_axis_result_tdata), // input wire [31 : 0] s_axis_a_tdata

.s_axis_a_tuser(log_axis_result_tuser), // input wire [9 : 0] s_axis_a_tuser

.m_axis_result_tvalid(m_axis_result_tvalid), // output wire m_axis_result_tvalid

.m_axis_result_tready(1'b1), // input wire m_axis_result_tready

.m_axis_result_tdata (m_axis_result_tdata), // output wire [31 : 0] m_axis_result_tdata

.m_axis_result_tuser (m_axis_result_tuser) // output wire [9 : 0] m_axis_result_tuser

);

endmodule

四、仿真激励代码(tb文件)

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/01/21 20:06:05

// Design Name:

// Module Name: tb_IP_TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_IP_TEST(

);

//reg define

reg sys_clk;

reg sys_rst_n;

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//初始化系统时钟、全局复位和输入信号

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20;

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

reg signed [31:0] data;

reg data_valid;

reg [7:0] data_valid_cnt;

reg [31:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt<='d0;

else

cnt<=cnt+1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

data_valid<=1'b0;

else if(data_valid_cnt>='d50)

data_valid<=1'b0;

else if(cnt=='d1000)

data_valid<=1'b1;

else

data_valid<=data_valid;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

data_valid_cnt<='d0;

else if(data_valid==1'b1)

data_valid_cnt<=data_valid_cnt+1'b1;

else

data_valid_cnt<='d0;

//data

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

data<=-32'd10;

else if(data_valid==1'b1)

data<=data+1;

else

data<=data;

wire [31:0] m_axis_result_tdata;

wire m_axis_result_tvalid;

wire [9:0] m_axis_result_tuser;

IP_TEST IP_TEST_inst(

.sys_clk (sys_clk),

.rst_n (sys_rst_n),

.data (data),

.data_valid (data_valid),

.m_axis_result_tvalid (m_axis_result_tvalid),

.m_axis_result_tdata (m_axis_result_tdata),

.m_axis_result_tuser (m_axis_result_tuser)

);

endmodule

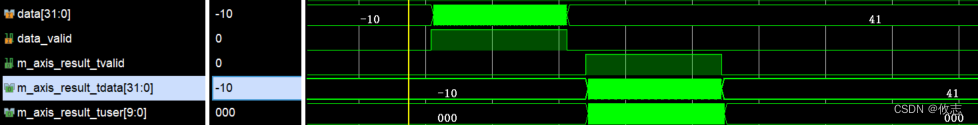

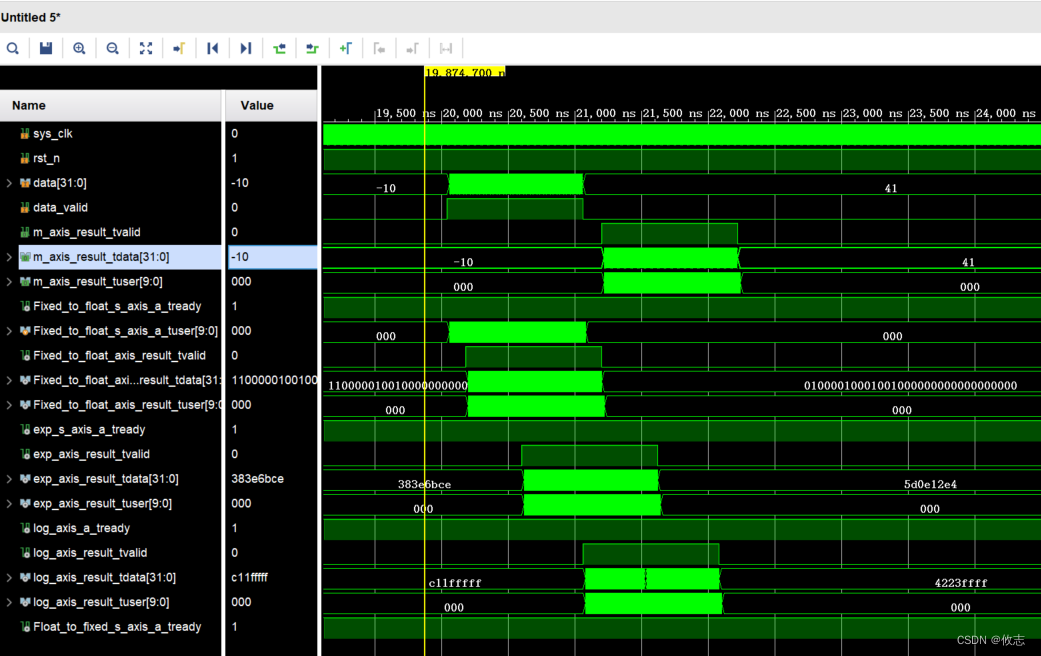

五、仿真结果

我们可以观察进行Fixed to float(定点数转浮点数) Exponential(指数运算) Logarithm(对数运算)Float to fixed(浮点数转定点数) 一系列操作后数据不变,验证通过。具体每个环节数据是怎么样的,大家自己观察,用在线进制转换-IEE754浮点数16进制转换 网站,验证计算是否正确。

本文详细介绍了浮动点变量在计算机中的表示方法,遵循IEEE754标准,以及如何在Vivado环境下配置FloatingPointIP核进行定点数和浮点数的转换运算。通过Verilog代码实例展示Fixedtofloat、Exponential、Logarithm等操作,并提供了仿真激励代码和结果验证方法。

本文详细介绍了浮动点变量在计算机中的表示方法,遵循IEEE754标准,以及如何在Vivado环境下配置FloatingPointIP核进行定点数和浮点数的转换运算。通过Verilog代码实例展示Fixedtofloat、Exponential、Logarithm等操作,并提供了仿真激励代码和结果验证方法。

1946

1946

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?