测试仿真流程

测试仿真环境为win系统下的quartus prime + modelsim

测试仿真流程参照我之前的教程

Verilog数字系统设计教程第4版夏宇闻——第三部分练习一

模块源代码

//----------alu.v----------

`define plus 3'd0

`define minus 3'd1

`define band 3'd2

`define bor 3'd3

`define unegate 3'd4

module alu(out,opcode,a,b);

output[7:0] out;

input[2:0] opcode;

input[7:0] a,b;

reg[7:0] out;

always@(opcode or a or b)

begin

case(opcode)

`plus: out = a + b; //加操作

`minus: out = a - b; //减操作

`band: out = a & b; //求与

`bor: out = a | b; //求或

`unegate:out = ~a; //求反

default: out = 8'hx; //未收到指令时,输出任意态

endcase

end

endmodule

测试模块代码

//----------alu.vt----------

`timescale 1 ns/ 1 ns

module alu_vlg_tst();

reg [7:0] a;

reg [7:0] b;

reg [2:0] opcode;

wire [7:0] out;

parameter times = 5;

initial

begin

a = {$random}%256;

b = {$random}%256;

opcode = 3'h0;

repeat(times)

begin

#100 a = {$random}%256;

b = {$random}%256;

opcode = opcode + 1;

end

#100 $stop;

end

alu i1 (

.a(a),

.b(b),

.opcode(opcode),

.out(out)

);

endmodule

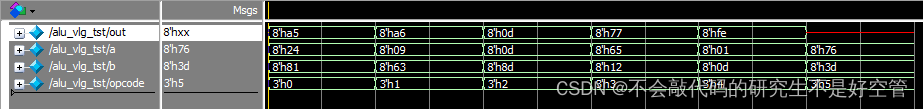

结果波形

1143

1143

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?