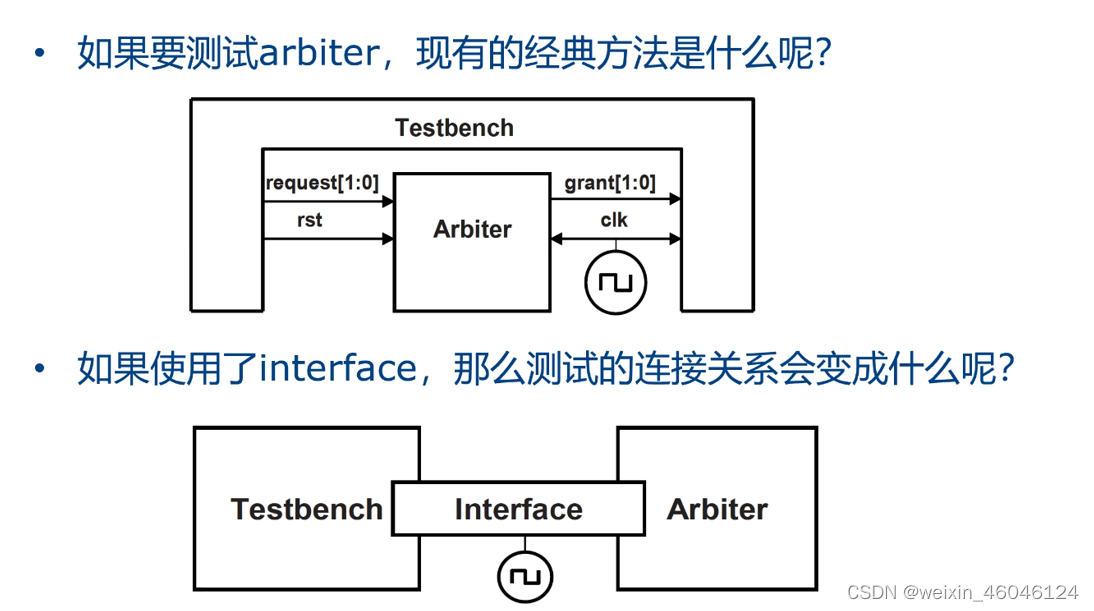

可以用来设计和验证,在验证时让连接更简洁

和module相似,可以定义端口,双向信号,可以用initial和always,可以定义function和task

可以在软硬件环境传递,可以作为module的端口列表,可以作为软件方法的形式参数(virtual)

interface arb_if(input bit clk);//接口定义 接口名(信号)

logic [1:0] grant, request;//定义接口中的logic变量

logic rst;

endinterface

module arb (

arb_if arbif

);//把module中的信号列表用接口名替代

always @(posedge arbif.clk or negedge arbif.rst)//直接用接口名+.接口信号名

begin

if(arbif.rst)

arbif.grant<=2'b00;

else

arbif.grant<=next_grant;

end

endmodule

//*****************************

//tb

//*****************************

module test(arb_if arbif)

initial begin

@(posedge arbif.clk) arbif.request<=2'b01;

$display("@%0t: drove req=01", $time);

repeat(2) @(posedge arbif.clk);

if (arbif.grant !=2'b01) $display("@%0t: a1: grant !=2'b01",$time);

$finish;

end

endmodule :test

//*****************************

//顶层

//*****************************

module top;

bit clk;

always #5 clk=~clk;

arb_if arbif(clk);//例化接口

arb a1 (arbif);//例化arb,接口作为参数传递到arb

test t1(arbif);//例化test,接口作为参数传递到tb

endmodule:top

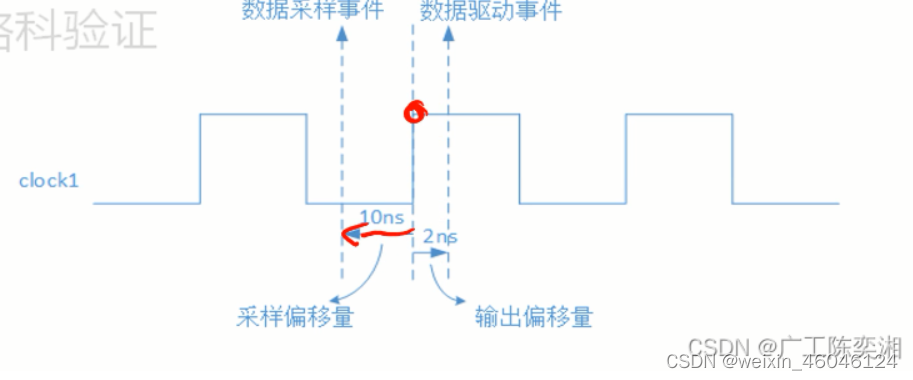

接口中的clocking时钟块

在接口中声明时序块clocking和采样的时钟信号,用来做信号的同步和采样

clocking基于时钟周期对信号驱动和采样,tb不再苦恼于如何准确及时地对信号驱动或采样

clocking bus @(posedge clk1);//定义时钟块bus,在clk1上升沿来驱动和采样

default input #10ns output #2ns;//默认情况下,在每个clk1上升沿前10ns采样,在事件后2ns进行输出驱动

input data, ready, enable;//声明bus要采样的三个输入信号,

output negedge ack;//要驱动ack,驱动的事件是clk1的下降沿后2ns

input #1step addr;//step理解为时间片,在clk1上升沿的上一个时间片采样区域,在左侧,不是那一时刻,保证采样到的数据是上一个时钟周期的

endclocking

clocking可以定义在接口中,也可以定义在module和program中

列举的信号不是自己定义的,是imp等其他模块定义的

default 定义默认的采样事件,如果没定义,则默认是1step对输入采样,#0输出驱动

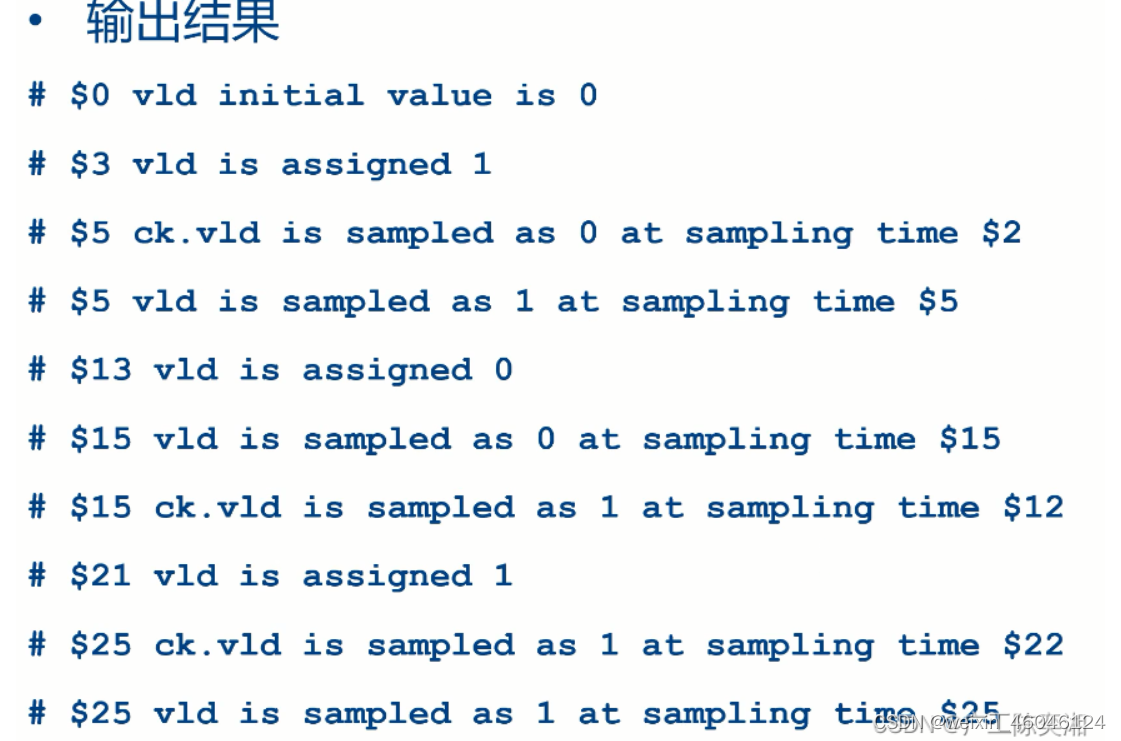

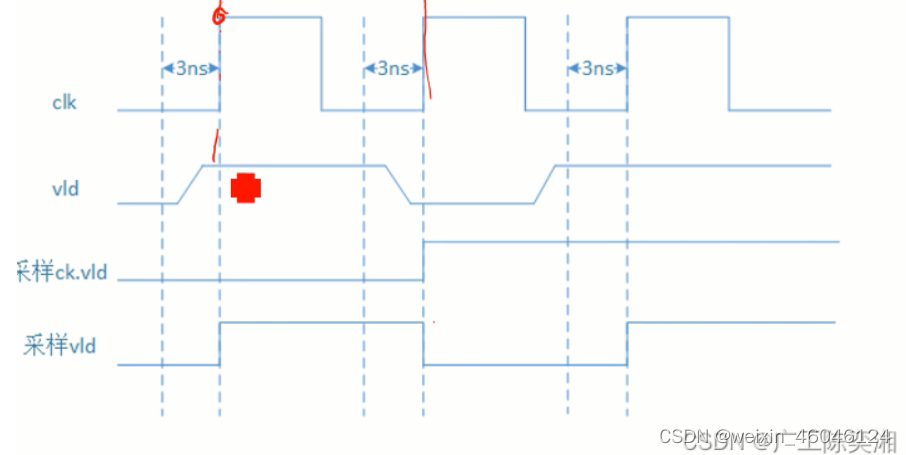

module clocking1;

bit vld;

bit grt;

bit clk;

//定义时钟块ck

clocking ck @(posedge clk);

defailt input #3ns output #3ns;

input vld;output grt;

endclocking

//时钟信号

initial forever #5ns clk<=!clk;

//驱动vld

initial begin: drv_vld

$display("$%0t vld initial value is %d", $time, vld);

#3ns vld=1; $display("$%0t vld is assigned %d", $time, vld);

#10ns vld=0; $display("$%0t vld is assigned %d", $time, vld);

#8ns vld=1; $display("$%0t vld is assigned %d", $time, vld);

end

//采样,initial并行执行

//@ck表示clocking的变化事件,也就是posedge clk

initial forever

@ck $display("$%0t vld is sampled as %d at sampling time $%0t", $time, cld, $time);

@ck $display("$%0t ck.vld is sampled as %d at sampling time $%0t", $time, ck.cld, $time-3);

endmodule

645

645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?